OSPI Flash(Octal SPI Flash)是一種基于SPI(串行外設接口)擴展的高速串行Flash存儲器,采用8-bit數據總線通信方式。相比傳統的SPI或Quad SPI(QSPI),OSPI提供更高的數據吞吐率與更優的系統性能。OSPI Flash主要應用在高性能嵌入式系統啟動,圖形界面處理(GUI)/人機交互界面(HMI),嵌入式AI模型存儲等領域。瑞薩高性能MCU、MPU都提供了功能強大的OSPI接口,它不僅可以工作在8線的高速模式下,還兼容普通的單線(SPI),雙線(DSPI)和四線(QSPI)的多種工作模式和多種協議模式。

然而面對廣大不同廠家的OSPI Flash,雖然說大部分功能相似,大部分功能也可以復用,但是不同廠家的OSPI Flash還是存在或多或少的差別。因此如果客戶出于成本的考慮,需要更換OSPI Flash的時候,需要做驅動層的適配工作。那如何做OSPI Flash的驅動的適配工作?

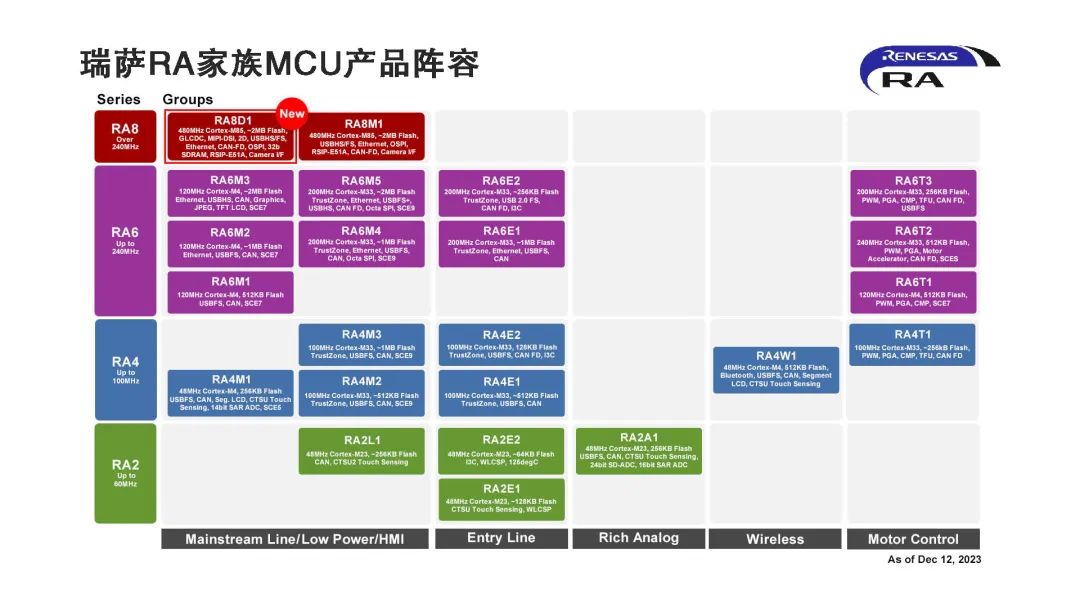

下面我以Renesas RA8D1這款高性能MCU為例來說明如何進行OSPI Flash驅動的適配工作,總結成兩篇適配秘籍,可以供客戶參考。公欲善其事,必先懂其基(基本原理),本篇文章先就OSPI的一些工作模式和協議等基本概念做一個相對系統的介紹。后續的篇章我們將以Winbond W35T51NW OSPI Flash為例來展開具體的驅動的適配工作。請感興趣的讀者持續關注!

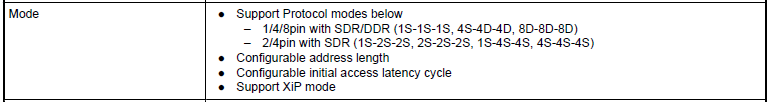

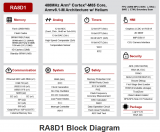

讀者朋友們可以先了解一下RA8D1的OSPI specifications:

RA8D1的OSPI工作模式:

點擊查看大圖

1Support Protocol modes below

xSPI規范支持多種協議模式,包括1S-1S-1S、4S-4D-4D、8D-8D-8D、1S-2S-2S、2S-2S-2S、1S-4S-4S、4S-4S-4S等。這些模式主要是基于數據傳輸位寬(線數)和時鐘模式(SDR/DDR)進行區分。

1協議模式的基本概念

1S、2S、4S、4D、8D代表了數據傳輸過程中使用的線數:

○1S(Single Line,單線):每個時鐘周期傳輸1bit數據。

○2S(Dual Line,雙線):每個時鐘周期傳輸2bit數據(雙線,每根線1bit)。

○4S(Quad Line,四線):每個時鐘周期傳輸4bit數據(四線,每根線1bit)。

○4D(Qcta Line,四線DDR):每個時鐘周期傳輸8bit數據,因為采用DDR(DDR雙數據速率)模式,時鐘周期的上升沿傳輸4bit數據,下降沿傳輸4bit數據。

○8D(Octa Line,八線DDR):每個時鐘周期傳輸16bit數據,因為采用DDR(DDR雙數據速率)模式,時鐘周期的上升沿傳輸8bit數據,下降沿傳輸8bit數據。

SDR(Single Data Rate,單數據速率)DDR(Double Data Rate,雙數據速率):

○SDR:僅在時鐘上升沿傳輸數據。

○DDR:在時鐘上升沿和下降沿傳輸數據,線數相同的情況下吞吐量是SDR的2倍。

2具體模式說明

不同模式的主要區別在于xSPI接口訪問Flash的地址、命令和數據階段分別使用多少條數據線進行傳輸。

| 模式 | 命令階段 | 地址階段 | 數據階段 | 時鐘模式 |

| 1S-1S-1S | 1-bit | 1-bit | 1-bit | SDR |

| 4S-4D-4D | 4-bit | DDR4-bit | DDR4-bit | DDR |

| 8D-8D-8D | DDR8-bit | DDR8-bit | DDR8-bit | DDR |

| 1S-2S-2S | 1-bit | 2-bit | 2-bit | SDR |

| 2S-2S-2S | 2-bit | 2-bit | 2-bit | SDR |

| 1S-4S-4S | 1-bit | 4-bit | 4-bit | SDR |

| 4S-4S-4S | 4-bit | 4-bit | 4-bit | SDR |

下面以1S-1S-1S、4S-4D-4D、8D-8D-8D三種協議模式舉例說明

1S-1S-1S(傳統SPI模式)

○命令、地址、數據階段都使用單線傳輸(每個時鐘周期1bit)。

○ 這種模式兼容傳統SPI,但傳輸速度較慢。

○優點:兼容性好,適用于低速SPI設備。

4S-4D-4D(Quad SPI DDR模式)

○命令階段:使用4-bit傳輸(相比1S提高4倍)。

○地址階段:使用4-bitDDR傳輸(時鐘上升沿和下降沿都發送數據)。

○數據階段:使用4-bitDDR傳輸,吞吐量更高。

○優點:相比1S-1S-1S,吞吐量提高了8倍,適用于高速NORFlash存儲應用。

8D-8D-8D(Octa SPI DDR模式)

○命令、地址、數據都使用8-bitDDR傳輸。

○ 相比4S-4D-4D,吞吐量翻倍。

○ 適用于極高速NORFlash存儲,如PSRAM、Octa Flash、Octa HyperRAM。

2Configurable address length

支持可配置的地址長度(常見如24-bit或32-bit地址模式):

24-bit通常用于小于16MB(128Mbit)的Flash;

32-bit用于更大容量的Flash(>16MB);

3Configurable initial access latency cycle

指訪問延遲周期(Latency Cycle)可配置,在XIP或連續讀取模式中尤為關鍵:

設備允許設置dummy cycle數量;

適應不同主頻、控制器時序要求;

優化帶寬性能或兼容性。

4Support XiP mode

支持Execute in Place(XIP)模式:

MCU/MPU可將Flash映射入內部地址空間;

支持直接讀取并執行,不需復制到RAM;

通常與memory-mapped mode、持續讀取命令組合使用。

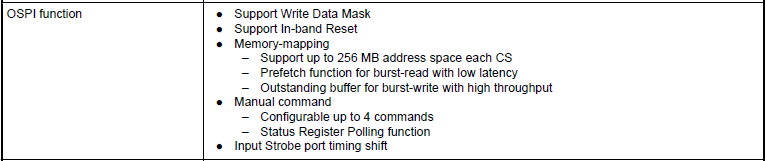

RA8D1的OSPI接口功能:

點擊查看大圖

1Support Write Data Mask(支持寫數據掩碼)

允許在寫入數據時屏蔽某些字節,使其不被改寫,而其他字節仍然可以被正常寫入。

這種功能通常用于按位更新存儲器內容,而無需先讀取、修改、再寫入完整數據。

2Support In-band Reset(支持帶內復位)

通過OSPI總線上的指令或數據序列觸發設備復位,而不是依賴額外的硬件復位引腳。

○ 適用于系統集成度高、不易接觸硬件復位引腳的應用,如嵌入式系統和工業控制設備。

3Memory-mapping(內存映射模式)

OSPI控制器支持將外部Flash設備的存儲空間直接映射到MCU地址空間,使其像內部RAM/ROM一樣被訪問。

1Support up to 256MB address space each CS

(每個CS支持高達256MB的地址空間)

在內存映射模式下,每個片選(CS,Chip Select)可支持高達256MB的存儲空間,這意味著可以使用較大的外部存儲器。

應用場景:

○ 適用于大容量代碼存儲(如執行XIP(execute In Place)),即代碼直接在Flash中運行,而無需拷貝到RAM。

○ 適用于存儲大量數據,如日志記錄、固件存儲、AI推理模型等。

2Prefetch function for burst-read with

low latency(預取功能,提高突發讀取性能)

在突發讀取(BurstRead)模式下,OSPI控制器會提前讀取后續數據并存入緩沖區,減少訪問延遲。

應用場景:

○ 適用于實時性要求較高的應用,例如高速圖像處理、實時操作系統(RTOS)等。

○XIP模式下,可以減少CPU訪問外部Flash的延遲,提高程序運行效率。

3Outstanding buffer for burst-write with

high throughput(突發寫入優化,提高吞吐量)

突發寫入(BurstWrite)時,OSPI控制器使用Outstanding buffer(寫入緩沖區),允許CPU快速提交數據,而不必等待Flash完成寫入,提高吞吐量。

應用場景:

○ 適用于數據流量較大的應用,如數據記錄、固件升級、機器學習模型加載等。

4Manual command(手動指令模式)

OSPI支持手動發送自定義指令,使其適用于不同廠商的Flash設備,并提供更靈活的操作方式。

1Configurable up to 4 commands

(可配置最多4條指令)

用戶可以預設4條常用指令(如讀、寫、擦除等),減少軟件控制開銷,提高效率。

2Status Register Polling function

(狀態寄存器輪詢功能)

允許MCU輪詢Flash的狀態寄存器,以確定Flash是否完成寫入、擦除等操作,避免不必要的等待。

5Input Strobe port timing shift

在高速OSPI傳輸中,數據可能會有時序偏移。這個功能允許調整數據采樣時鐘,以確保數據穩定可靠。

應用場景:

○ 當使用不同的Flash器件時,可能會因工藝或PCB布局導致時序誤差,調整該參數可以優化信號完整性。

○ 適用于高速通信場景,如工業自動化、汽車電子、無線通信設備等。

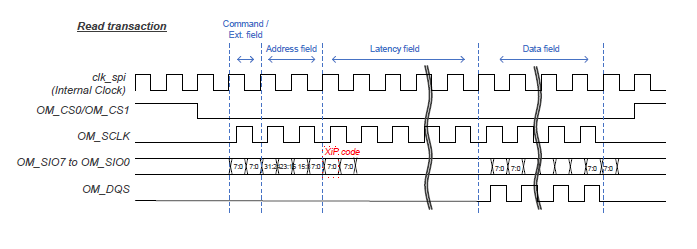

下面具體給讀者解讀一下在8D-8D-8D協議下的時序圖:

點擊查看大圖

圖中相關信號線的含義如下表所示:

| 信號 | 含義 | 說明 |

| clk_spi(Internal Clock) | 控制器內部工作時鐘 | 控制器使用的內部時鐘,驅動SPI狀態機,不直接輸出 |

| OM_CS0/CS1 | 片選信號 | 有效為低,表示與Flash通信開始 |

| OM_SCLK | 外部SPI時鐘 | 控制器發出的時鐘信號,Flash據此采樣或發送數據 |

| OM_SIO[7:0] | Octal IO數據線 | 8位數據總線,雙向通信(收發命令/地址/數據) |

| OM_DQS | 數據選通信號 | DDR模式下Flash輸出的時鐘對齊信號,用于控制器采樣數據 |

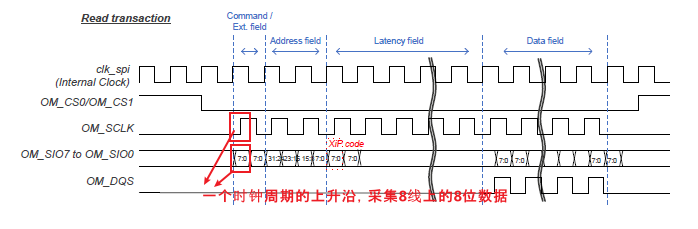

點擊查看大圖

從上圖可以看到command field的一個時鐘周期的上升沿可以采集8位數據(因為有OM_SIO0-OM_SIO7八根線的數據,每根線上一位數據),下降沿也可以采集8位數據,這樣一個時鐘周期可以采集16bit的數據。同樣的道理地址段兩個時鐘周期,可以采集32位數據。那么這樣數據段的傳輸速率,相比1S-1S-1S協議提高了16倍。

關于OSPI Flash適配的內功心法就大致介紹完畢。我們將在下一個篇章推出具體的Octa Flash適配的移形換位大法。請感興趣的讀者,持續關注我們的#瑞薩嵌入式小百科公眾號。

-

mcu

+關注

關注

146文章

17981瀏覽量

366821 -

嵌入式

+關注

關注

5152文章

19670瀏覽量

317518 -

FlaSh

+關注

關注

10文章

1679瀏覽量

151807 -

存儲器

+關注

關注

38文章

7651瀏覽量

167379 -

瑞薩

+關注

關注

36文章

22383瀏覽量

88040

原文標題:OSPI Flash適配秘籍之內功心法篇

文章出處:【微信號:瑞薩MCU小百科,微信公眾號:瑞薩MCU小百科】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

瑞薩RA8D1 CEU介紹與使用說明

【Vision Board創客營連載體驗】RA8D1 Vision Board初體驗

【瑞薩RA8D1 CPK開發板試用】開箱與點燈

新品發布 | 瑞薩推出面向圖形顯示應用和語音/視覺多模態AI應用的全新RA8 MCU產品群

邊緣計算分論壇動手實踐指南,RA8D1 OpenMV 硬件全球首發!

瑞薩RA8系列教程 | 基于 Keil 開發 RA8單片機

瑞薩RA8D1 MCU的OSPI Flash適配指南

瑞薩RA8D1 MCU的OSPI Flash適配指南

評論