開源FPGA項目自發布以來,得到了眾多開發者的關注,涉及工業、通信、車載等多個行業的100+位工程師報名參與設計,并分為:硬件組、FPGA組、Linux組,其中硬件組率先開始啟動項目。經過和所有報名硬件組的工程師溝通,最終確定由ID號:閑云(肖工)擔任原理圖主導設計工程師,負責主板硬件設計;ID號:恒水一(郝工)擔任Layout主導設計工程師,負責主板Layout設計。

經過一周的設計,閑云(肖工)完成了第一版本原理圖,今晚20:00(7月16日)審核原理圖啦,誠邀大家一起加入!原理圖審核完成以后,我們將開始設計PCB!騰訊會議掃一掃加入我們哦!

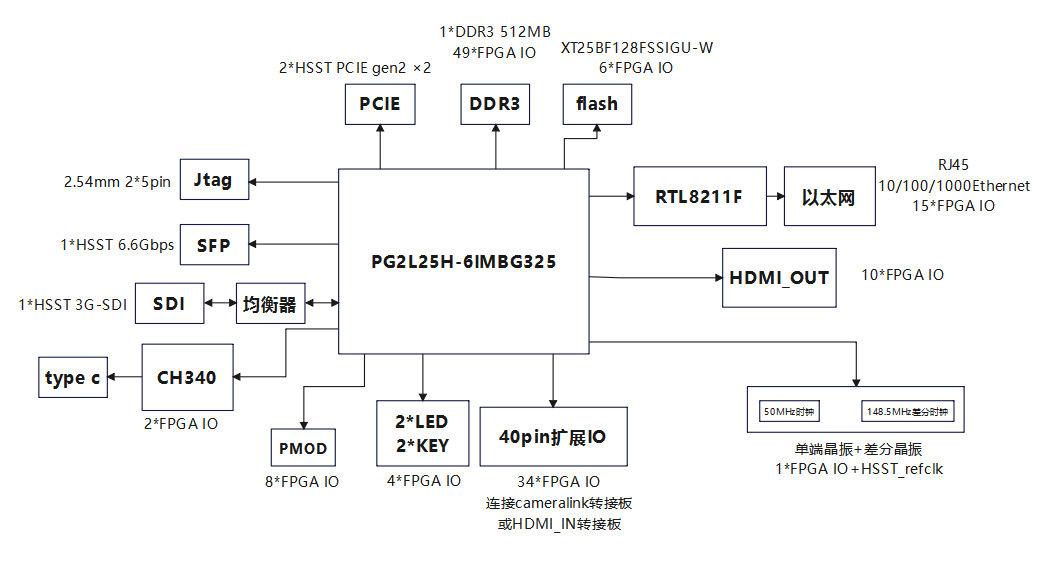

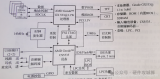

硬件框圖

* 7月6日,相關硬件人員進行了會議討論,最終確定硬件方案確定如下:

1. 電源:外部電源輸入采用電源適配器輸入,使用電源芯片為FPGA各電源管腳提供對應的電源,并為外設器件供電,電源方案采用矽力杰SQ20953和SQ28704;

2.晶振:單端晶振及HSST差分晶振;

3. DDR3:1顆4Gbit(512MB)的DDR3芯片,DDR3型號采用芯存XCCC256M16EP-EINAY;

4. Flash:采用XT25BF128FSSIGU-W用于存儲位流文件;

5.HDMI_OUT:FPGA差分管腳連接HDMI輸出接口;

7.SFP光口:1個SFP光纖接口,最高速率支持6.6Gbps

8.PCIE接口:PCIE gen2 x2;

9. 以太網:實現10/100/1000M Ethernet;

10.SDI接口:預留1路SDI接口,SDI均衡器采用LMH0344和LMH0302;

11.JTAG:預留jtag調試接口,標準2.54mm 2*5pin;

12.LED/按鍵:預留用戶按鍵及用戶LED(數量根據可用管腳數量調整);

13.PMOD:預留1路PMOD接口(根據可用管腳數量調整);

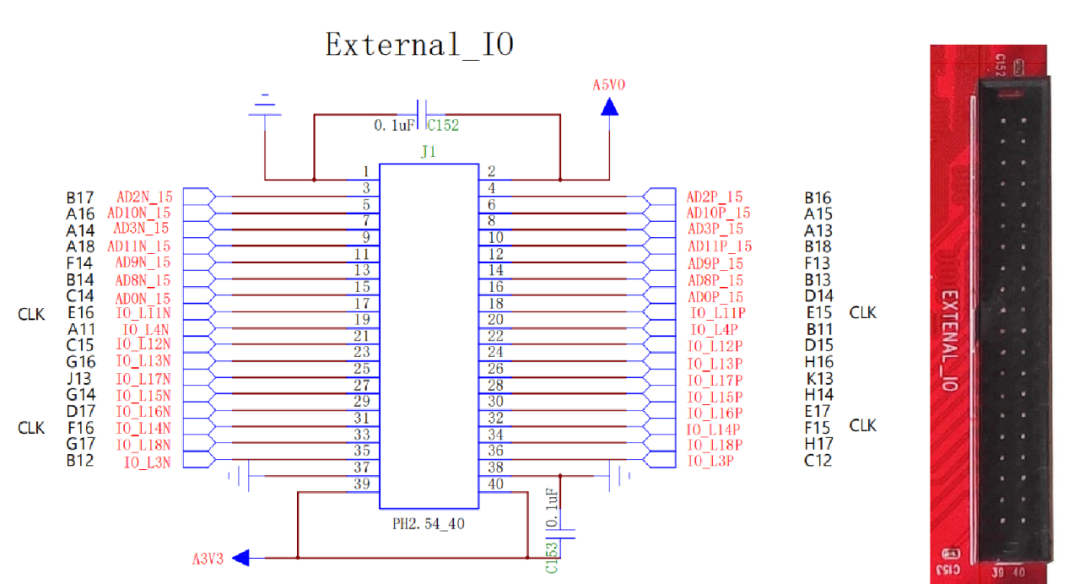

14.40pin擴展IO接口:擴展1路標準PMOD接口,并設計camera link(base)及HDMI_IN轉接板,2.54mm 40pin擴展IO接口線序定義參考如下:

* 注:40pin擴展IO選用FPGA差分IO,且在對應管腳序號支持兩對差分始終輸入至FPGA的全局時鐘管腳,使板卡接口適配更多擴展模塊。

硬件設計會議回放及參考資料

開源FPGA開發板硬件討論會議回放請在B站搜UP主:小眼睛半導體觀看!or 如下鏈接:

【開源FPGA開發板活動硬件設計討論會(1)】 https://www.bilibili.com/video/BV1GPGpzAENa/?share_source=copy_web&vd_source=e8e422b1d803952d319bad4c486c7160

開源項目參考資料

鏈接: https://pan.baidu.com/s/1pLU8O65bGMeo24zKUUrtYg提取碼: rtd3

項目發起人

配套參考教材

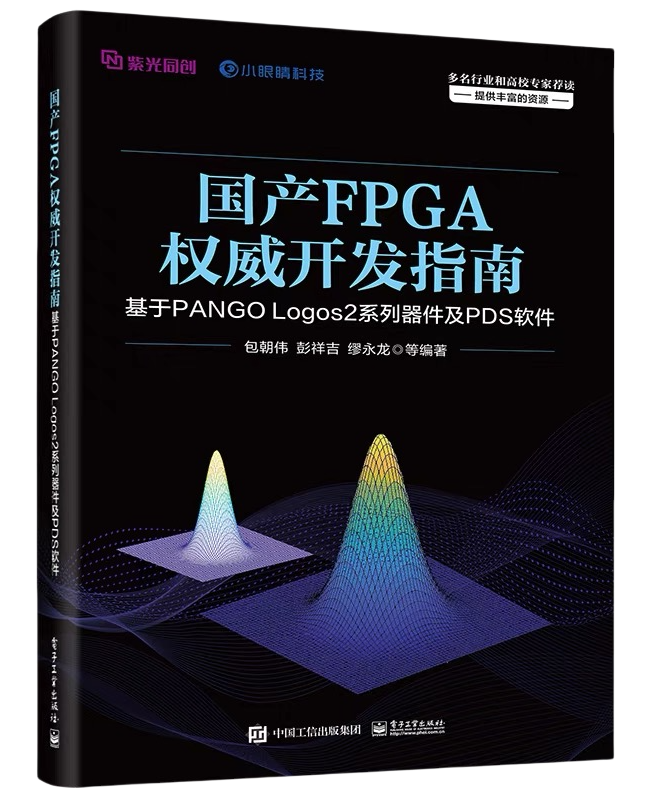

由項目發起人Mill(米爾)和紫光同創原廠技術專家共同編寫的教材《國產FPGA權威開發指南》作為參考。該書不僅從宏觀市場角度分析整個FPGA市場及發展,并從硬件架構原理及軟件使用方法多個層面闡述FPGA開發的各個方面,并以紫光同創FPGA的器件特性作為分析案列,深入淺出講解FPGA技術及原理,并在第八章收錄了各個領域FPGA應用方案及具體問題解決方法。全書理論實踐相結合,具有極高的理論指導及實戰意義,可用于高校理論教學的工具書,亦可用于企業FPGA開發指導。

-

FPGA

+關注

關注

1645文章

22049瀏覽量

618347 -

開源

+關注

關注

3文章

3688瀏覽量

43822

發布評論請先 登錄

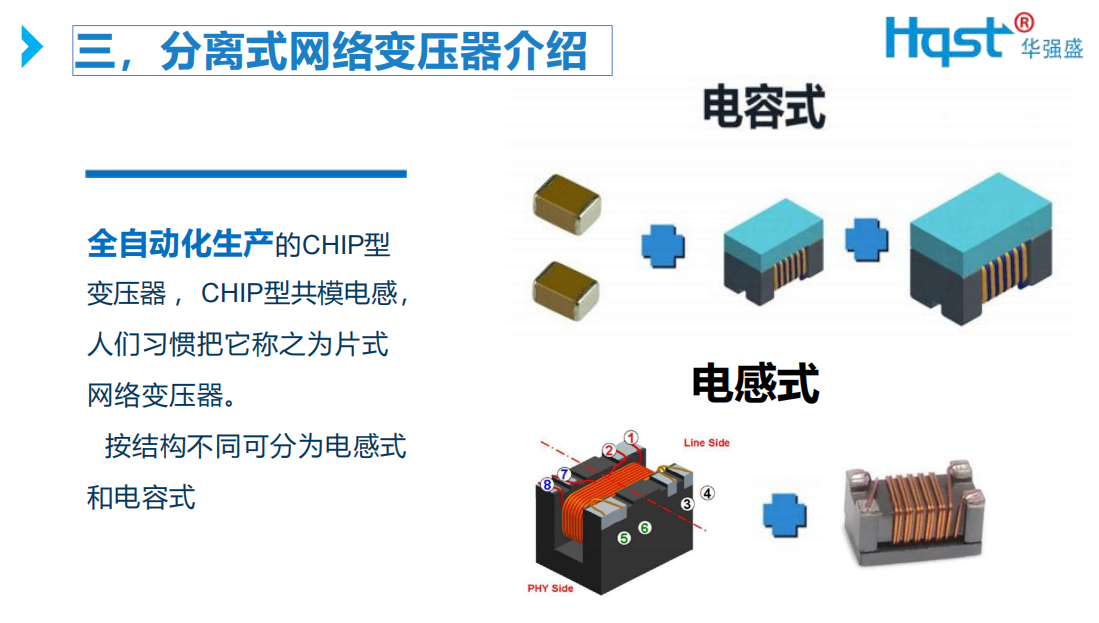

如何用電容式的片式 CHIP LAN 網絡變壓器(電感)來替代消費級傳統網絡變壓器,電氣原理圖是怎樣的?

火爆開發中 | 開源FPGA硬件板卡,硬件第一期發布

火爆開發中|開源FPGA硬件板卡,硬件第一期發布

【開源分享】:開源小巧的FPGA開發板——Icepi Zero

擁抱開源!一起來做FPGA開發板啦!

開源啦!!!基于鴻蒙ArkTS封裝的圖表組件《McCharts》,大家快來一起共創

用THS3091來做功率級放大,在運放的帶寬內放大倍數平坦度怎么樣?

AD20原理圖跟PCB怎么交互

選2088還是3051?一起來說說TA們的不同~

開源FPGA硬件|大家一起來“找茬”!就在今晚20:00,原理圖公開審核

開源FPGA硬件|大家一起來“找茬”!就在今晚20:00,原理圖公開審核

評論