設計目標:

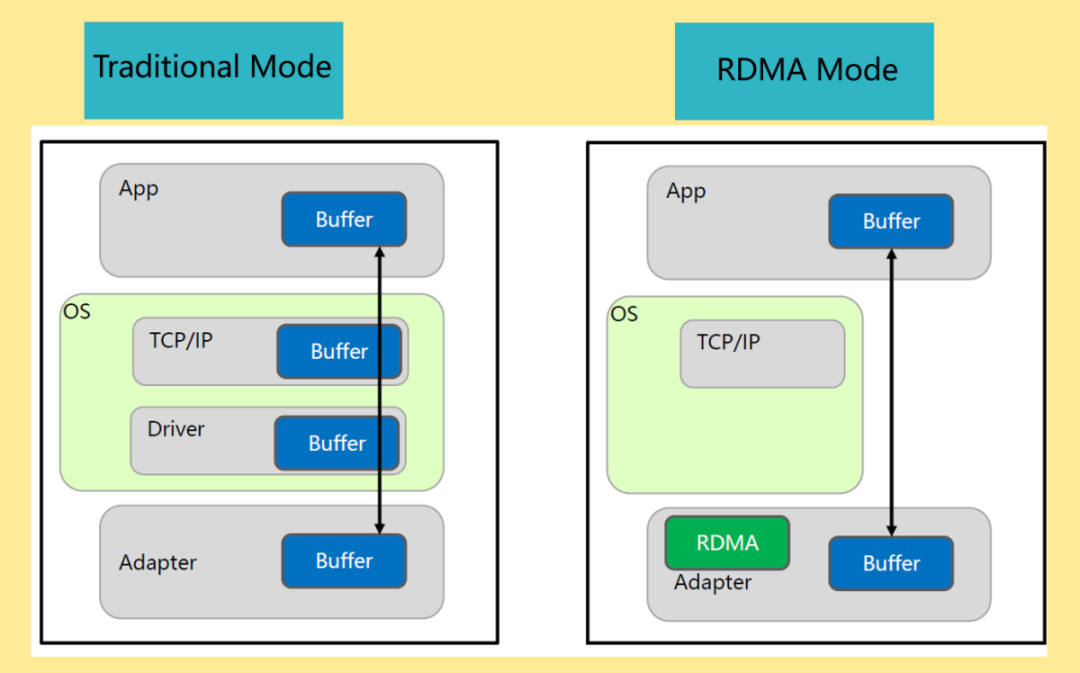

RDMA技術采用無感傳輸機制,消除傳統網絡傳輸中需要CPU介入下的多重數據復制與內核參與環節,實現直接跨主機內存訪問的機制。其設計目標為優化分布式環境下的數據傳輸效率,降低CPU負載。

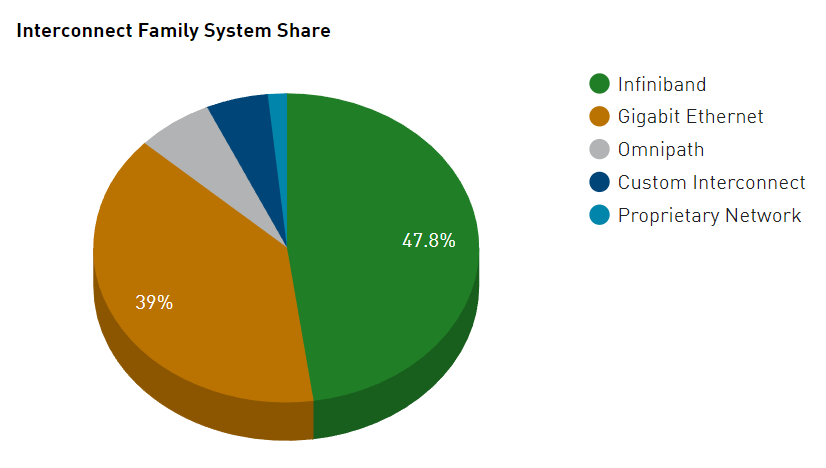

RoCEv2基于標準網絡的以太網、網絡層和傳輸層(UDP)協議,這可以使得RoCEv2的網絡流量可以經過傳統的網絡路由器路由。之前RDMA簡介1~8有對相關資料介紹,這里強調的是:它是目前性價比最高的RDMA實現方式,雖然IB模式在一些高校應用較多,但因為它的專有特性,價格較貴,難廣泛用于產品中。

設計思考

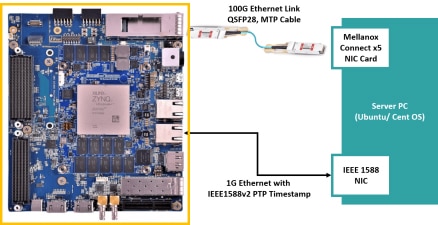

基于PC-PC或GPU-GPU之間RDMA設計已有較多廠商投入,雖然有的大廠投入幾年后折羽而歸,但不影響PC領域成熟應用產品的推廣。這里主要討論在FPGA上設計RDMA over RoCE V2,雖然已有xilinx的ernic應用,但是性價比以及國產化需求還是有其發展空間。這里討論設計需要著重考慮地方:

1)通用性

一般項目中的數據采集前端基于 FPGA 進行開發。第一,各數據采集前端使用的 FPGA型號各不相同,需要實現的設計能夠工作在多種不同型號 FPGA 上;第二,為了降低設計部署成本,需要實現的設計能夠在脫離 CPU 控制下獨立運行和控制傳輸;第三,一些廠商不愿意采用私有化協議,主要是考慮其被迫被捆綁,私有協議也就意味著難以與其他系統兼容,一旦存在功能或性能設計不足,只能前功盡棄。考慮到以上三點需求,設計時建議采用純邏輯電路實現。

2)高性能

數據采集前端得到的數據,數據塊大小不固定、數據速率也不盡相同。同時對于數據傳輸的需求也并不相同,存在一對一、一對多、多對多等多種傳輸情況。面對大量離散數據時,需要增加 RDMA 隊列數量及深度,同時靈活調整數據包大小來保證傳輸性能,而面對大量連續數據請求時,則可通過減少隊列數量的方式來降低功耗。

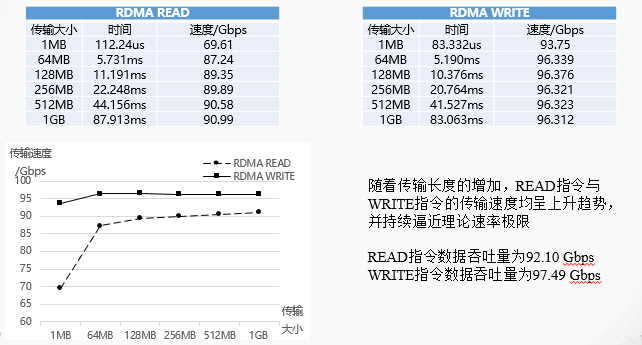

同時,在面對一對多或多對多傳輸需求時,則要求設計能夠正確地處理網絡擁塞情況并正確地進行流量控制。因此,需要實現完備的隊列管理及擁塞處理功能,在滿足性能要求的同時適應不同的應用環境。具體要求為使用 QSFP28 及以上光纖接口,在傳輸不小于 256 MB 的連續數據時,數據傳輸速率不小于 90 Gbps。在傳輸包大小為 4KB 時,延遲不高于 10 μs、包吞吐量不小于 1000 kpps。這里也只是簡要指標分析,上面這些指標在PC-FPGA之間實現較容易,在FPGA-FPGA之間還是有一些挑戰。這也反映競爭環境下適者生存,最后生存的不大可能是大多數。雖然我們設計的IP性能(包括我們A, FPGA-FPGA)早已超越這些指標,相信其他廠家也能滿足。

3)易集成、用戶操作簡便

實現的 RDMA 協議棧和控制邏輯,應能夠簡易地集成到應用生產環境中,并提供簡易的用戶操作方式來實現數據傳輸控制及隊列控制。因此,設計需要使用標準化接口,同時盡可能地降低資源占用率,并具備 DMA 數據傳輸功能。

4)穩定性

這里強調的是,如果只是預研項目,就不大需要考慮穩定性,其特有的功能和性能才是項目需要重點解決的。但是作為商用IP,就需要考慮其穩定性,不能出現上次可以,這次就工作不正常,或者性能下降明顯情況。

它涉及到?幾個因素:

1)高速接口的匹配性?:RDMA數傳通道一般采用AXI總線,它需確保IP核與FPGA的如AXI4-Stream/AXI4-Lite等兼容性,避免因協議不匹配導致傳輸錯誤; ?

2)?時序優化:一般它需要跨時鐘域設計,因此對時鐘同步、信號路徑規劃和資源分配等關鍵因素需要重點考慮;

3)?存儲資源分配?:合理設計FIFO深度,(一般采用2的整數次冪深度設計)和RAM塊數量,避免因資源不足導致數據丟失或性能下降。 ?

這里給出IP讀寫性能情況:

B站已給出相關性能的視頻,如想進一步了解,請搜索B站用戶:專注與守望

鏈接:https://space.bilibili.com/585132944/dynamic?spm_id_from=333.1365.list.card_title.click

審核編輯 黃宇

-

FPGA

+關注

關注

1645文章

22041瀏覽量

618226 -

高速傳輸

+關注

關注

0文章

29瀏覽量

9170 -

RDMA

+關注

關注

0文章

85瀏覽量

9289

發布評論請先 登錄

RDMA over RoCE V2設計2:ip 整體框架設計考慮

RDMA over RoCE V2設計1:通用,穩定及高性能!

RDMA簡介7之可靠傳輸

RDMA簡介6之RoCEV2連接管理

RDMA簡介5之RoCE V2隊列分析

RDMA簡介4之ROcE V2初析

RDMA簡介3之四種子協議對比

RDMA簡介2之A技術優勢分析

RDMA簡介1之RDMA開發必要性

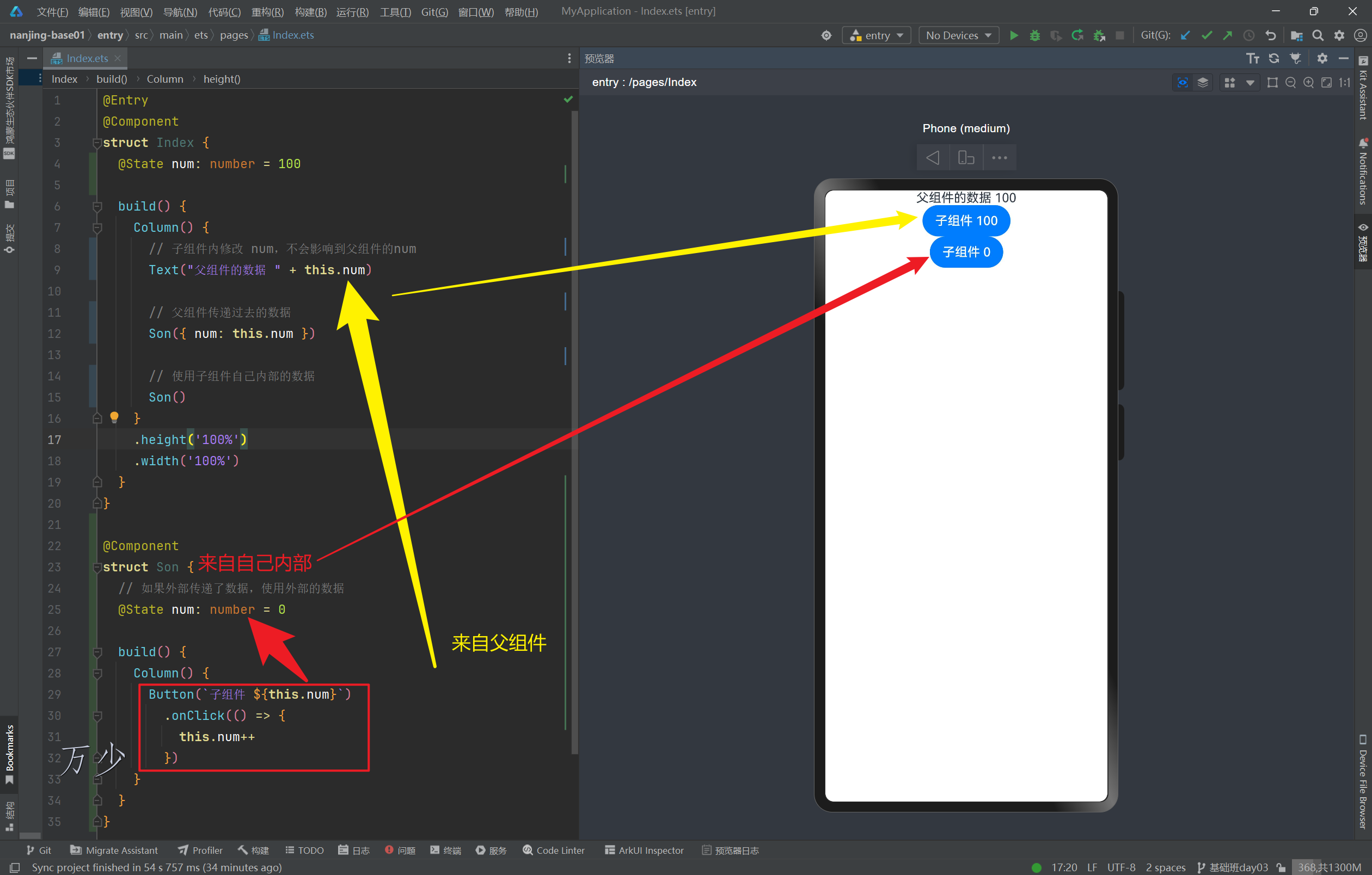

HarmonyOS Next V2 @Local 和@Param

HarmonyOS Next V2 @Monitor 和@Computed

加速網絡性能:融合以太網 RDMA (RoCE) 的影響

RoCE與IB對比分析(一):協議棧層級篇

RDMA over RoCE V2設計1:為什么要設計它?

RDMA over RoCE V2設計1:為什么要設計它?

評論