TJ375已經(jīng)支持PLL的動態(tài)配置。打開PLL在Advance Settings中的Dynamic Reconfiguration中勾選Enable就可以了。最大可以支持85組配置參數(shù)。動態(tài)配置框圖如下:

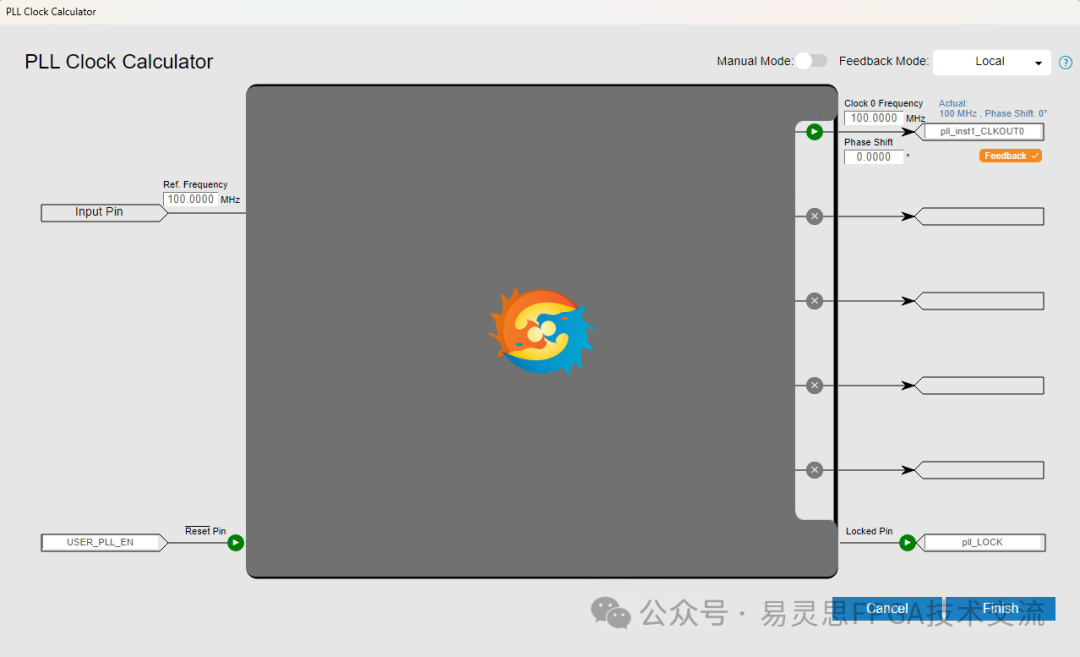

(1)在interface中打開動態(tài)配置功能

使用PLL動態(tài)配置功能需要打開PLL的reset和lock信號,

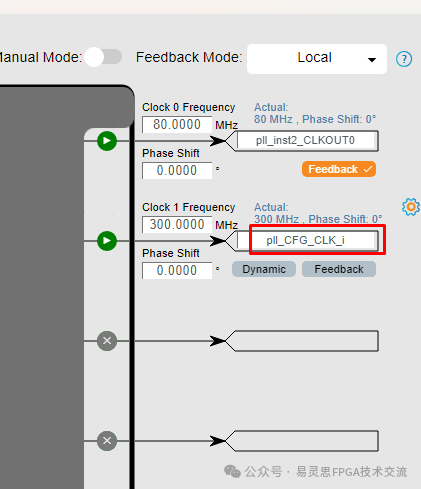

需要兩個時鐘,pll_cfg_clk_i 和 pll_cfg_clk, pll_cfg_clk_i是一個輸入時鐘,pll_cfg_clk是動態(tài)配置的輸出時鐘,

通過另一個PLL產(chǎn)生一個pll_CFG_CLK_i

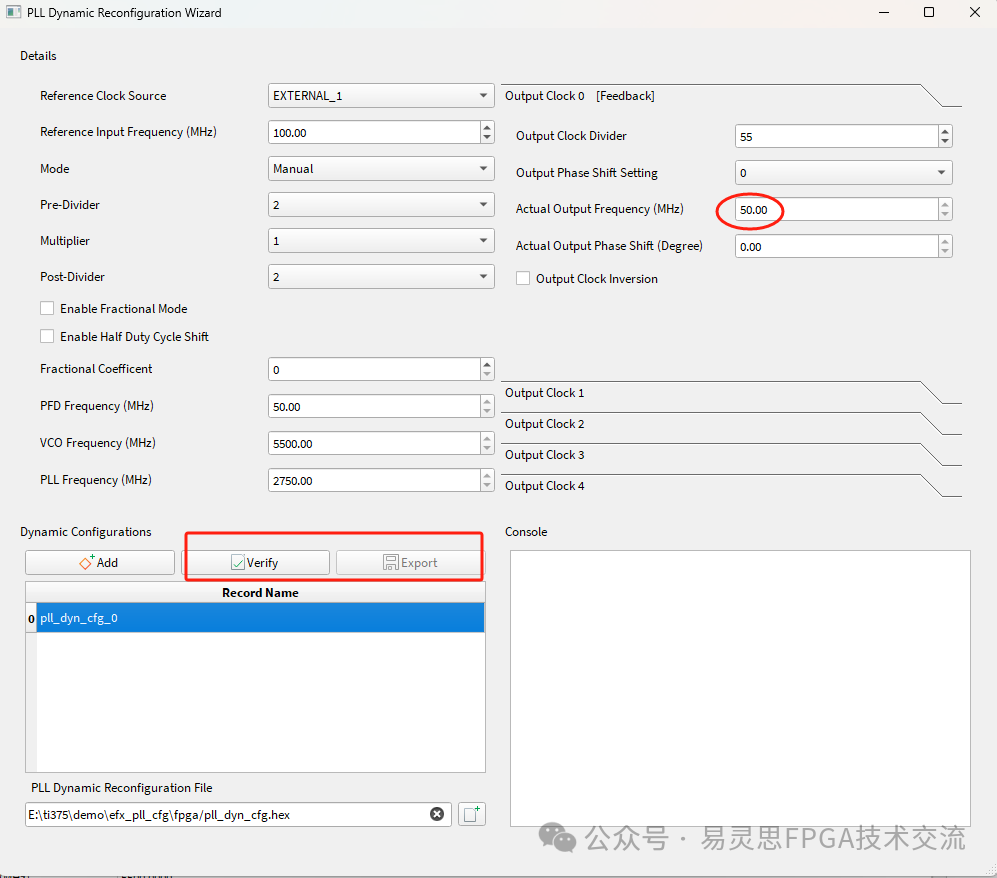

在生成動態(tài)配置IP之前要先配置PLL的hex

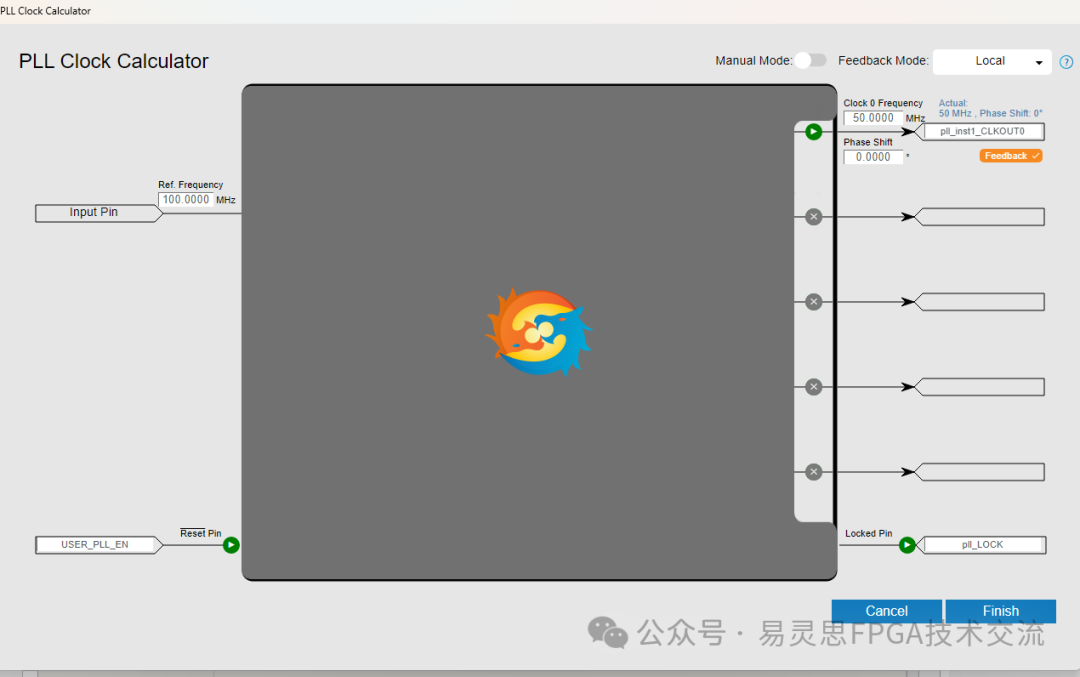

step1:把PLL配置成50M

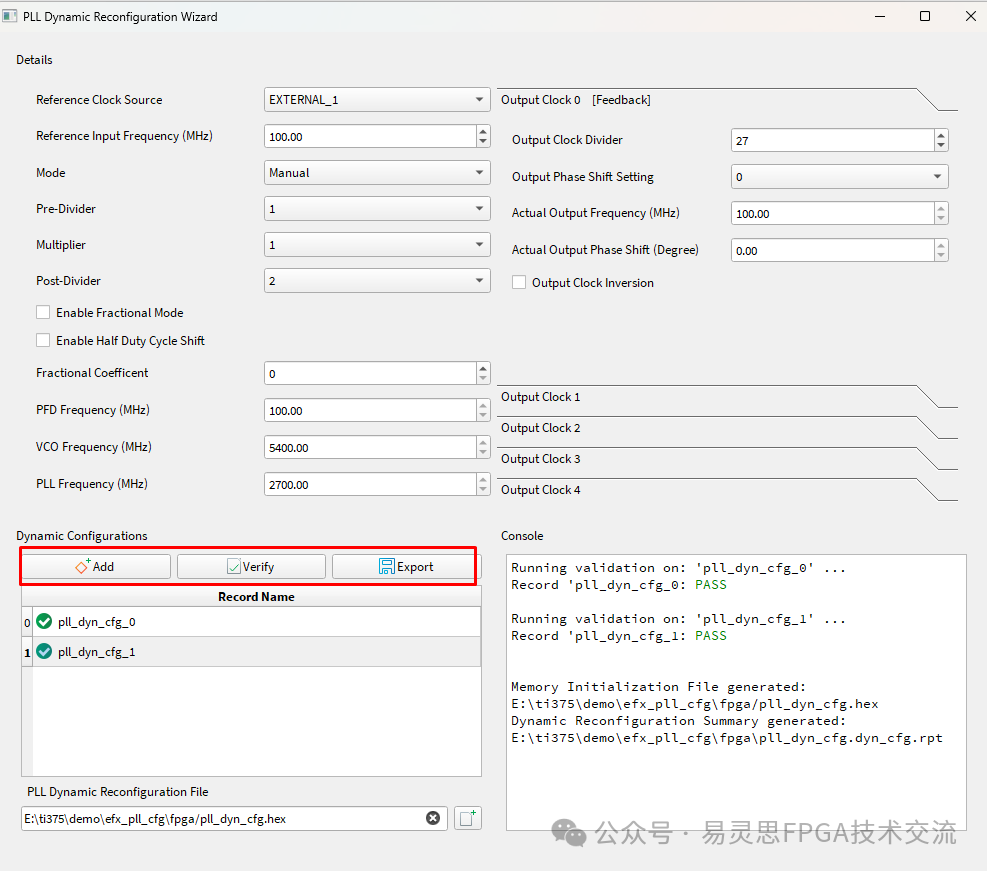

(2)添加配置參數(shù)。點擊 Reconfiguration Wizard就可以看到該組參數(shù)的配置,點擊verify確認參數(shù)是否正常;再點擊Export生成相應的參數(shù)到hex文件;

把PLL的輸出修改成100M輸出。

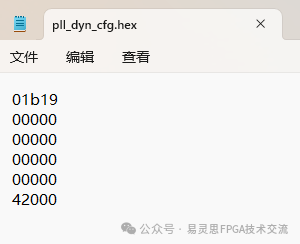

再次點擊 Reconfiguration Wizard就可以看到該組參數(shù)的配置,點擊verify確認參數(shù)是否正常;再點擊Export生成相應的參數(shù)到hex文件;

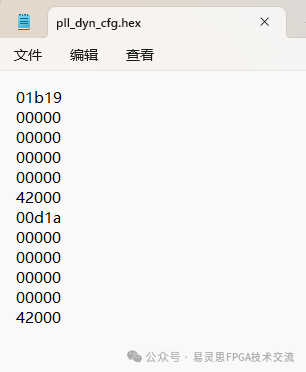

從生成的hex文件可以看到數(shù)據(jù)有所增加,說明有兩個組配置參數(shù)。

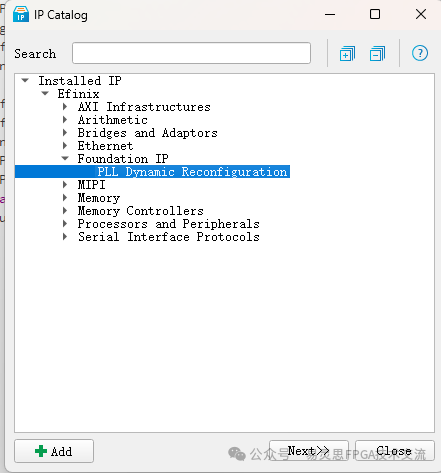

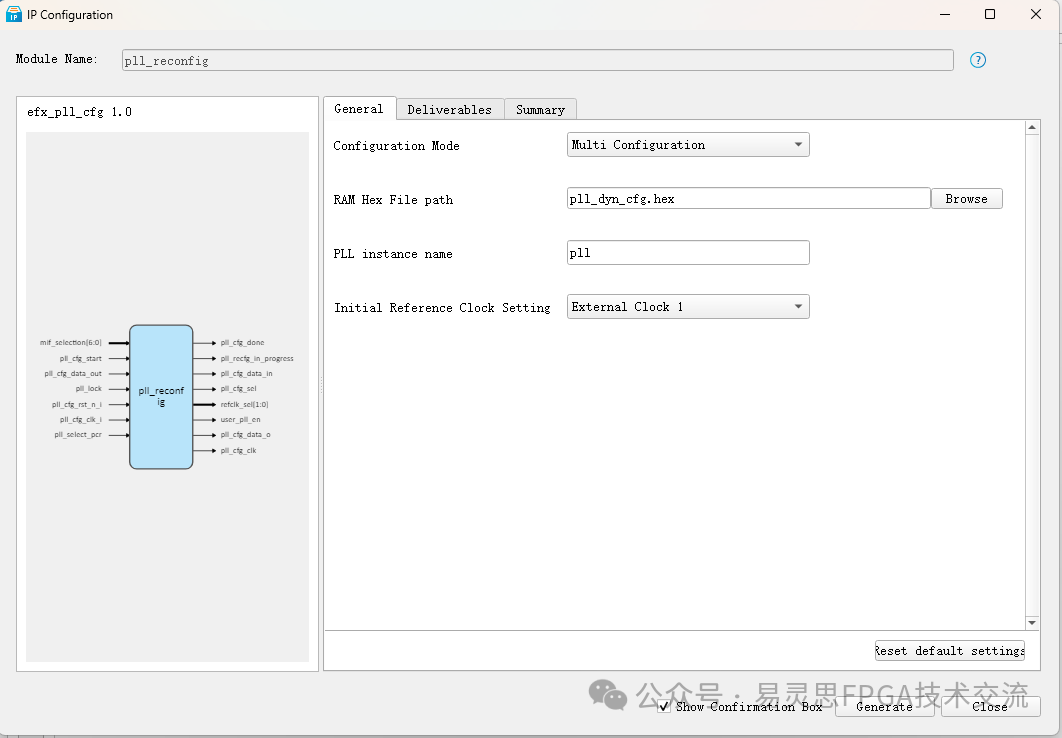

(3)添加IP.在interface里面設(shè)置完成之后就可以添加IP了

RAM Hex file path就是之前生成的hex文件的路徑;

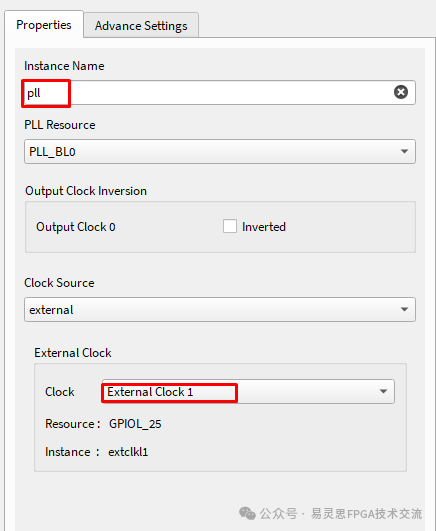

PLL instance name就是我們在interface中例化的PLL的名字;

Initial Reference clock Setting :PLL的參考時鐘的源,要對于interface中例化的PLL的參考源。再來看下PLL的配置就更清楚了。

IP 端口說明

| port | I/O | clock Domain | |

| user_pll_en | O | 連接PLL的復位信號 | |

| pll_cfg_clk | O | 動態(tài)配置時鐘,要與interface內(nèi)部輸入的時鐘名一致,25 - 150MHz,應該是pll_cfg_clk_i的二分頻生成時鐘 | |

| pll_cfg_clk_i | I | 50 - 300MHz | |

| pll_cfg_rst_n_i | 復位PLL動態(tài)配置。只有pll_recfg_in_progress為低時才允許斷言。 | ||

| pll_select_pcr | I | pll_cfg_clk_i | 把PLL切回PCR設(shè)置。 |

| pll_cfg_start | I | pll_cfg_clk_i | 拉高該信號啟動PLL動態(tài)配置。實測一個時鐘周期即可。 |

PCR: Peripheral Configuration Register PLL在interface中設(shè)置的初始值 。可以通過把pll_select_pcr拉高來恢復到初始值

-

FPGA

+關(guān)注

關(guān)注

1645文章

22046瀏覽量

618286 -

易靈思

+關(guān)注

關(guān)注

5文章

56瀏覽量

5218

發(fā)布評論請先 登錄

PLL技術(shù)在FPGA中的動態(tài)調(diào)頻與展頻功能應用

易靈思邀您相約2025上海國際汽車工業(yè)展覽會

易靈思2025 FPGA技術(shù)研討會北京站圓滿結(jié)束

基于易靈思國產(chǎn)FPGA Ti60F225 實現(xiàn)6目同步1080P實時成像系統(tǒng)

國產(chǎn)EDA億靈思?接入DeepSeek

賽靈思低溫失效的原因,有沒有別的方法或者一些見解?

易靈思FPGA PS配置模式--v7

config37中根據(jù)DACCLK配置jesd clock,請問下jesd clock大小是跟之前配的serdes pll配置的line rate成40倍關(guān)系的嗎?

易靈思FPGA產(chǎn)品的主要特點

配置和優(yōu)化DAC348x的片內(nèi)PLL

音頻設(shè)備的PLL和時鐘配置應用說明

紫光同創(chuàng)——PLL IP 的使用(Logos2)

MOSFET器件參數(shù):TJ、TA、TC到底講啥

易靈思Trion FPGA PS配置模式--update(6)

易靈思 FPGA TJ375的PLL的動態(tài)配置

易靈思 FPGA TJ375的PLL的動態(tài)配置

評論