將脈沖技術(shù)引入先進(jìn)CMOS技術(shù)的可靠性測(cè)試

在氮化鎵和碳化硅之后,氧化鎵(Ga?O?)正以超高擊穿電壓與低成本潛力,推動(dòng)超寬禁帶功率器件進(jìn)入大規(guī)模落地階段。

但在光伏逆變、電動(dòng)車快充、高壓電源模塊等真實(shí)工作場(chǎng)景中,高頻大電流動(dòng)態(tài)開(kāi)關(guān)才是氧化鎵器件日常面臨的真實(shí)挑戰(zhàn)。如何評(píng)估器件在這些動(dòng)態(tài)應(yīng)力下的可靠性,成為影響產(chǎn)品量產(chǎn)落地與客戶信賴度的關(guān)鍵。

傳統(tǒng)直流老化測(cè)試,難以真實(shí)還原動(dòng)態(tài)負(fù)載場(chǎng)景,也難以準(zhǔn)確捕捉在高κ材料柵結(jié)構(gòu)中電荷捕獲、陷阱演化等動(dòng)態(tài)退化行為。脈沖應(yīng)力與電荷泵技術(shù)的結(jié)合,正成為下一代氧化鎵功率器件可靠性驗(yàn)證的關(guān)鍵抓手。

本篇內(nèi)容將帶您了解為什么在Ga?O?等先進(jìn)CMOS與功率器件的可靠性驗(yàn)證中,需要引入脈沖應(yīng)力技術(shù),以及如何借助泰克平臺(tái)與方法,更真實(shí)模擬器件在實(shí)際工作負(fù)載下的老化過(guò)程,助力從材料到器件到系統(tǒng)的產(chǎn)業(yè)落地驗(yàn)證。

泰克對(duì)話港科大,黃文海教授談超寬禁帶氧化鎵

傳統(tǒng)的直流應(yīng)力與測(cè)量方法廣泛用于表征 CMOS 器件的可靠性,如 HCI 和 TDDB 引起的退化。然而,隨著 PMOSFET 和高κ材料器件中新興電荷捕獲等問(wèn)題出現(xiàn),可靠性測(cè)試也在演進(jìn)。實(shí)際電路中器件動(dòng)態(tài)開(kāi)關(guān)的特性,使得動(dòng)態(tài)可靠性驗(yàn)證需求日益增加,引入脈沖應(yīng)力測(cè)試成為趨勢(shì)。

研究表明,電壓應(yīng)力導(dǎo)致的界面陷阱增加是 HCI、NBTI 等可靠性問(wèn)題的重要原因。將電荷泵技術(shù)引入現(xiàn)有直流測(cè)試,可有效監(jiān)測(cè)界面陷阱,幫助理解高κ材料及先進(jìn) CMOS 工藝中的新型退化機(jī)制。

雖然常用“交流應(yīng)力”表述,但在此場(chǎng)景中實(shí)為重復(fù)方波或梯形脈沖,本文統(tǒng)一稱為“脈沖應(yīng)力”,更準(zhǔn)確反映測(cè)試方式。

脈沖表征 - 電荷泵

電荷泵(CP)和高頻/準(zhǔn)靜態(tài) C-V 是表征 MOS 界面陷阱密度的常用方法。然而,隨著晶體管柵氧化物厚度降至 3-4nm 以下,準(zhǔn)靜態(tài) C-V 已不適用于高κ材料界面表征。

CP 技術(shù)適用于日益廣泛使用高κ薄膜的晶體管柵,能夠監(jiān)測(cè)界面和電荷捕獲現(xiàn)象。通過(guò)直流或脈沖應(yīng)力下的 CP 測(cè)量,可評(píng)估 HCI、NBTI、TDDB 等可靠性測(cè)試引發(fā)的器件退化量。

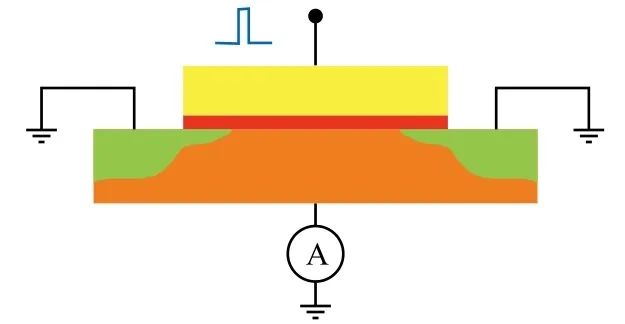

圖1:電荷泵測(cè)量示意圖。晶體管的源極和漏極連接到地面,而柵極以固定的頻率和振幅進(jìn)行脈沖

圖1顯示了與被測(cè)設(shè)備(DUT)的連接。基本的 CP 技術(shù)包括:對(duì)晶體管的柵極施加固定幅度、上升時(shí)間、下降時(shí)間和頻率的電壓脈沖序列時(shí),測(cè)量基極電流。在此測(cè)試中,漏極、源連接到地面,襯底通過(guò)源測(cè)量單元(SMU)連接到地面,用于測(cè)量通過(guò)柵極的電流(Icp)。

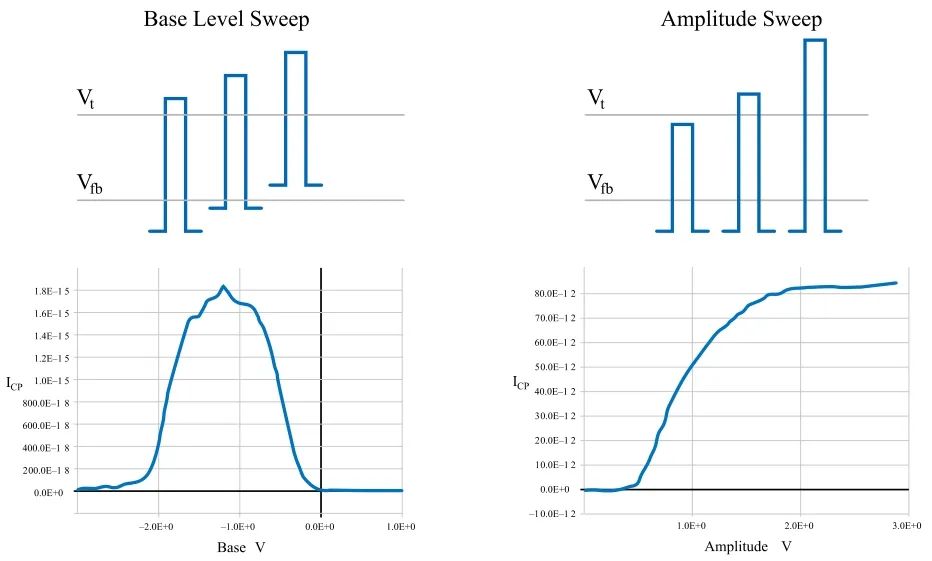

兩種最常見(jiàn)的CP技術(shù)是電壓基極掃描和幅值掃描。在電壓基極電平掃描中,周期(脈沖寬度)和電壓振幅被固定,而掃描脈沖基極電壓(圖2a)。在每個(gè)電壓下,測(cè)量體電流并繪制基本電壓 (ICP vs Vbase),如圖2a所示。

圖2a

圖2b

圖2:用于電荷泵送的兩種掃描類型:a)基極電壓掃描 b)脈沖幅度掃描

第二種電荷泵技術(shù)是電壓幅度掃描,它具有一個(gè)固定的基本電壓和周期 ( 脈沖頻率 ),每個(gè)掃描步驟的電壓振幅都發(fā)生了變化(圖2b)。所獲得的數(shù)據(jù)與從電壓基極掃描中提取的數(shù)據(jù)相似,但在這種情況下,電荷泵電流與電壓幅度 (ICP vs 電壓幅度 ) 這些測(cè)量也可以在多個(gè)頻率 ( 周期 ) 上執(zhí)行,以獲得界面陷阱的頻率響應(yīng)。

對(duì)于高κ材料結(jié)構(gòu),CP技術(shù)可以將被捕獲的電荷 (Nit)量化為:

在硅基板 / 界面層以外的捕獲電荷可以被感知到。圖2a為基底電壓掃描的特征ICP曲線,而圖2b為電壓幅值掃描的特征ICP曲線。

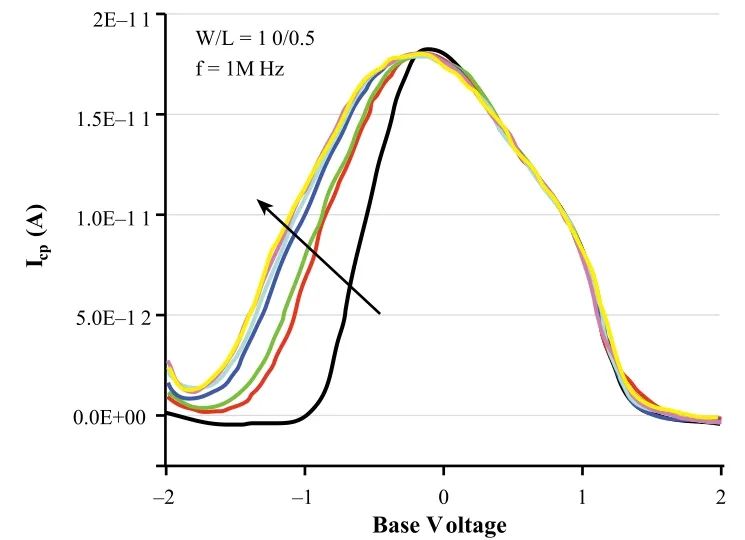

CP技術(shù)也可用于表征界面阱形成的初始階段。圖3顯示了使用1MHz頻率的“新”CP測(cè)量(即以前未測(cè)試過(guò)的MOSFET)。暗態(tài)電流是初始的CP測(cè)量值;較淺的曲線表示隨后的測(cè)量結(jié)果。請(qǐng)注意,在較低的電壓下,ICP曲線的形狀以及大小都發(fā)生了變化。在多次測(cè)量后,隨著效果飽和,變化趨勢(shì)就會(huì)有效地停止。曲線形狀的變化表明,CP測(cè)量所施加的電應(yīng)力導(dǎo)致了界面陷阱的形成。這意味著使用脈沖測(cè)量CP可以有效地對(duì)器件施加壓力并引起一些退化。脈沖應(yīng)力下的退化是對(duì)我們理解偏置溫度不穩(wěn)定性(BTI)和TDDB的有益補(bǔ)充。

圖3. “新”器件上的電荷泵測(cè)量所引起的應(yīng)力效應(yīng)

BTI和TDDB的脈沖應(yīng)力

BTI(NBTI/PBTI)和 TDDB 通常采用高溫高壓交替應(yīng)力與測(cè)量的方式進(jìn)行測(cè)試,以加速退化并縮短驗(yàn)證周期。

NBTI 已成為 PMOSFET 可靠性測(cè)試的重要議題,其特征是閾值電壓升高、漏極電流衰減,但在應(yīng)力解除后會(huì)出現(xiàn)“弛豫”現(xiàn)象,影響直流應(yīng)力測(cè)量的準(zhǔn)確性,從而導(dǎo)致對(duì)壽命評(píng)估的高估。此外,高κ柵材料中普遍存在電荷捕獲與去捕獲,進(jìn)一步加劇了器件性能的動(dòng)態(tài)波動(dòng),使傳統(tǒng)直流應(yīng)力方法難以反映真實(shí)工作場(chǎng)景下的退化行為。

為更真實(shí)模擬器件在快充、逆變等場(chǎng)景下的動(dòng)態(tài)負(fù)載,脈沖應(yīng)力技術(shù)逐步成為先進(jìn)器件可靠性驗(yàn)證的重要手段。脈沖應(yīng)力可模擬不同頻率下的動(dòng)態(tài)開(kāi)關(guān),應(yīng)力間歇期間部分退火恢復(fù),真實(shí)反映器件在實(shí)際應(yīng)用中的老化規(guī)律,幫助工程師更準(zhǔn)確地建立頻率相關(guān)的壽命模型。

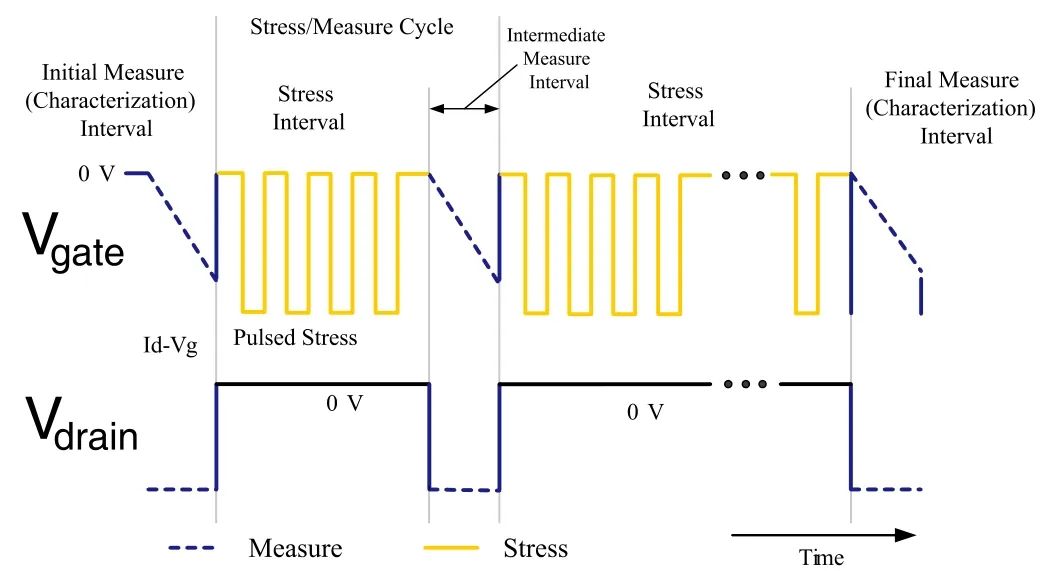

圖4a

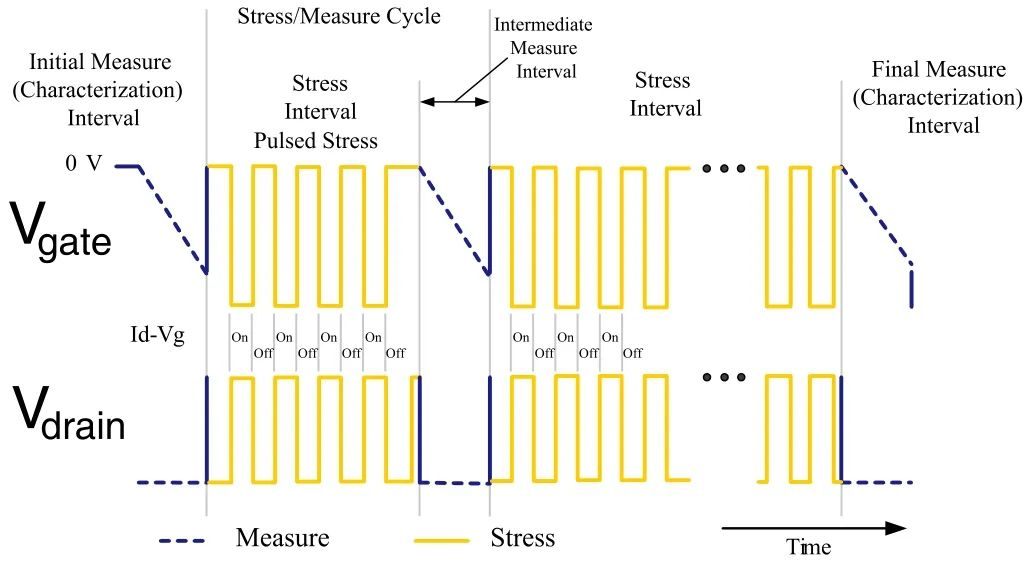

圖4b

圖4. NBTI應(yīng)力/測(cè)量圖,顯示了兩種不同的脈沖應(yīng)力方法:a)使用傳統(tǒng)柵極和漏極電壓的動(dòng)態(tài)NBTI(DNBTI)b)DNBTI模擬逆變器條件,漏極電壓與柵極電壓處于相反的相位

通過(guò)使用周期性應(yīng)力來(lái)模擬器件在電路中的應(yīng)力,脈沖應(yīng)力基本上是一個(gè)短的直流應(yīng)力,被沒(méi)有施加應(yīng)力的時(shí)間中斷(圖4)。對(duì)于NBTI,這種應(yīng)力脈沖之間的非應(yīng)力部分允許退化恢復(fù)到一定程度。這種部分恢復(fù)對(duì)確定并模擬了該器件的使用壽命行為具有重要意義。部分恢復(fù)還不能被很好地理解,并且會(huì)因每個(gè)使用器件的結(jié)構(gòu)、尺寸和材料的組合而有所不同。圖4顯示了兩個(gè)脈沖應(yīng)力的例子,盡管還有其他的脈沖應(yīng)力方法。圖4a顯示了NBTI的脈沖應(yīng)力,其中漏極電壓在應(yīng)力間隔期間保持0V。圖4b顯示了NBTI的脈沖應(yīng)力,除了柵極電壓外漏極電壓是脈沖的。這第二種方法用于模擬逆變電路中的單個(gè)器件的性能。圖4b中的柵極和漏極都受到了壓力,因此在器件退化過(guò)程中同時(shí)存在NBTI和HCI。一般來(lái)說(shuō),脈沖應(yīng)力技術(shù)產(chǎn)生更少的退化,器件的壽命更長(zhǎng)。

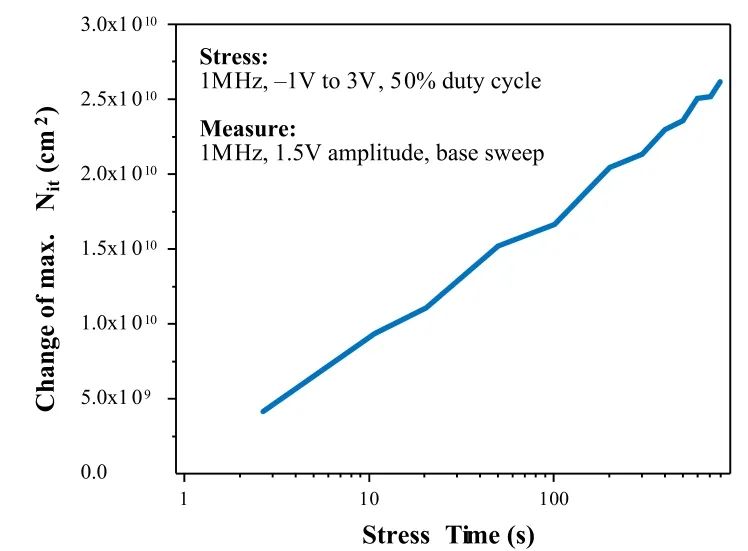

圖5.由于脈沖應(yīng)力而導(dǎo)致的Nit退化

對(duì)于NBTI,脈沖應(yīng)力技術(shù)用于研究單個(gè)器件以及數(shù)字電路的動(dòng)態(tài)行為。圖5顯示了不同脈沖應(yīng)力持續(xù)時(shí)間導(dǎo)致的Nit的增加,結(jié)合了圖4a的應(yīng)力方法和圖2a的周期性CP測(cè)量值。

除了BTI,TDDB在靜態(tài)和動(dòng)態(tài)故障狀態(tài)中的作用可以很好地被理解。對(duì)于在TDDB測(cè)試期間監(jiān)測(cè) SILC(應(yīng)力引發(fā)的泄漏電流),應(yīng)力 / 測(cè)量圖類似于圖4a,但 Vdrain保持在一個(gè)恒定的非零電壓,允許在應(yīng)力期間讀取Id。

結(jié)論

在超寬禁帶氧化鎵功率器件走向光伏、快充、高壓電源真實(shí)場(chǎng)景落地的進(jìn)程中,驗(yàn)證其在高頻、大電流動(dòng)態(tài)開(kāi)關(guān)下的長(zhǎng)期可靠性,是實(shí)現(xiàn)大規(guī)模應(yīng)用的關(guān)鍵門檻。脈沖應(yīng)力技術(shù)與電荷泵測(cè)量的結(jié)合,不僅能精準(zhǔn)量化高κ柵結(jié)構(gòu)中電荷捕獲與陷阱演化,更能模擬真實(shí)工況下的動(dòng)態(tài)負(fù)載,應(yīng)力期間與恢復(fù)過(guò)程的退化與自愈特性,為Ga?O?器件建立可信的可靠性模型。

相較傳統(tǒng)直流測(cè)試,脈沖應(yīng)力驗(yàn)證讓工程師能在更短時(shí)間內(nèi)獲得更真實(shí)的老化評(píng)估,推動(dòng)氧化鎵器件從實(shí)驗(yàn)室加速走向規(guī)模應(yīng)用,為產(chǎn)業(yè)落地和客戶信賴保駕護(hù)航。

-

電源模塊

+關(guān)注

關(guān)注

33文章

1906瀏覽量

94412 -

功率器件

+關(guān)注

關(guān)注

42文章

1930瀏覽量

92644 -

氧化鎵

+關(guān)注

關(guān)注

5文章

84瀏覽量

10635

原文標(biāo)題:從材料到器件:氧化鎵功率器件動(dòng)態(tài)可靠性測(cè)試新思路

文章出處:【微信號(hào):泰克科技,微信公眾號(hào):泰克科技】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

什么是MOSFET柵極氧化層?如何測(cè)試SiC碳化硅MOSFET的柵氧可靠性?

提供半導(dǎo)體工藝可靠性測(cè)試-WLR晶圓可靠性測(cè)試

電子元器件的可靠性篩選

GaN可靠性的測(cè)試

GaN HEMT可靠性測(cè)試:為什么業(yè)界無(wú)法就一種測(cè)試標(biāo)準(zhǔn)達(dá)成共識(shí)

單片機(jī)應(yīng)用系統(tǒng)的可靠性與可靠性設(shè)計(jì)

SiC MOSFET FIT率和柵極氧化物可靠性的關(guān)系

中科院微電子所在硅基氮化鎵橫向功率器件的動(dòng)態(tài)可靠性研究方面獲進(jìn)展

龍騰半導(dǎo)體建有功率器件可靠性與應(yīng)用實(shí)驗(yàn)中心

功率器件可靠性試驗(yàn)測(cè)試項(xiàng)目

氮化鎵功率器件測(cè)試方案

電子元器件測(cè)試軟件助力可靠性測(cè)試,保證器件性能和質(zhì)量

氧化鎵功率器件動(dòng)態(tài)可靠性測(cè)試方案

氧化鎵功率器件動(dòng)態(tài)可靠性測(cè)試方案

評(píng)論