本文講述了AMD UltraScale /UltraScale+ FPGA 原生模式下,異步模式與同步模式的對比及其對時鐘設置的影響。

在 UltraScale/UltraScale+ 中引入了 RXTX_BITSLICE。該原語用于捕獲和接收 XPIO IOB。建議用戶使用 High-Speed SelectIO (HSSIO) Wizard。UG571詳細介紹了原語和連接。

例如,在使用源同步時,為什么 HSSIO Wizard 限制用戶每個 Bank 只能使用 23 個差分對?在 UltraScale/UltraScale+ 中源同步有什么要求?我該如何判斷是否需要使用異步模式,還是可以改用源同步模式?

值得探討的首要主題是 UltraScale/UltraScale+ 中的源同步,及其對時鐘設置的影響。

在 UltraScale/UltraScale+ 中使用 HSSIO 或原生模式時定義源同步

在源同步模式下使用 RXTX_BITSLICE 時,選通/捕獲(QBC 或 DBC)時鐘會通過半字節間和字節間時鐘設置,直接布線至 Bank 中的捕獲觸發器。半字節間和字節間時鐘設置影響范圍不超過其所在 Bank。這意味著捕獲時鐘需以接口速度來工作(1 Gb/s 捕獲條件下,工作頻率為 500 MHz),并且它具有已知的相位對齊。捕獲時鐘可采用邊沿對齊或中心對齊與數據對齊。

存儲器接口中的選通(通常稱之為 DQS)會按數據速率隨數據一起發射,并且通常并不會連續發射,它用于在接收側捕獲數據。在 HSSIO/原生模式下,選通是按數據速率與數據一起發射的,并且不一定是連續的。

PLL 的輸入來自 GC 管腳,如果位于 _QBC_GC 管腳上并且是連續時鐘,則可與捕獲時鐘/選通共享。Bank 的 PLL 會對含專用輸出 CLKOUTPHY 的解串器進行時鐘設置,CLKOUTPHY 只能觸達其 Bank 內的 BITSLICE & BITSLICE_CONTROL。因此,無法為兩個 Bank 的同一個時鐘使用源同步。

總結

源同步要求捕獲時鐘按接口速度來運行,并且已知與數據的相位關系,只能在單個 Bank 內運行。

注釋:單個接口可以跨多個 Bank,而 HSSIO 有一個選項,要求每個 Bank 至少一個捕獲時鐘/選通。

定義異步模式

如果該接口未按接口速率向每個 Bank 發送一個捕獲時鐘,或者該捕獲時鐘與接口時鐘之間不存在已知的相位關系,則必須將該接口視作為異步。如果存在捕獲時鐘并且需要跨多個 Bank,則需將其視作為異步。

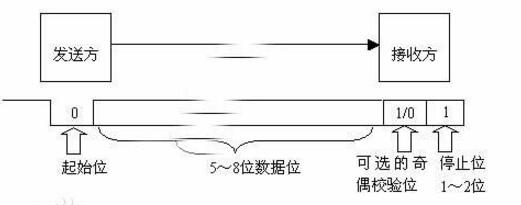

在某些接口中,會隨幀時鐘、字時鐘或其他并行速率時鐘發送數據,這表示會隨數據發送一個時鐘,但該時鐘不可用作為捕獲時鐘(它需要時鐘管理器來進行倍率處理)。

該時鐘需視作為異步。 并且,未隨數據一起發送時鐘的任意接口同樣如此。

異步時鐘設置

在異步模式 (SERIAL_MODE= TRUE) 中,并不會隨選通一起完成 RX 數據的捕獲,PLL CLKOUTPHY 用于對捕獲觸發器進行時鐘設置,并且必須存在用于對齊時鐘與數據的機制。XAPP1330包含 CDR 邏輯,可搭配 HSSIO Wizard 使用。

如果您的某個接口跨多個 Bank,那么每個 Bank 都需要一個 HSSIO Wizard,并且每個 Wizard 都將使用 PLL 來為每個 Bank 創建一個 CLKOUTPHY。

-

FPGA

+關注

關注

1645文章

22040瀏覽量

618155 -

amd

+關注

關注

25文章

5586瀏覽量

136321 -

時鐘

+關注

關注

11文章

1898瀏覽量

133197

原文標題:開發者分享|AMD UltraScale?/UltraScale+? FPGA:異步模式的適用時機及其使用方式

文章出處:【微信號:gh_2d1c7e2d540e,微信公眾號:XILINX開發者社區】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

同步復位與異步復位,同步釋放的對比疑問

怎么理解CC1101的異步串行工作模式?

快速啟動是否支持同步讀取模式

什么是異步轉移模式

異步傳輸模式工作原理簡介

FPGA設計中的異步復位同步釋放問題

一文看懂異步傳輸模式atm的特點

AMD FPGA異步模式與同步模式的對比

AMD FPGA異步模式與同步模式的對比

評論