一. AMD FPGA的加載模式簡(jiǎn)介

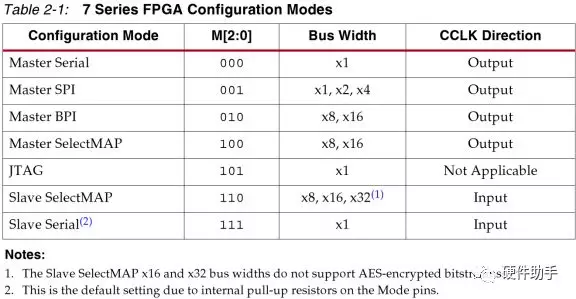

在不帶內(nèi)置ARM核的AMD FPGA產(chǎn)品系列中,F(xiàn)PGA的程序加載方式并沒有發(fā)生大的變化,仍舊采用JTAG、Master SPI、Serial Configuration、Master BPI、Select MAP幾種加載模式,關(guān)于每種加載模式的電路圖和工作原理不再進(jìn)行描述,每個(gè)產(chǎn)品系列的configuration guide中都有詳細(xì)描述,關(guān)于這部分的硬件設(shè)計(jì)和工作原理,用戶可以參考對(duì)應(yīng)的文檔如UG470、UG570等。

在不同系列的pure FPGA產(chǎn)品發(fā)展過程中,加載模式發(fā)生了一些細(xì)微變化簡(jiǎn)述如下:

A. 自7系列產(chǎn)品開始Master SPI加載模式增加了x2、x4模式,自Ultrascale系列開始在x2、x4的基礎(chǔ)上又增加了x8模式(dual quad SPI模式);

B. 自7系列產(chǎn)品開始不再支持AMD自有的FLASH PROM產(chǎn)品,也不再更新自有的FLASH PROM產(chǎn)品,在UG908文檔中不斷更新測(cè)試過的第三方FLASH,如Micron、Spansion、ISSI等廠商的SPI FLASH和BPI FLASH;

帶內(nèi)置ARM核的SOC產(chǎn)品中,芯片內(nèi)部集成了bootrom并且需要使用FirstBootloader來(lái)進(jìn)行加載,因此其加載模式和加載流程與pure FPGA器件有區(qū)別,常見的boot mode包括JTAG模式、QSPI模式、SD Card模式、EMMC模式、NAND模式、USB模式等,詳細(xì)描述可以參考UG585和UG1085文檔中的boot and configuration章節(jié),SOC系列產(chǎn)品的加載方式我們將在以后文章中單獨(dú)說(shuō)明。

本文的寫作初衷是介紹Select MAP加載模式,因此后面的描述基本都是基于不帶內(nèi)置ARM核的FPGA來(lái)展開。

二. bit、bin和mcs文件的區(qū)別

在使用JTAG或者其他芯片來(lái)Program FPGA和FLASH時(shí),我們最常用到的三個(gè)文件是bitstream文件、bin文件和mcs文件,最常遇到的問題是這三個(gè)文件有什么區(qū)別,在這一章節(jié)中我們不展開對(duì)文件內(nèi)部詳細(xì)數(shù)據(jù)格式的解析,主要針對(duì)這三個(gè)文件的主要差別和使用場(chǎng)景進(jìn)行對(duì)比和描述。

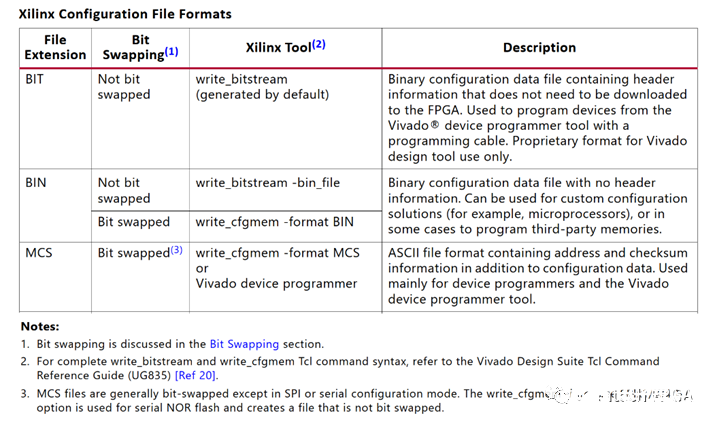

在configuration userguide中,有如下描述:

bit、bin和mcs文件

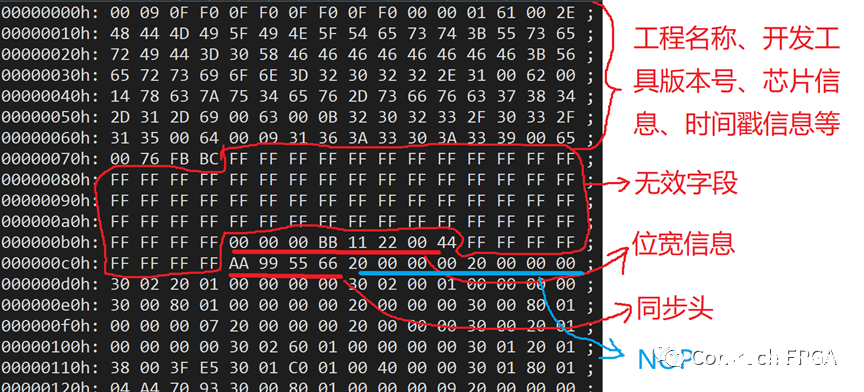

我截取一個(gè)真實(shí)bitstream文件的開始部分,如下圖:

bit文件前端內(nèi)容

我們?cè)贘TAG Program FPGA的時(shí)候,使用的是bitstream文件;在Serial模式、SPIx1模式Program FLASH的時(shí)候,bin文件和mcs文件都可以使用;在SPIx4模式、SPIx8模式、BPI模式、SelectMAP模式Program FLASH的時(shí)候,使用的是MCS文件;在SelectMAP模式使用外部其他芯片(如MCU、ARM、CPU、CPLD、FPGA)Program FPGA的時(shí)候,使用的是bin文件,但是需要我們自己做bit swap。

從上面兩圖展開介紹:bitstream文件開頭部分包含工程名稱、開發(fā)工具版本號(hào)、芯片型號(hào)、時(shí)間戳、加載位寬、同步頭等信息,真正被Program進(jìn)入FPGA的有效bit在同步頭和緊跟著的NOP之后;在bin文件沒有做bit swap的時(shí)候,bin文件直接從全FFFF的無(wú)效字段開始,比bitstream文件少了工程名稱、開發(fā)工具版本號(hào)、芯片型號(hào)、時(shí)間戳、加載位寬、同步頭等信息;而mcs文件通常比bitstream文件、bin文件大很多,是因?yàn)閙cs文件中加入了對(duì)FLASH的操作命令以及其他一些信息,并且在多位數(shù)據(jù)位寬時(shí),mcs文件中的有效數(shù)據(jù)部分根據(jù)加載位寬做了bit swap。

三. SelectMAP加載模式的優(yōu)缺點(diǎn)

什么會(huì)有場(chǎng)景需要使用SelectMAP加載模式?SelectMAP加載模式有哪些優(yōu)缺點(diǎn)呢?SelectMAP模式有如下特點(diǎn):

A. 可以外供時(shí)鐘給CCLK,頻率確定;而Serial模式和Master SPI模式下FPGA自己震蕩產(chǎn)生的CCLK頻率低、頻率不精確;----優(yōu)點(diǎn)

B. SelectMAP模式可以支持8bit、16bit、32bit加載;----優(yōu)點(diǎn)

C. 在板卡上有多個(gè)FPGA芯片、MCU+FPGA、ARM+FPGA等架構(gòu)下,可以共用一個(gè)FLASH、SD卡、EMMC等存儲(chǔ)介質(zhì)來(lái)存儲(chǔ)加載文件;----優(yōu)點(diǎn)

D. 占用的IO數(shù)量多;----缺點(diǎn)

E. 需要外面一顆芯片來(lái)實(shí)現(xiàn)SelectMAP模式的加載;----缺點(diǎn)

綜合以上特點(diǎn),SelectMAP模式在兩種應(yīng)用場(chǎng)景中會(huì)有優(yōu)勢(shì):

場(chǎng)景一:在使用Serial模式和Master SPI模式的時(shí)候,加載數(shù)據(jù)線位寬只能是1、2、4或8,在Master Serial和Master SPI模式下CCLK時(shí)鐘由FPGA內(nèi)部震蕩產(chǎn)生,這個(gè)時(shí)鐘頻率是不準(zhǔn)確的,而且我們?cè)诋a(chǎn)生bitstream的配置選項(xiàng)中選擇的configuration rate頻率有限;所以在期望縮短加載時(shí)間的應(yīng)用場(chǎng)景下,更高位寬更高CCLK頻率的SelectMAP模式可以大大縮短加載時(shí)間。

場(chǎng)景二:在板卡上有多個(gè)芯片時(shí),可以共用加載文件的存儲(chǔ)介質(zhì),來(lái)減少存儲(chǔ)介質(zhì)芯片數(shù)量。

四. SelectMAP加載的硬件和軟件設(shè)計(jì)

SelectMAP硬件設(shè)計(jì):

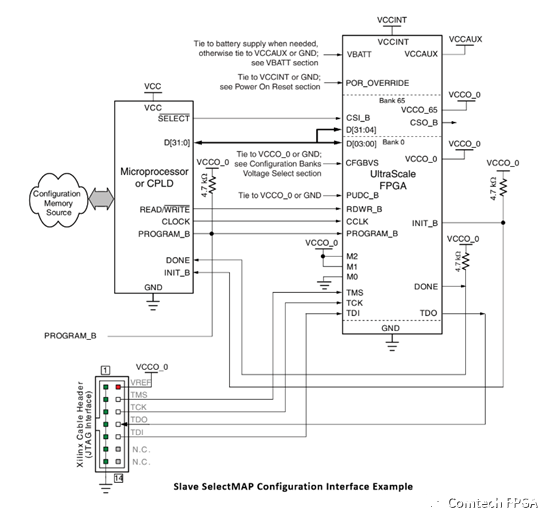

在configuration userguide中給出了SelectMAP模式的硬件原理圖示例:

單片F(xiàn)PGA的SelectMAP加載

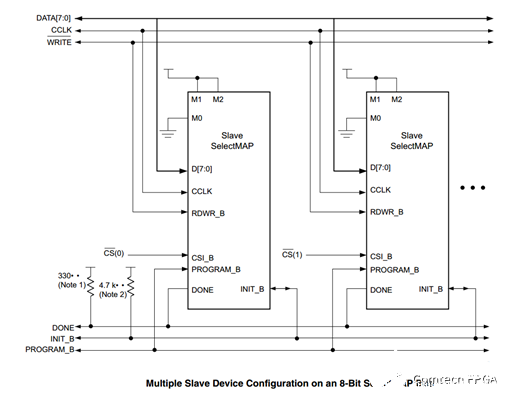

多片F(xiàn)PGA的SelectMAP加載

Select MAP模式軟件設(shè)計(jì):

而FPGA前端負(fù)責(zé)實(shí)現(xiàn)Select MAP加載的主控器件,可以是MCU、CPLD、ARM、FPGA等,只需要按照如下時(shí)序?qū)in文件中的有效內(nèi)容做bit swap后寫入到FPGA即可。

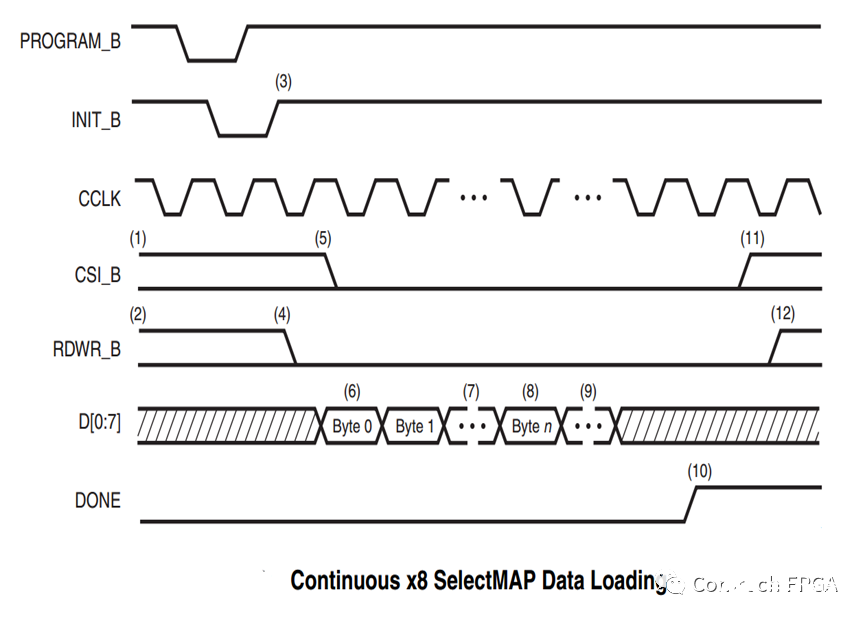

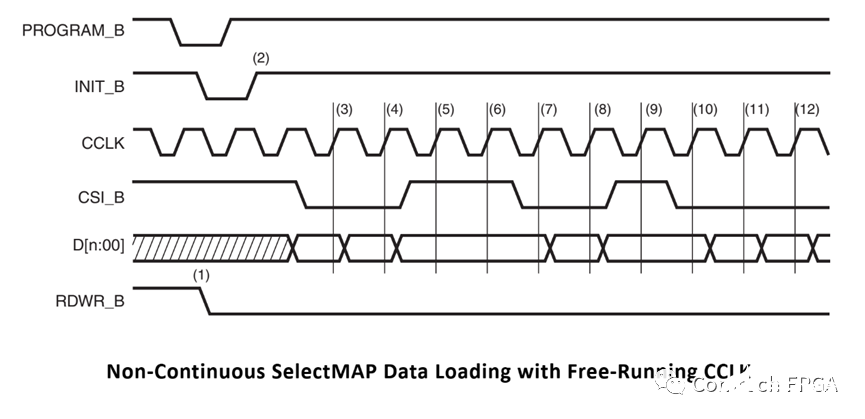

以8bit SelectMAP模式為例:

連續(xù)數(shù)據(jù)loading SelectMAP模式

不連續(xù)數(shù)據(jù)loading SelectMAP模式

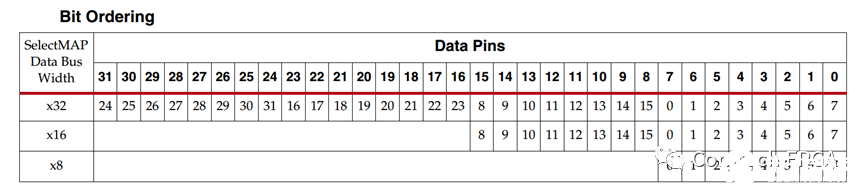

需要說(shuō)明的是在SelectMAP模式中的bit swap,需要根據(jù)數(shù)據(jù)線位寬在主控器件中實(shí)現(xiàn)如下bit swap:

SelectMAP模式bit swap

如果前端主控器件是MCU、ARM、CPU,可以參考AMD官方參考設(shè)計(jì)XAPP583,C代碼在XAPP583中可以獲得;如果前端主控器件是CPLD或者FPGA,作者曾經(jīng)寫Verilog代碼實(shí)現(xiàn)過一片小FPGA做主控、通過Select MAP模式加載多片F(xiàn)PGA,歡迎咨詢作者本人。

審核編輯:湯梓紅

-

FPGA

+關(guān)注

關(guān)注

1643文章

21954瀏覽量

613988 -

mcu

+關(guān)注

關(guān)注

146文章

17824瀏覽量

360242 -

amd

+關(guān)注

關(guān)注

25文章

5557瀏覽量

135864 -

FlaSh

+關(guān)注

關(guān)注

10文章

1662瀏覽量

150965 -

程序

+關(guān)注

關(guān)注

117文章

3820瀏覽量

82389

發(fā)布評(píng)論請(qǐng)先 登錄

串行配置和并行配置模式下的多片FPGA配置數(shù)據(jù)流加載方式

AMD Xilinx 7系列FPGA的Multiboot多bit配置

Xilinx SelectMAP 配置問題

怎么通過GPIF II在Slave SelectMap中配置FPGA

由于JTAG,Spartan6從機(jī)SelectMap配置失敗了怎么辦

FPGA配置引腳說(shuō)明及加載時(shí)序

通過USB接口實(shí)現(xiàn)FPGA 的SelectMap配置

V5 FPGA配置回讀

FPGA多重加載技術(shù)的設(shè)計(jì)模塊及其在硬件平臺(tái)上的多模式啟動(dòng)測(cè)試并分析

FPGA的配置/加載方式

基于ARM-Linux平臺(tái)的FPGA程序加載模式淺析

安路EG4X FPGA從動(dòng)串行加載模式

安路EG4X FPGA從動(dòng)并行加載模式

AMD FPGA中MicroBlaze的固化流程詳解

AMD FPGA的SelectMAP加載模式

AMD FPGA的SelectMAP加載模式

評(píng)論