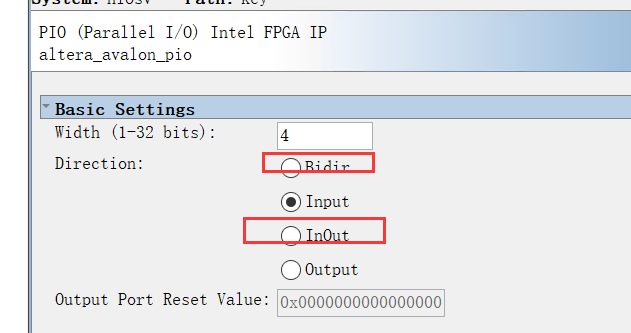

PIO IP是FPGA 設計中比較簡單常用的IP, 當設置PIO IP的Direction的時候,可以看到有如下4個選項:

Input代表這組IO是輸入引腳,Output代表這組IO是輸出引腳,這些很好理解,但Bidir和InOut都表示雙向的意思,它們有什么區(qū)別嗎?

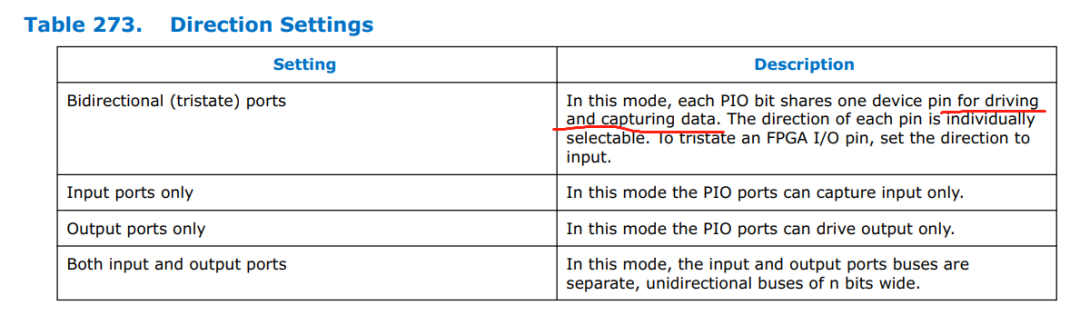

參考28.4.1.2. Direction (intel.com)可知:

bidir,指n位寬的信號中的每一位都可以單獨/分別設置為讀或是寫。

inout,指將n位寬的信號,全設置為讀或全部設置為寫,但是不能要求其中某些位讀而某些位為寫。

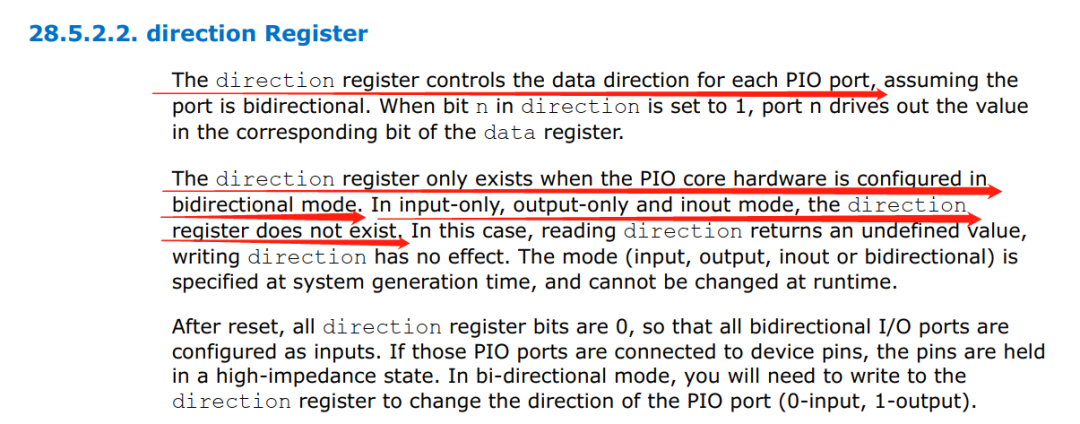

只有設置為bidir模式的時候,才存在direction寄存器,用于控制某個I/O端口用于讀(input),還是用于寫(output):

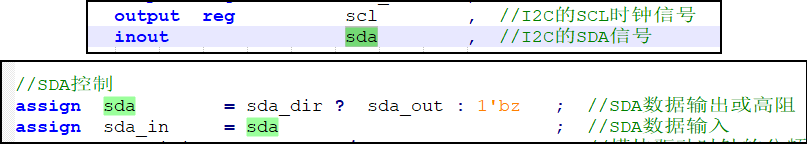

不過在Altera PIO IP之外,其他地方在用bidir和inout表達的時候,bidir(bidir是“bidirectional”的縮寫)更側(cè)重于表示雙向的特性,是一個概念性的描述;而inout是硬件描述語言中用于聲明雙向信號或端口的關(guān)鍵字,是一種具體的語法形式。例如在VHDL和Verilog中,都使用inout關(guān)鍵字來實現(xiàn)bidir功能,用于實現(xiàn)雙向的接口或總線,如I2C等總線。

I2C的信號線電路設計參考如下:

-

FPGA

+關(guān)注

關(guān)注

1645文章

22034瀏覽量

617946 -

Altera

+關(guān)注

關(guān)注

37文章

805瀏覽量

155954 -

友晶科技

+關(guān)注

關(guān)注

0文章

4瀏覽量

7022 -

PIO

+關(guān)注

關(guān)注

0文章

20瀏覽量

6419

原文標題:【答疑解惑】Altera FPGA 的PIO IP當中bidir和inout選項的區(qū)別

文章出處:【微信號:友晶FPGA,微信公眾號:友晶FPGA】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

Altera Stratix 10和Agilex 7 FPGA的電源管理及配置問題案例

Altera Agilex 3 FPGA和SoC產(chǎn)品介紹

Intel-Altera FPGA:通信行業(yè)的加速引擎,開啟高速互聯(lián)新時代

Altera大學成立,助力FPGA教學發(fā)展與人才培養(yǎng)

Altera 40G Ethernet IP環(huán)回測試教程

Altera Agilex 7 M系列FPGA正式量產(chǎn)出貨

Altera Agilex 5 D系列FPGA的性能和能效

Altera發(fā)布最新FPGA產(chǎn)品和開發(fā)工具套件

Altera正式獨立運營:FPGA行業(yè)格局將迎來新變局

使用IP核和開源庫減少FPGA設計周期

基于Altera Agilex? 7 400G Ethernet IP 與FPC202芯片控制使用手冊

Altera JESD204B IP核和TI DAC37J84硬件檢查報告

Altera FPGA 的PIO IP當中bidir和inout選項的區(qū)別

Altera FPGA 的PIO IP當中bidir和inout選項的區(qū)別

評論