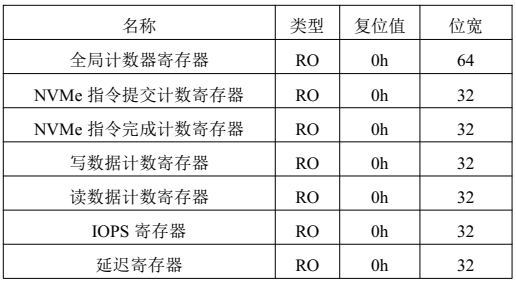

DMA 控制單元負(fù)責(zé)控制 DMA 傳輸事務(wù), 該單元承擔(dān)了 DMA 事務(wù)到 NVMe 事務(wù)的轉(zhuǎn)換任務(wù), 使用戶對(duì)數(shù)據(jù)傳輸事務(wù)的控制更加簡(jiǎn)單快捷。 DMA 控制功能由 DMA寄存器組實(shí)現(xiàn)。

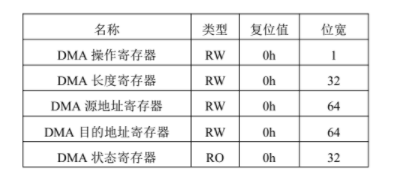

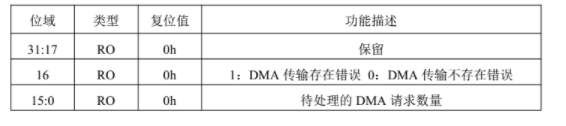

DMA 寄存器組包含 DMA 操作寄存器、 DMA 長(zhǎng)度寄存器、 DMA 源目的地址寄存器和 DMA 狀態(tài)寄存器。 DMA 操作寄存器定義了 DMA 請(qǐng)求類(lèi)型, 包括寫(xiě)和讀操作; DMA 長(zhǎng)度寄存器定義了 DMA 請(qǐng)求的數(shù)據(jù)傳輸長(zhǎng)度, 該長(zhǎng)度以 NVMe 設(shè)備邏輯塊大小為單位; DMA 源地址和 DMA 目的地址寄存器定義了 DMA 請(qǐng)求的源數(shù)據(jù)存放的起始地址和數(shù)據(jù)傳輸?shù)哪康牡刂罚?DMA 狀態(tài)寄存器定義了當(dāng)前待運(yùn)行的 DMA請(qǐng)求數(shù)量和 DMA 請(qǐng)求執(zhí)行狀態(tài)信息。 DMA 寄存器組定義如表 1 所示, 其中 DMA

狀態(tài)寄存器定義如表 2 所示。

表 1 DMA 寄存器組定義

表 2 DMA狀態(tài)寄存器定義

想進(jìn)一步了解相關(guān)視頻,請(qǐng)搜索B站用戶:專(zhuān)注與守望

鏈接:https://space.bilibili.com/585132944/dynamic?spm_id_from=333.1365.list.card_title.click

-

FPGA

+關(guān)注

關(guān)注

1645文章

22036瀏覽量

618126 -

PCIe

+關(guān)注

關(guān)注

16文章

1340瀏覽量

85119 -

高速存儲(chǔ)

+關(guān)注

關(guān)注

0文章

10瀏覽量

6011 -

nvme

+關(guān)注

關(guān)注

0文章

251瀏覽量

23235

發(fā)布評(píng)論請(qǐng)先 登錄

Xilinx FPGA NVMe Host Controller IP,NVMe主機(jī)控制器

Xilinx FPGA高性能NVMe SSD主機(jī)控制器,NVMe Host Controller IP

高性能NVMe主機(jī)控制器,Xilinx FPGA NVMe Host Accelerator IP

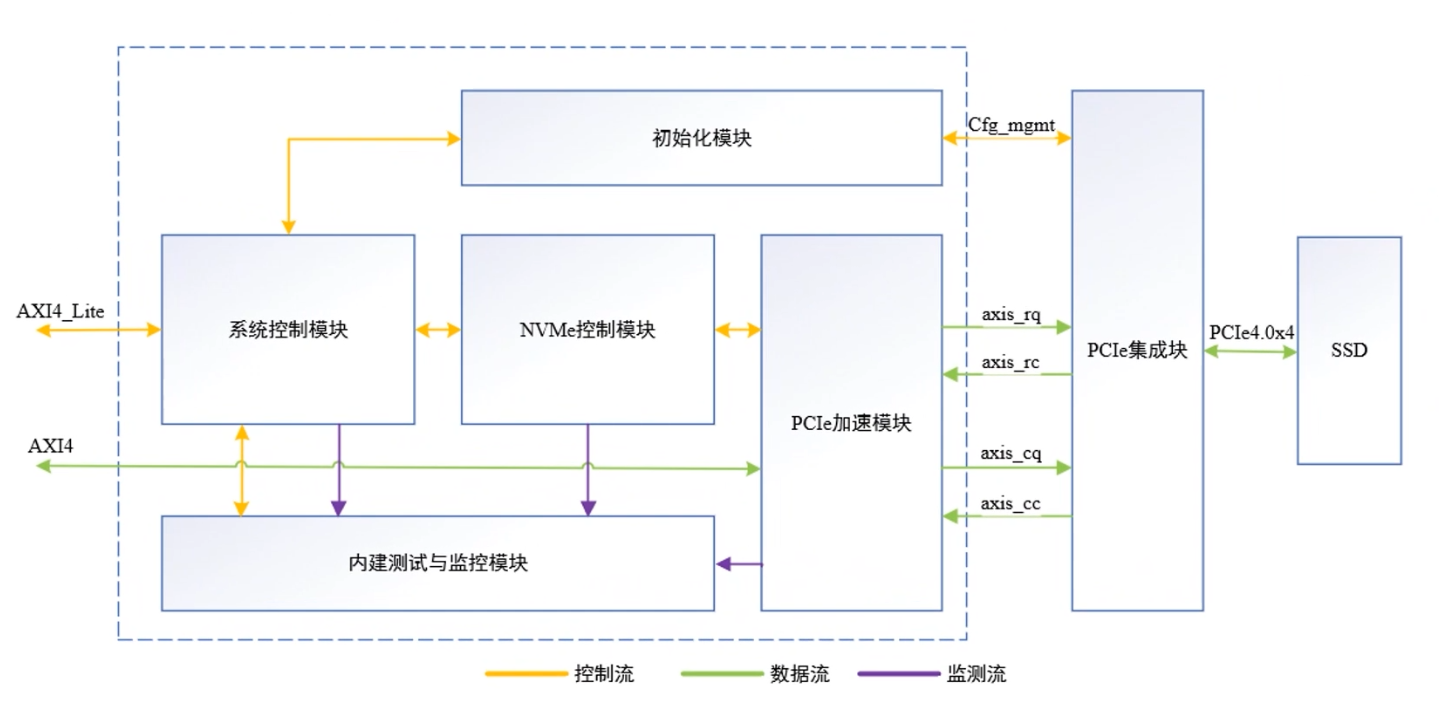

NVMe IP高速傳輸卻不依賴便利的XDMA設(shè)計(jì)之三:系統(tǒng)架構(gòu)

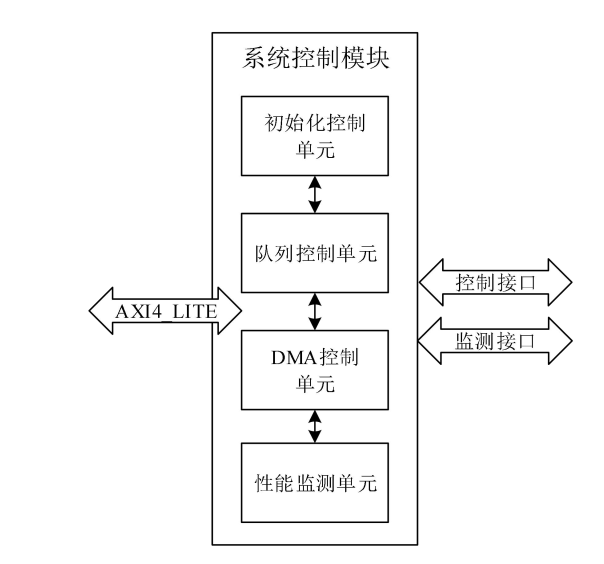

NVMe IP高速傳輸擺脫XDMA設(shè)計(jì)之四:系統(tǒng)控制模塊設(shè)計(jì)

NVMe IP高速傳輸卻不依賴XDMA設(shè)計(jì)之五:DMA 控制單元設(shè)計(jì)

NVMe高速傳輸之擺脫XDMA設(shè)計(jì)之六:性能監(jiān)測(cè)單元設(shè)計(jì)

NVMe高速傳輸之擺脫XDMA設(shè)計(jì)之十:NVMe初始化狀態(tài)機(jī)設(shè)計(jì)

NVMe IP over PCIe 4.0:擺脫XDMA,實(shí)現(xiàn)超高速!

NVMe IP高速傳輸卻不依賴XDMA設(shè)計(jì)之二:PCIe讀寫(xiě)邏輯

NVMe IP高速傳輸卻不依賴XDMA設(shè)計(jì)之三:系統(tǒng)架構(gòu)

NVMe IP高速傳輸卻不依賴XDMA設(shè)計(jì)之四:系統(tǒng)控制模塊

NVMe IP高速傳輸卻不依賴XDMA設(shè)計(jì)之六:性能監(jiān)測(cè)單元設(shè)計(jì)

NVMe IP高速傳輸卻不依賴XDMA設(shè)計(jì)之五:DMA 控制單元設(shè)計(jì)

NVMe IP高速傳輸卻不依賴XDMA設(shè)計(jì)之五:DMA 控制單元設(shè)計(jì)

評(píng)論