以下文章來源于半導體小馬,作者小馬

WAT(Wafer Acceptance Test)測試,也叫PCM(Process Control Monitoring),對Wafer劃片槽(Scribe Line)測試鍵(Test Key)的測試,通過電性參數來監控各步工藝是否正常和穩定。

劃片槽(Scribe Line)和測試鍵(Test Key):這是在半導體制造過程中用于WAT測試的兩個關鍵元素。劃片槽是沿著晶圓邊緣的窄條,用于后續的切割(dicing)過程。測試鍵則是設在劃片槽內或者邊緣的特定區域,用于WAT測試。 電性參數:這些參數包括電容、電阻、接觸以及金屬線路等,這些都是在制造過程中需要監控的重要指標。它們反映了半導體器件的電氣特性,如電流傳導能力、電壓承受能力等。

CP(Circuit Probing)也叫“Wafer Probe”或者“Die Sort”,是對整片Wafer的每個Die的基本器件參數進行測試,例如Vt(閾值電壓),Rdson(導通電阻),BVdss(源漏擊穿電壓),Igss(柵源漏電流),Idss(漏源漏電流)等,把壞的Die挑出來,會用墨點(Ink)標記,可以減少封裝和測試的成本,CP pass才會封裝,一般測試機臺的電壓和功率不高,CP是對Wafer的Die進行測試,檢查Fab廠制造的工藝水平,把壞的Die挑出來,可以減少封裝和測試的成本。

FT(final test)是對封裝好的Chip進行Device應用方面的測試,把壞的chip挑出來,FT pass后還會進行process qual和product qual,FT是對package進行測試,檢查封裝造廠的工藝水平。

廣義上的FT也稱為ATE(Automatic Test Equipment),一般情況下,ATE通過后可以出貨給客戶,但對于要求比較高的公司或產品,FT測試通過之后,還有SLT(System Level Test)測試,也稱為Bench Test。SLT測試比ATE測試更嚴格,一般是功能測試,測試具體模塊的功能是否正常。經長期的多工況驗證,滿足更多生產環境和工程環境的要求。

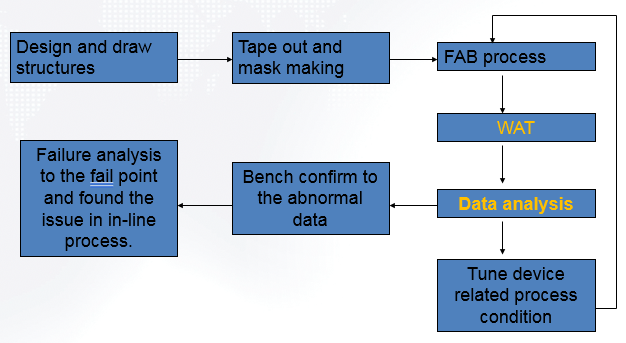

WAT監控工藝一般流程

WAT測試常見結構

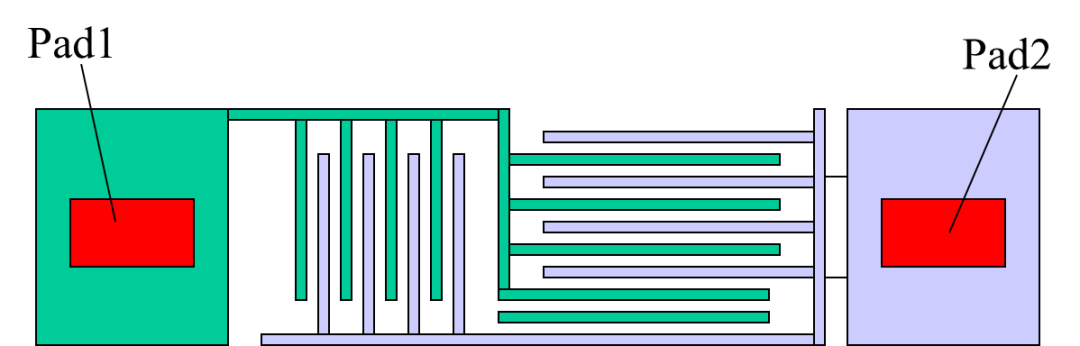

隔離結構

隔離結構用于測量黃光、刻蝕與導線相關的能力,如AA,Poly,Metal

測試方法:在兩個Pad上加電壓測量電流或加電流測量電壓

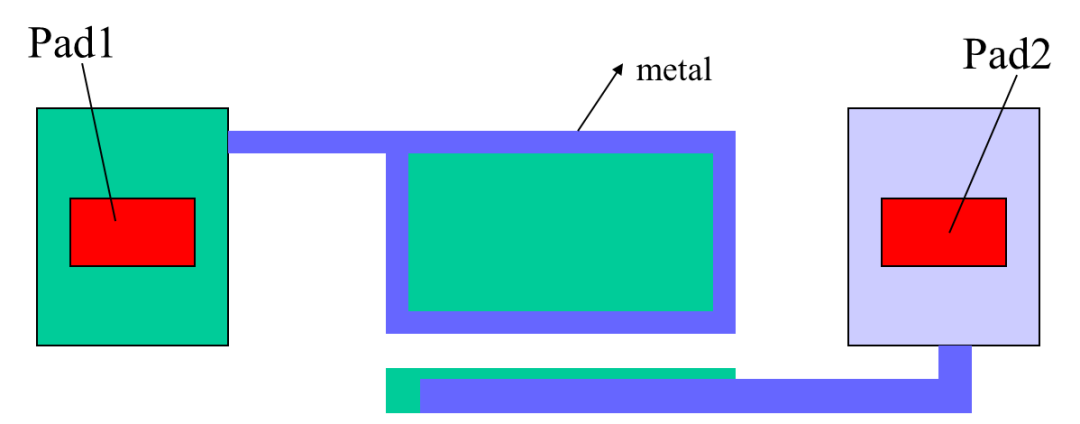

導通結構

導通結構用于測量黃光、刻蝕與導線相關的能力,如AA,Poly,Metal

測試方法:在兩個Pad上加電壓測量電阻

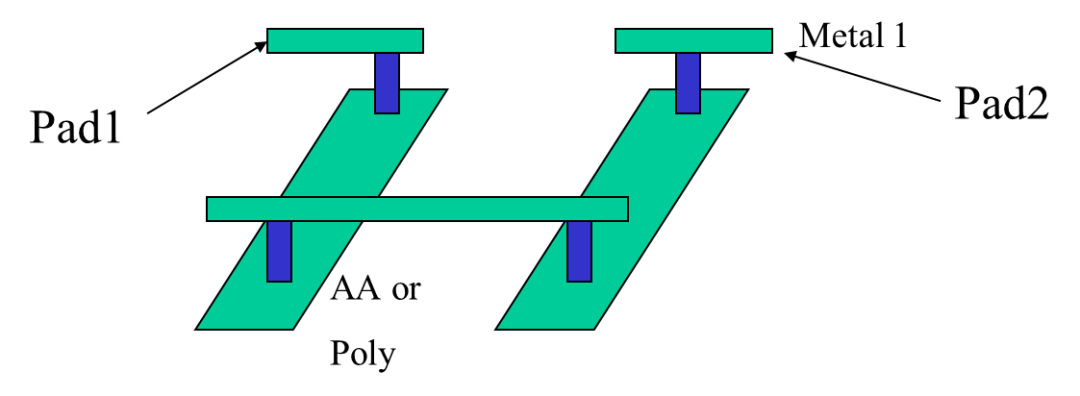

孔接觸結構

孔接觸結構用于測量孔相關的工藝能力,如CNT、VIA

測試方法:在兩個Pad上加電壓測量電阻

薄層電阻結構

薄層電阻結構用于測量導線的Rs,如AA,both silicide and non-silicide, wells, metals

測試方法:在兩個Pad上加電壓測量電阻

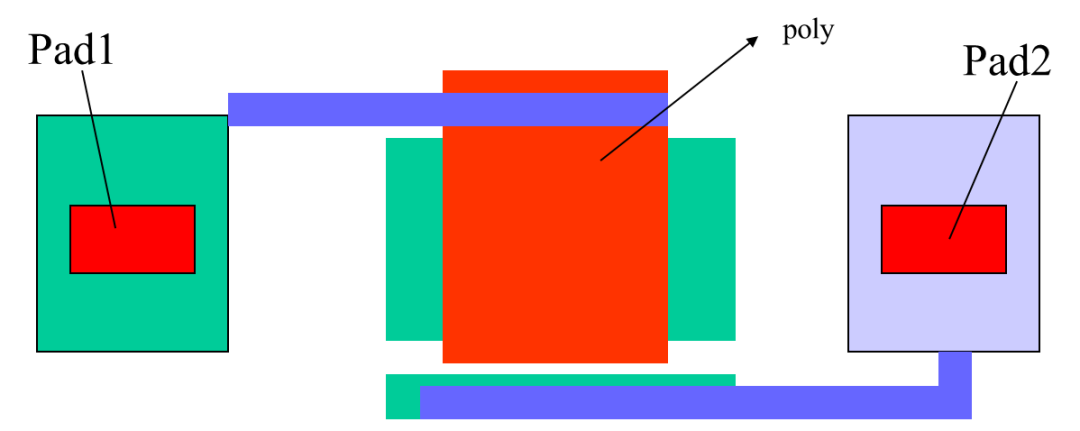

柵介質結構

柵介質結構用于監控柵介質的厚度

測試方法:測量MOS電容的容值,然后計算得出柵介質厚度

接點泄漏結構

用于監控S/D接點漏電流,包括bulk pattern, AA edge pattern, poly finger pattern

測試方法:在兩個Pad上加電壓測量電流或加電流測量電壓

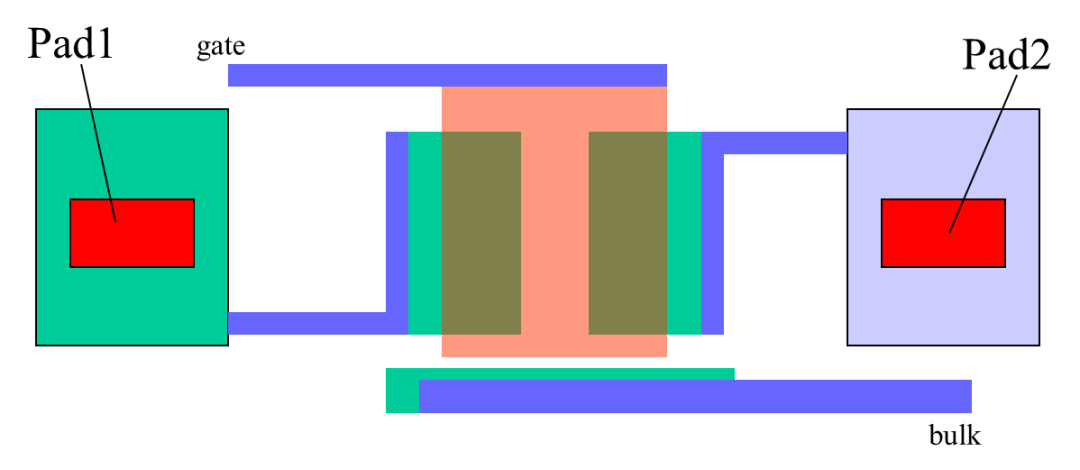

場效應器件結構

用于監控隔離能力,有Poly和Metal 2種結構

測試方法:體硅接地,柵極加載掃描電壓,測量Pad間的電流

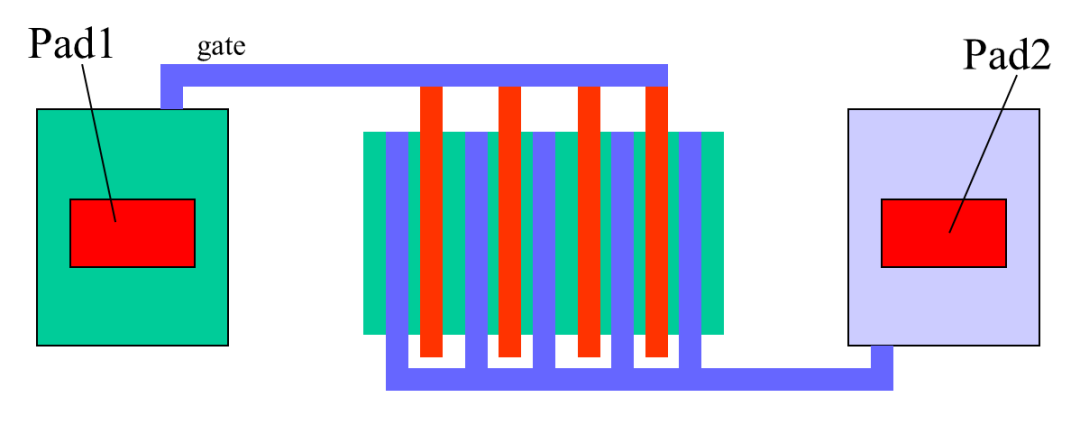

硅化物橋連結構

用于監控Spacer是否存在硅化物殘留

測試方法:Pad間加電壓,測量電流

器件結構

用于監控器件表現

測試方法:Vt,Ion,Ioff,Idsat,DIBL,Isub,Ig等按定義進行測試,詳細說明后續介紹

其它結構

設計規則檢查結構,例如結到阱間距規則檢查、阱包圍規則檢查、多晶硅端帽規則檢查、接觸孔到多晶硅間距規則檢查等。

H型器件用于監測器件的 “駝峰現象”(hump phenomena)。

米勒電容用于監測多晶硅的邊緣放置誤差(E-CD,Edge Critical Dimension)。

使用小電阻監測晶圓允收測試(WAT,Wafer Acceptance Test)探針卡的接觸電阻。

-

測試

+關注

關注

8文章

5667瀏覽量

128547 -

半導體

+關注

關注

335文章

28771瀏覽量

235095 -

晶圓

+關注

關注

53文章

5136瀏覽量

129443

原文標題:半導體WAT測試是什么?

文章出處:【微信號:芯長征科技,微信公眾號:芯長征科技】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

半導體芯片內部結構詳解

什么是半導體晶圓?

Pickering發布新一代低漏電流開關模塊,賦能半導體精密測試

WAT晶圓接受測試簡介

半導體測試可靠性測試設備

半導體WAT測試的常見結構

半導體WAT測試的常見結構

評論