在電子設備設計中,MOS管(金屬-氧化物-半導體場效應晶體管)因其高效率和快速開關特性被廣泛應用,但它的“脆弱性”也令人頭疼——特別是對靜電的高度敏感。這種敏感源于其內部結構:柵極與襯底間的絕緣層僅幾個納米厚,如同一層保鮮膜,一旦遭遇靜電放電(ESD),極易被擊穿,導致器件永久失效。因此,如何設計有效的靜電防護電路,成為工程師必須掌握的“必修課”。

靜電擊穿的致命威脅

靜電對MOS管的破壞主要分為兩類:一是柵極絕緣層擊穿,直接導致器件功能喪失;二是瞬態高壓引發的漏極-源極間電流沖擊,造成內部結構熔毀。例如,人體在干燥環境中行走時積累的靜電電壓可達數千伏,若直接接觸未保護的MOS管,瞬間放電能量足以讓器件“當場罷工”。更隱蔽的風險來自電路設計本身——驅動信號過快的上升時間(di/dt)可能引發寄生振蕩,加劇靜電擊穿的概率。

防護電路設計的三大核心策略

1. 從源頭隔絕靜電入侵

儲存與運輸環節是防護的第一道關卡。MOS管應封裝于導電泡沫或防靜電袋中,這類材料如同“電磁屏蔽罩”,通過內部導電網絡將靜電電荷均勻泄放,避免局部高壓聚集。在PCB組裝階段,操作人員需佩戴接地手環,工作臺鋪設防靜電桌墊,相當于為靜電搭建了一條“避雷針路徑”,將人體和設備表面的電荷導入大地。

2. 柵極保護:加裝“電壓保險絲”

柵極作為MOS管的“控制中樞”,最需重點防護。常見方案包括:

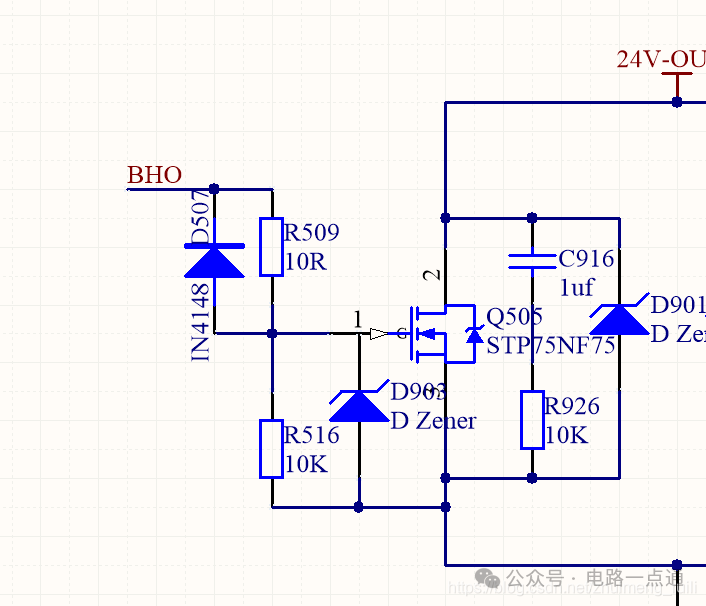

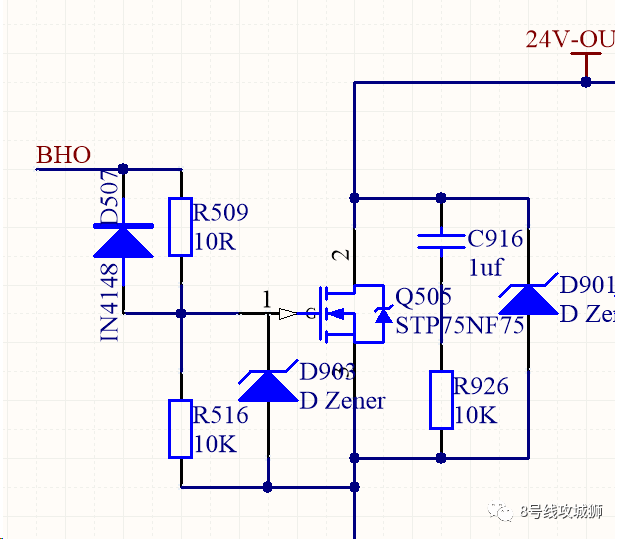

并聯齊納二極管:在柵極與源極之間接入反向擊穿電壓略低于柵極耐受值的二極管,當靜電電壓超過閾值時,二極管迅速導通泄放電荷,如同在高壓洪峰前開啟泄洪閘門。

串聯限流電阻:在驅動信號輸出端與柵極間添加10-100Ω電阻,這相當于給電流通道增設“減速帶”,既能抑制開關瞬態的高頻振蕩,又可降低靜電脈沖的峰值電流。

諾芯盛@mos管對靜電的防護電路

諾芯盛@mos管對靜電的防護電路3. PCB布局的“微觀防御體系”

電路板設計中的細節優化能顯著提升抗靜電能力:

縮短柵極走線:過長的導線會形成“天線效應”,吸收環境中的電磁干擾。將驅動電路靠近MOS管布局,可減少寄生電感,抑制電壓尖峰。

增加接地屏蔽層:在敏感信號線周圍布置接地的銅箔,形成“電磁隔離帶”,阻擋外部靜電耦合。

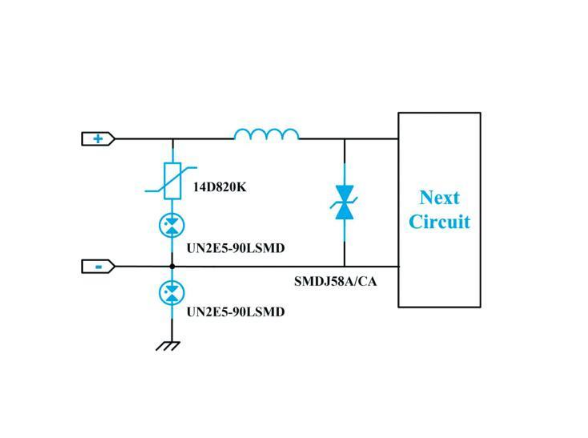

冗余設計:對高可靠性場景,可并聯多個MOS管分攤電流壓力,或增設TVS二極管(瞬態電壓抑制器)構建多級防護網絡。

驅動電路的“速度與安全平衡術”

驅動芯片直接控制MOS管的開關速度,但過快的開關會導致漏源極電壓劇烈震蕩,誘發寄生導通。例如,若驅動電阻過小,開關過程可能在納秒級完成,此時漏極電感與雜散電容形成諧振回路,產生高達數百伏的瞬態電壓。為此,工程師需通過實驗確定最優驅動電阻值——通常以開關損耗(發熱量)和電壓震蕩幅度的折中值為準。假設某電源模塊工作電壓為24V,驅動電阻選20Ω時,開關損耗可能增加5%,但電壓尖峰可從50V降至30V,顯著降低擊穿風險。

失效案例的啟示

某工業電源模塊頻繁出現MOS管炸毀,經檢測發現故障集中在倉儲環節。進一步分析顯示,未使用防靜電包裝的MOS管在搬運過程中因摩擦積累了靜電,上電瞬間柵極被擊穿。改進方案中,除更換導電包裝外,還在柵極添加了15V齊納二極管,最終將故障率從3%降至0.1%。這一案例印證了“防靜電無小事”的設計哲學——細節疏忽可能引發系統性風險。

-

靜電

+關注

關注

2文章

526瀏覽量

37229 -

MOS管

+關注

關注

109文章

2549瀏覽量

70337 -

防護電路

+關注

關注

0文章

30瀏覽量

9720

發布評論請先 登錄

mos管對靜電的防護電路

mos管對靜電的防護電路

評論