文章來源:半導體與物理

原文作者:jjfly686

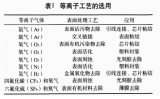

本文介紹了芯片制造中的等離子氮化工藝 。

在5納米以下的芯片制程中,晶體管柵極介質層的厚度已縮至1納米以下(約5個原子層)。此時,傳統二氧化硅(SiO?)如同漏水的薄紗,電子隧穿導致的漏電功耗可占總功耗的40%。

而解耦等離子體氮化(DPN)技術通過向氧化層精準注入氮原子,構建出一道“納米防盜網”,既堵住了電子泄漏的通道,又為芯片性能開辟新徑。

一、什么是DPN?

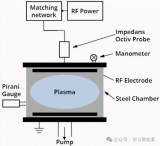

DPN(Decoupled Plasma Nitridation,解耦等離子體氮化)是一種低溫等離子體表面處理技術,核心原理是將氮原子以可控方式注入柵極氧化層,形成富氮界面。與傳統熱氮化不同,DPN的“解耦”特性體現在:

能量解耦:等離子體能量獨立控制(通常100-500W),避免高能粒子損傷硅襯底。

空間解耦:通過磁場約束等離子體,使氮原子主要富集在氧化層上表面而非硅/氧化物界面,保護載流子遷移率。

關鍵技術指標:

氮濃度:精準控制在5-10原子百分比(超過15%會引發界面缺陷)。

厚度極限:可實現≤10埃(1納米)的超薄膜處理,是5nm以下節點的必備工藝。

二、DPN工藝流程

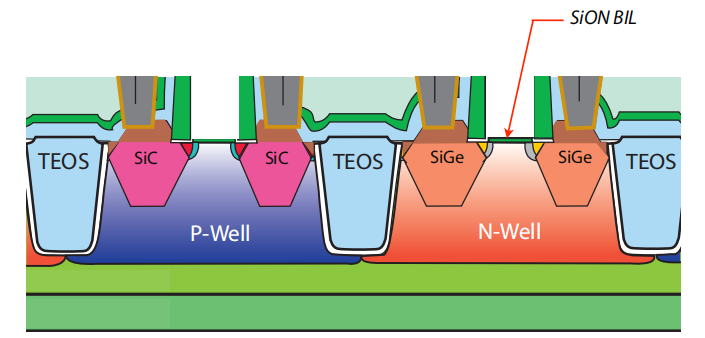

以28nm HKMG(高k金屬柵)工藝為例,DPN的關鍵步驟如下:

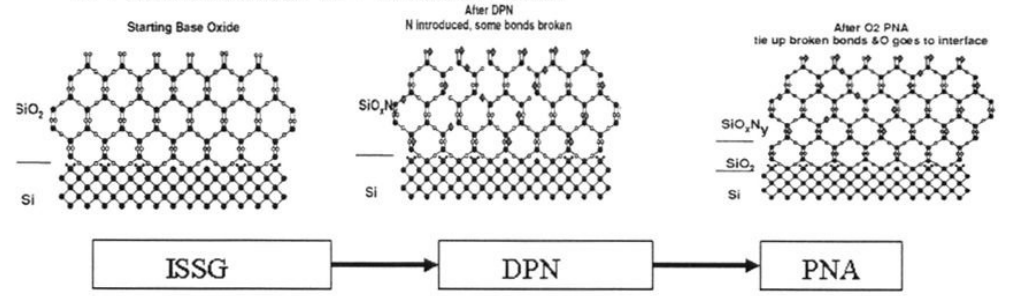

氧化層生長

在硅襯底上ISSG生長一層較薄二氧化硅層,作為氮化基底。

等離子體氮化

氣體環境:通入N?/HN3(主氣體)、Ar(稀釋氣體),壓力35-70 mTorr。等離子激活:射頻電源(200-600W)電離氣體,生成高活性氮離子(N?)。氮滲透:氮離子穿透SiO?表層,在距上表面0.5 nm內形成富氮區。

氮化后退火(PNA)

在同一真空腔體內快速退火(600-800℃),驅動氮原子均勻擴散,修復晶格損傷,并下降界面態的密度。

三、DPN在柵極氮化中的四大作用

1.提高介電常數(k值):氮原子替換SiO?中的氧原子后,形成Si-N鍵(極性高于Si-O鍵),使k值從3.9提升至4.5-7.0。同等電容下,物理厚度可增加20%,直接抑制量子隧穿效應。

2.抑制柵極漏電流:在1 nm氧化層中,DPN摻氮使漏電流從1000 A/cm2降至10 A/cm2(降低99%)。原理在于氮原子抬高了SiO?的導帶能壘,電子需更高能量才能隧穿。

3.阻擋摻雜劑擴散:PMOS柵極的硼原子易穿透SiO?導致閾值電壓漂移。氮化層如同“原子濾網”,使硼擴散系數降低103倍,保障器件長期穩定性。

4.優化界面態:通過控制氮峰值位置(距界面>0.3 nm),避免氮原子破壞硅懸掛鍵,保持電子遷移率較大。

?

-

等離子體

+關注

關注

0文章

129瀏覽量

14502 -

工藝

+關注

關注

4文章

675瀏覽量

29283 -

晶體管

+關注

關注

77文章

9989瀏覽量

140798 -

芯片制造

+關注

關注

10文章

679瀏覽量

29560

原文標題:芯片制造:DPN等離子體氮化

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導體所】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

PCB多層板等離子體處理技術

PCB電路板等離子體切割機蝕孔工藝技術

PCB板制作工藝中的等離子體加工技術

PCB多層板等離子體處理技術

微波標量反射計可測量大范圍的等離子體密度

低溫等離子體廢氣處理系統

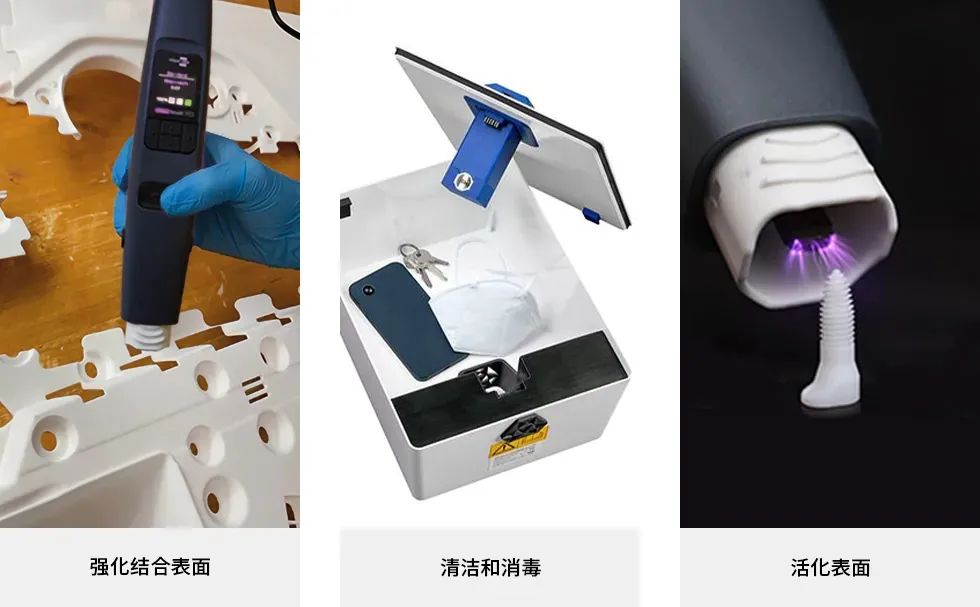

TDK|低溫等離子體技術的應用

等離子體應用

低溫等離子體技術的應用

等離子體清洗工藝的關鍵技術 等離子體清洗在封裝生產中的應用

芯片制造中解耦等離子體氮化工藝流程

芯片制造中解耦等離子體氮化工藝流程

評論