“在本文中,我將向大家展示一個結合了樹莓派Pico (RP2040) 與 Cyclone 10 FPGA 的PCB設計項目。我將解釋項目中的一些設計決策,如何準備生產所需的文件,以及如何在本次項目的贊助商NextPCB完成PCBA下單。此外,我們還將用 C 語言和 Verilog 硬件描述語言(HDL)開發一些固件,來共同“點亮”這塊板子,并玩轉它的兩個核心:RP2040 和 FPGA。話不多說,讓我們開始吧!”

目錄

- 頂層硬件/軟件架構

- RP2040+FPGA 硬件設計指南與文檔

- PCB布局、功能分區與引腳定義

- 在NextPCB + HQ-Online(華秋商城)下 PCBA 訂單

- 硬件上電(冒煙)測試與注意事項

- RP2040 GPIO測試 (LED閃爍)

- RP2040 ADC + PWM 示例

- Cyclone 10 FPGA IO 測試 (DIP開關 + LED)

- Cyclone 10 FPGA JTAG 編程

- Cyclone 10 FPGA QSPI Flash 配置測試

- 項目核心測試:RP2040 + FPGA (SPI通信)

- RP2040 + FPGA SPI 最高速度測試

- RP2040 OLED顯示示例

- 其他板載外設測試

- 總結

頂層硬件/軟件架構

首先,這個項目背后的初衷是設計一塊集成 RP2040 微控制器和低成本 FPGA 的板卡,用于實驗各種芯片間的數字通信方案,例如 SPI 總線和自定義 IO 總線(使用PIO)。

我們可以將系統設置成這樣:從 RP2040 的角度看,FPGA 是完全“透明”的,就像一個內存映射 I/O(MMIO)的外設擴展。反之,我們也可以在 FPGA 上實現一個軟核處理器,并將RP2040配置為一個從設備。這種架構非常靈活,擁有無限的應用可能。

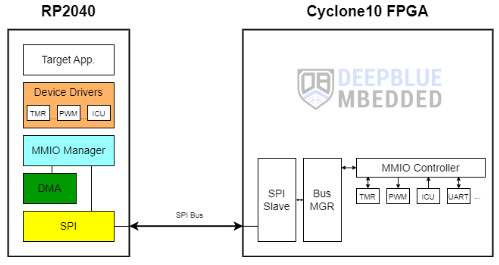

下圖展示了我們項目中要實現的目標硬件/軟件系統架構。

RP2040 側

在 RP2040 這邊,我們會使用一個主 SPI 外設來處理與 FPGA 的底層通信。在固件(軟件棧)中,我們會實現某種形式的 MMIO 尋址、IO 讀寫操作、解碼等。通過這種方式,我們可以將 MMIO 外設的尋址操作從固件的應用層中抽象出來。

然后,我們可以為 FPGA 上實現的自定義硬件外設編寫一些固件驅動程序。這樣做同樣能將自定義外設的操作細節從應用層的視角中抽象出來。

最終,使用 RP2040 微控制器自身的硬件定時器外設,和使用一個在 FPGA 上自定義設計的硬件定時器外設,體驗將幾乎沒有差別。當然,我們不會僅僅為了多幾個定時器就大費周章,但你應該能明白這個思路。

FPGA (Cyclone 10) 側

在 FPGA 這邊,我們將實現一個硬件從 SPI 外設來處理與 RP2040 的通信。然后,我們會將接收到的數據傳遞給一個自定義的總線管理器,該管理器內部應包含某種狀態機,用于編解碼傳入/傳出的 SPI 數據。在這一步,串行的 SPI 數據將被轉換為并行的總線數據/控制信號。

接著,我們會連接一個 MMIO 控制器,它負責控制自定義外設的內存 IO 操作,并標準化每個自定義外設的掛載方式。這使得系統更具擴展性和可移植性。

同樣,這也只是系統工作方式的一個例子。它當然也可以將 SPI 總線橋接到 AXI-4/AXI-Lite 總線,以便掛載軟核處理器或標準的硬件 IP 核,可能性還有很多。

RP2040-FPGA 芯片間連接

RP2040 微控制器和 Cyclone 10 FPGA 芯片之間有兩條總線連接:

-

SPI 總線 (4線)

使用 SPI 總線,我們可以利用 RP2040 的硬件外設與 FPGA 進行高速通信(最高可達62.5Mbps)。我們還可以通過 RP2040 內部的 DMA 單元實現批量數據傳輸,從而極大地減少 CPU 的干預。

-

自定義IO總線 (4線)

利用 RP2040 獨特的 PIO(可編程I/O),我們可以輕松實現任何自定義的數字通信協議,以達到非常高的數據傳輸速度。這為未來的無限可能性和實驗敞開了大門。

硬件設計指南與文檔

在設計這樣的系統時,官方文檔和指南是我們最好的朋友。Intel/Altera提供了許多非常有用的文檔,我在設計這塊板子時都用到了,包括:

- Cyclone 10 LP 器件數據手冊

- Cyclone 10 LP 設計指南

- Cyclone 10 LP (10CL006) 引腳信息

RP2040 也是如此,樹莓派官網上有幾份很有幫助的文檔:

- RP2040 參考手冊

- RP2040 硬件設計指南

- 樹莓派 Pico 數據手冊

你也可以參考我之前關于 RP2040 的項目,它演示了如何圍繞 RP2040 微控制器設計自定義 PCB 板,我在這個項目中也完全沿用了那部分設計。

https://deepbluembedded.com/raspberry-pi-pico-rp2040-schematic-pcb-design-in-kicad/

PCB 布局、功能分區與引腳定義

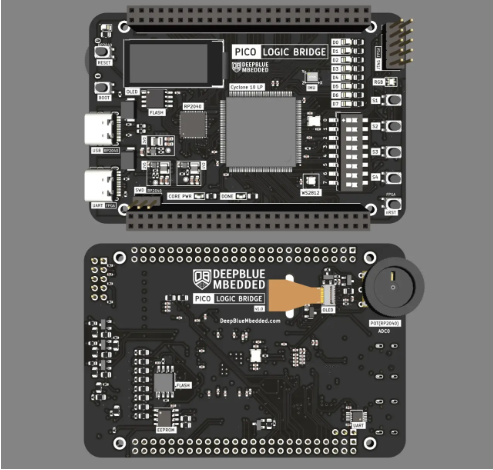

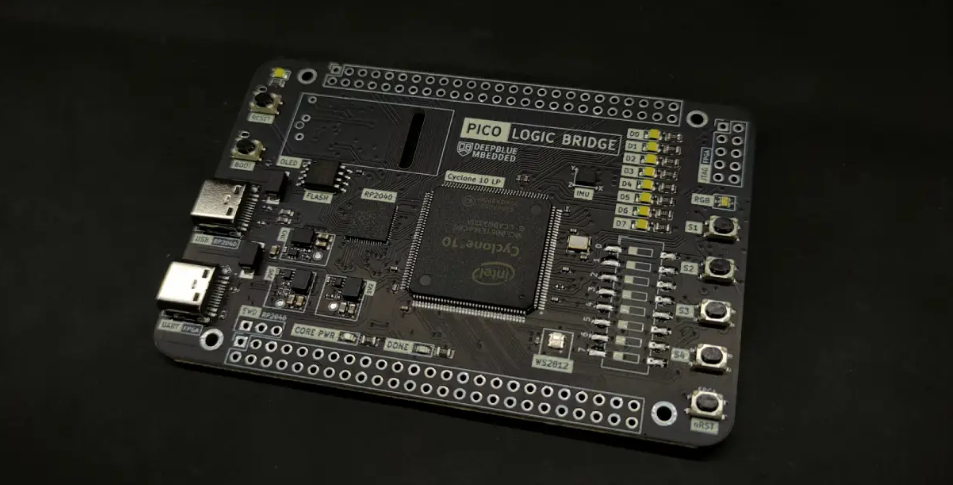

這是板子在KiCAD 3D視圖中的頂層和底層布局。我特意將所有東西按邏輯分區,并保持其易用性。在 CAD 軟件里看起來很大的 PCB,現實中很容易變得笨拙難用。我盡力將用戶需要交互的元件放在易于觸及和操作的位置。

板子尺寸為:6cm x 9cm(它非常小,不像在CAD軟件里看起來那么大)

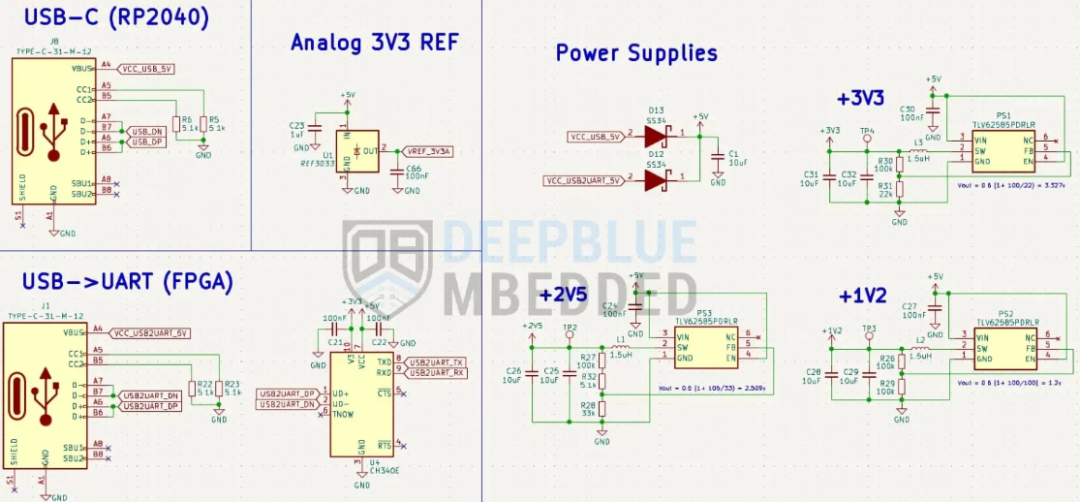

板上有兩個 USB-C 接口,一個用于電源輸入(+5V)和 RP2040 的 USB 通信(UF2燒錄程序時需要),另一個 USB 口連接到一個 USB 轉 UART 橋接芯片,通往FPGA。

2. 電源 (穩壓器)

板上有三個 DC/DC 降壓轉換器和一個模擬電壓參考,它們分別是:

- +3V3 (FPGA+RP2040 Vcc)

- +1V2 (FPGA Core)

- +2V5 (FPGA Aux.)

- +3.3VA (REF3033)

3. RP2040 MCU電路 + QSPI FLASH

RP2040 微控制器需要 +3.3V 的 IOVdd 輸入電壓、內部穩壓器提供的 +1.1V 核心電壓、100nF 的去耦電容和一個 12MHz 的晶體振蕩器。

與市面上大多數微控制器不同,RP2040 沒有內置閃存,因此需要一個外部 QSPI 閃存芯片。你可以選擇2MB、4MB、8MB或16MB的閃存。

在我的板子上,我使用了 RP2040 的 XIP(eXcute-In-Place)接口所允許的最大閃存容量:16MB(128Mbit)。

我還增加了一個RESET按鈕,以及用于UF2編程的BOOT按鈕。

4. Cyclone 10 LP (10CL006) FPGA電路

FPGA 芯片有很多 Bank 和特殊功能的 IO 引腳,需要按照 Intel/Altera 官方文檔中詳細說明的方式進行連接。

VCCIO、VCCA 和 VCCINT 引腳都按數據手冊建議連接。MSEL[2:0] =ASx1(Active Serial) 模式允許 FPGA 從一個 SPI 串行閃存芯片加載配置比特流。我使用了一個64Mbit的QSPI閃存芯片。

我用作 FPGA 主時鐘源的 CMOS 振蕩器是一個50MHz的振蕩器。當然,我們可以利用 FPGA 內部的2個PLL單元來調整這個頻率(這款FPGA的PLL最高可達400MHz)。

5. RP2040 板載外設

連接到RP2040微控制器的板載外設有:

6. FPGA 板載外設

連接到Cyclone 10 LP FPGA的板載外設有:

- 8個 DIP 開關

- 8個 LED

- 4個按鍵

- 1個模擬 RGB (PWM) LED

- 1個 NeoPixel RGB (WS2812) LED

- 1個 64kBit I2C EEPROM芯片 (24C64)

7. IO端口

板上有4組排針端口:

- 2x (25x2) IO 排針: RP2040 = 15個 IO, FPGA = 41個IO

- 1x FPGA JTAG 排針

- 1x RP2040 SWD 排針

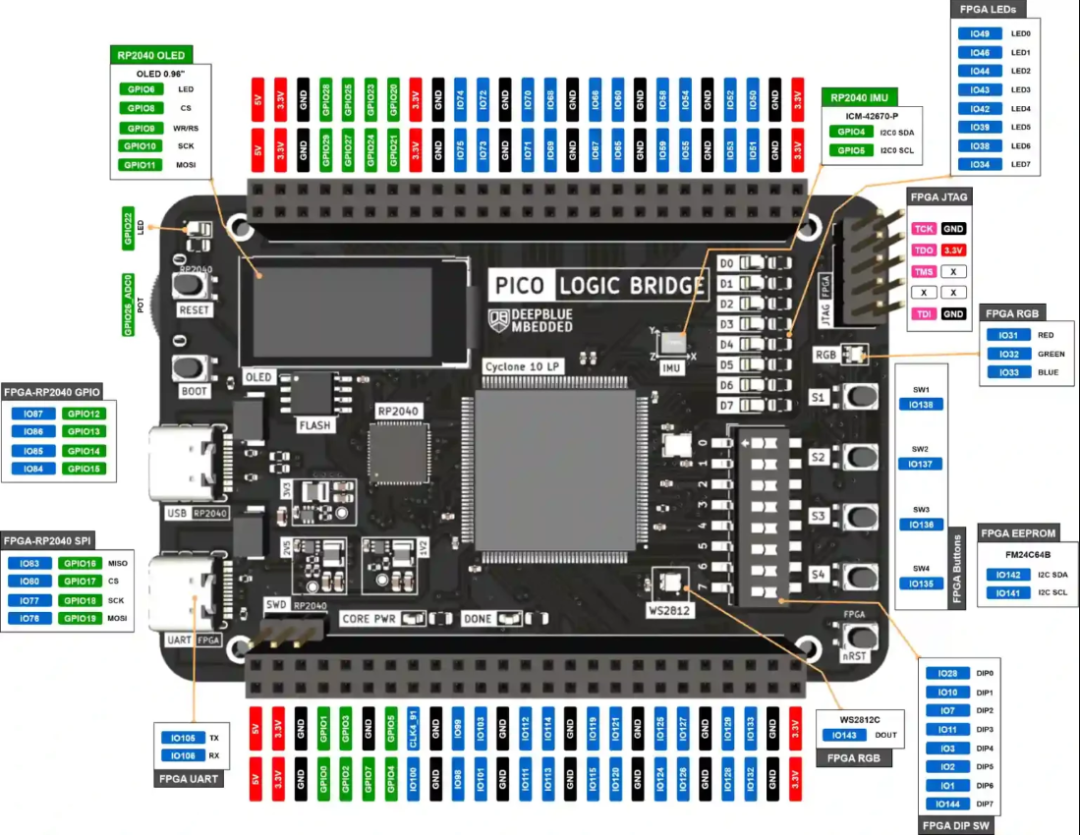

RP2040+FPGA 板引腳定義圖

這是我們項目板卡的引腳定義圖。

在 @NextPCB 上下單

可以在網頁上下單,也可以使用 KiCad 的插件:

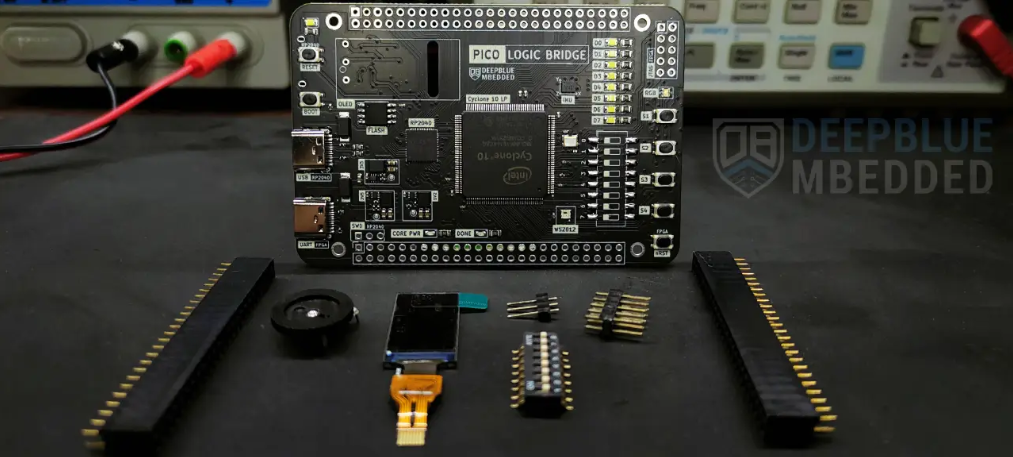

到貨了!

硬件上電(冒煙)測試與注意事項

首先,我需要手動焊接/安裝一些直插元器件。

然后,我用顯微鏡和“Fine Needle”萬用表探頭快速檢查,確保關鍵電源網絡沒有短路,并檢查關鍵電源路徑(VCC, VCCINT, VCCA等)的導通性。

一切看起來都很完美。下一步,我從我的“限流”電源上給板子通電(+5V/50mA)。這樣做是為了以防萬一,即使有問題,也不會有足夠大的電流造成嚴重損壞。謝天謝地,它完美地工作了起來,只消耗了幾個毫安的電流。

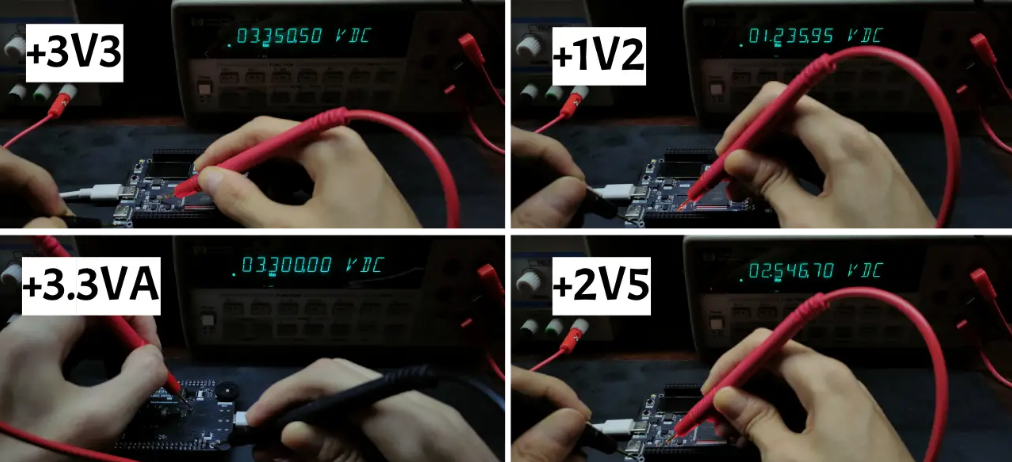

以下是實際測量的電源電壓:

到這一步,我信心十足地插上了 USB 線,準備開始真正的測試工作!

RP2040 GPIO 測試 (LED閃爍)

這是第一個“RP2040測試”示例,我們將閃爍板載的 LED 燈。編譯固件并使用 UF2 引導加載程序將其燒錄到板子上。

測試結果:LED成功閃爍!

RP2040 ADC + PWM 示例

接下來,我們測試 RP2040 的 ADC。通過讀取板載的模擬旋轉電位器的值,然后用它作為占空比控制信號,來調節板載 LED 的亮度。

測試結果:轉動電位器,LED亮度平滑變化。

Cyclone 10 FPGA IO測試 (DIP開關 + LEDs)

這是第一個“FPGA測試”示例。我將 8 個 DIP 開關通過 FPGA 內部連接到 8 個 LED,用開關控制燈的狀態。同時,將 3 個按鍵連接到 RGB LED 的紅、綠、藍引腳。這是一個非常基礎的測試,用來驗證 FPGA 至少能正常工作,并能接收比特流文件來執行相應的功能。

測試結果:開關和按鍵都能正確控制對應的LED。

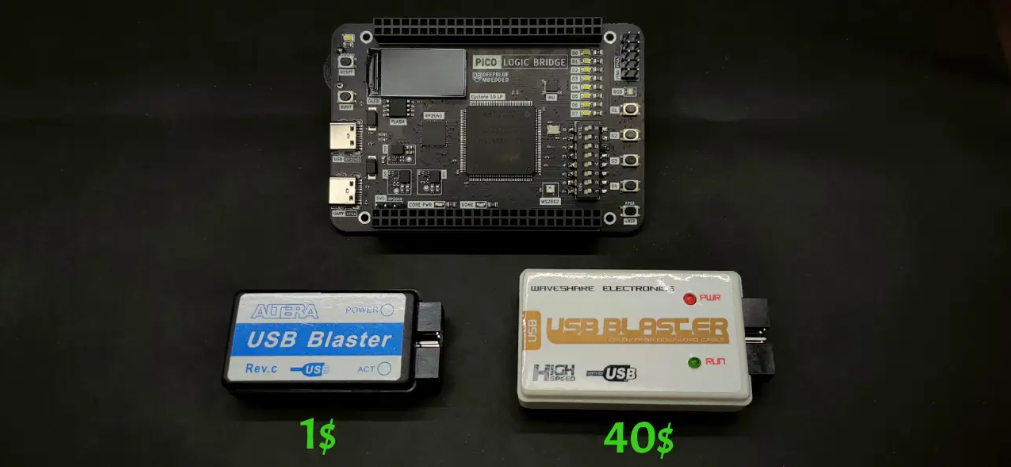

Cyclone 10 FPGA JTAG 編程

為了將比特流加載到我的 Cyclone 10 FPGA 上,我嘗試了市面上常見的兩種 Altera USB Blaster。由于我使用的是最新版本的 Quartus Prime(精簡版),所以 Waveshare USB Blaster v2 對我來說比較好用。

不過,便宜的 USB Blaster 也能用,電腦也能檢測到,驅動程序也能安裝,一切正常。但它在我這里沒有出現在 Quartus Prime 軟件中。也許它在舊版本的軟件包下能用。

Cyclone 10 FPGA QSPI Flash 配置測試

在之前的示例中,只要按下復位按鈕或斷電,FPGA的 配置(比特流)就會丟失。因此,我們需要測試 QSPI Flash 的配置功能。我將比特流準備成JIC(JTAG間接配置)文件格式,然后通過JTAG連接將其燒錄到QSPI存儲器中。

這將使我們的FPGA設計永久存儲在QSPI閃存中,并在上電或按下復位按鈕后自動加載。

測試結果:斷電重啟后,FPGA 成功加載了之前的配置,功能恢復正常。

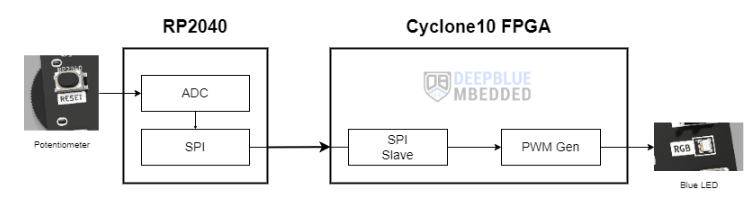

項目核心測試:RP2040 + FPGA (SPI通信)

現在,我們來進行真正的核心測試。在這個例子中,我們將實現:

- RP2040固件(C語言): RP2040 將使用 ADC 讀取模擬電位器的值,將其從12位縮放到8位,然后通過 SPI 發送給 FPGA 芯片。

- Cyclone10 FPGA HDL(Verilog): 在 FPGA 上,我們將創建一個硬件 SPI 從機模塊和一個 PWM 生成器。每當 SPI 從機設備接收到一個字節的數據,它就會被鎖存并加載到 PWM 的占空比控制寄存器中。PWM 的輸出將連接到板載 RGB 的藍色 LED。

因此,RP2040的電位器將控制 FPGA 的 PWM 輸出,進而控制 RGB 上藍色 LED 的亮度。我們將 SPI 通信速度設置為1Mbps以確保一切正常,然后再逐步提高速度。

測試結果:完美實現!轉動電位器,藍色LED的亮度隨之變化。

RP2040 + FPGA SPI 最高速度

在對系統在 1Mbps SPI 速度下的性能充滿信心后,我開始逐漸提高 SPI 通信速度。當速率達到 30Mbps 時,通信開始出錯,這是因為我的 FPGA 使用的是板載的原始 50MHz 時鐘源。

因此,我啟用了 FPGA 內部的一個PLL單元,將時鐘“泵”到 30Mbps,并將該時鐘提供給我所有的HDL模塊(尤其是SPI從機)。這樣做之后,我們就可以在62.5Mbps 的速率下輕松維持穩定的 SPI 通信,這也是 RP2040 在 125MHz 系統時鐘下運行時的最高 SPI 速度。

這對我來說簡直太棒了!因為我在網上看到很多關于 SPI 線路端接以及在速度超過 30MHz 時會出現問題的討論。而我沒有使用任何并行或串聯端接電阻,只是遵循了信號完整性的通用布線最佳實踐。

RP2040 OLED 顯示示例

在結束本項目之前,最后一個示例演示是板載 0.96 英寸 OLED RGB 顯示屏。以下是一段演示視頻,展示了一些存儲在 RP2040 上并在 OLED 屏幕上顯示的圖像。

額外的電路板外設測試

鑒于這是該硬件設計 PCB 項目的首次迭代。目前,所有測試都按預期運行,沒有任何問題。這已經是一個很大的成功了!

如果其他輔助外設也能正常工作,那將是額外的勝利。剩余未測試的外設包括:

-

IMU (ICM-42670) – [RP2040]

-

I2C EEPROM (24C64) – [FPGA]

-

Neopixel RGB (WS2812) LED – [FPGA]

我沒有時間為上述部件開發一些設備驅動程序,但我相信它們也能正常工作。

總結

通過這個項目,我希望你覺得它對你有幫助、有啟發,或者至少覺得它很有趣。我有很多想用這塊板子做的實驗,特別是微控制器和 FPGA 之間的數字通信。我將盡力記錄后續的工作,并希望能在我們的油管頻道上分享一些內容,敬請關注。

如果你有任何問題,或者希望我用這塊板子做一個特定的應用,甚至是用不同的規格(FPGA、MCU、傳感器、外設等)創造一塊新板子,歡迎在評論中告訴我。我很樂意聽聽你的看法。

以下是油管的完整項目視頻鏈接:

https://youtu.be/bl_8qcS0tug

本文轉載自:https://deepbluembedded.com/rp2040-cyclone-10-fpga-pcb-design-project/,經過翻譯、校對

-

FPGA

+關注

關注

1643文章

21981瀏覽量

614539 -

PCB設計

+關注

關注

396文章

4788瀏覽量

89369 -

Cyclone

+關注

關注

0文章

55瀏覽量

30440 -

樹莓派

+關注

關注

121文章

1956瀏覽量

107037 -

KiCAD

+關注

關注

5文章

239瀏覽量

9354

發布評論請先 登錄

【干貨分享】RP2040 + Cyclone 10 FPGA PCB 設計

基于XIAO RP2040和樹莓派的圍棋棋盤游戲系統設計

樹莓派!干農活!

小身材,大能量:你玩過樹莓派掌機嘛?

樹莓派 Pico SDK 2.1.1 版本發布!

矽遞科技XIAO RP2040開發板的Arduino開發環境配置教程

項目分享:樹莓派Pico (RP2040) + Cyclone 10 FPGA PCB 設計

項目分享:樹莓派Pico (RP2040) + Cyclone 10 FPGA PCB 設計

評論