獨熱碼在狀態機里面使用比價廣泛,這一塊有些人愛用,有些人嫌煩,有時候可以用用格雷碼跳轉,不過格雷碼只支持那種一步到底的,中間有分支就不好做了,所以后來還是回到了獨熱碼的正道上。

說白了獨熱碼的使用,在對狀態判斷時,會減少一級組合邏輯,關鍵路徑上少一步,乍看沒多少,用多了積累多了,還是一個很客觀的數據的。

然后三段式狀態機,狀態跳轉時一定記得要加上default,避免latch的產生。為了防止有時候不記得,在寫狀態機時不如上來就給其他情況先賦值。

調試技巧

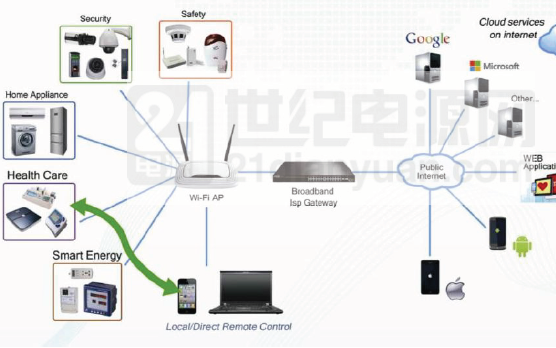

FPGA設計,需要以數據流來推動,因此統計數據流輸入和輸出的個數,對于調試來說,是一個最方便也最直觀的方式。

這些計數,設計者可以通過總線接口供外部處理器讀出。不需要占用大量邏輯資源去調用邏輯分析儀,就可以通過處理器的串口連接計算機打印出來。

調試過程中,如果發現某些模塊有輸入卻沒輸出,或者是輸入個數與輸出個數不匹配,打印出所有計數,就可以很快定位出問題出現的位置。然后有的放矢,很快就可以找出該模塊的問題所在。

通過FPGA內部各模塊的關鍵計數分析,來定位分析問題,在設計上沒有任何難度。不過需要外部CPU或者FPGA嵌入式CPU的配合使用。

-

FPGA

+關注

關注

1643文章

21968瀏覽量

614295 -

Default

+關注

關注

0文章

4瀏覽量

8191 -

Latch

+關注

關注

1文章

48瀏覽量

16361

原文標題:與FPGA相關的獨熱碼

文章出處:【微信號:ALIFPGA,微信公眾號:FPGA極客空間】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

為什么相對于格雷碼來說,獨熱碼會使用更多的觸發器和更少的組合邏輯???

fpga Default Latch FPGA設計的獨熱碼的使用和調試技巧的詳細概述

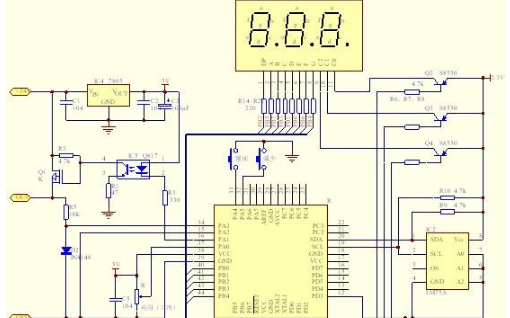

基于單片機及FPGA的時碼終端系統

IIC調試的詳細中文資料概述

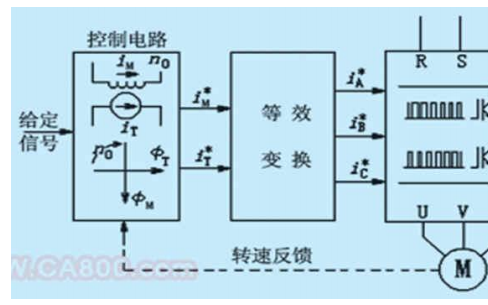

VFD-V變頻器功能碼詳細說明詳細中文資料概述

SOPC和FPGA的介紹和基礎實驗的詳細資料概述

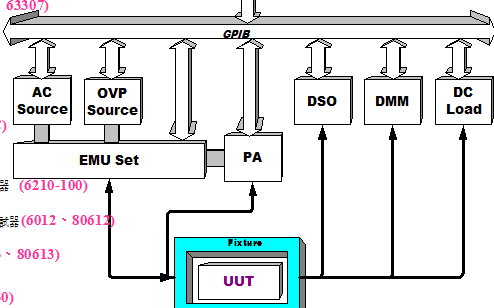

Chroma8000自動測試系統的介紹和ATE調試操作流程詳細概述

基于FPGA的IRIGBDC碼解碼

FPGA設計的獨熱碼的使用和調試技巧的詳細概述

FPGA設計的獨熱碼的使用和調試技巧的詳細概述

評論