概述

MAX9218數(shù)字視頻串/并轉(zhuǎn)換器在數(shù)據(jù)和控制周期對(duì)總共27位數(shù)據(jù)解串。在數(shù)據(jù)周期,LVDS串行輸入被轉(zhuǎn)換為18位并行視頻數(shù)據(jù),在控制周期,輸入被轉(zhuǎn)換為9位并行控制數(shù)據(jù)。分開的視頻和控制周期充分利用視頻時(shí)序來降低串行數(shù)據(jù)速率。MAX9218與MAX9217串行器組成一個(gè)完整的數(shù)字視頻傳輸系統(tǒng)。

專用數(shù)據(jù)解碼降低EMI并提供DC平衡。DC平衡允許使用AC耦合,為發(fā)送和接收之間提供隔離。MAX9218具有可選的上升沿或下降沿輸出鎖定。

ESD容限符合ISO 10605的±10kV接觸放電和±30kV氣隙放電規(guī)范。

MAX9218內(nèi)核電壓為+3.3V,獨(dú)立輸出電源可實(shí)現(xiàn)與1.8V至3.3V邏輯電平接口。該器件可提供48引腳薄型QFN和LQFP封裝,可用于-40°C至+85°C工作溫度范圍。

數(shù)據(jù)表:*附件:MAX9218 27位、3MHz至35MHz、直流平衡、LVDS解串器技術(shù)手冊(cè).pdf

應(yīng)用

- 車載娛樂系統(tǒng)

- LCD顯示器

- 導(dǎo)航系統(tǒng)顯示器

- 攝像機(jī)

特性

- 專用數(shù)據(jù)解碼實(shí)現(xiàn)DC平衡并降低EMI

- 視頻消隱期間解串控制數(shù)據(jù)

- 5位控制數(shù)據(jù)輸入為一位的誤差容限

- 輸出轉(zhuǎn)換時(shí)間根據(jù)工作頻率調(diào)整以降低EMI

- 輸出分組轉(zhuǎn)換以降低EMI

- 輸出使能允許使用輸出總線

- 鎖定時(shí)時(shí)鐘脈沖延展

- 寬至±2%的參考時(shí)鐘容限

- 無需外部控制即可與MAX9217串行器同步

- ISO 10605 ESD保護(hù)

- 獨(dú)立輸出電源實(shí)現(xiàn)與1.8V至3.3V邏輯接口

- +3.3V內(nèi)核電源

- 節(jié)省空間的薄型QFN和LQFP封裝

- -40°C至+85°C工作溫度范圍

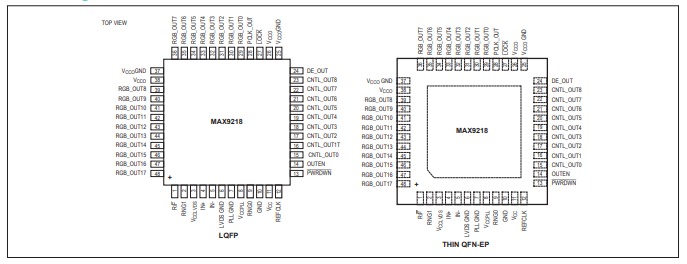

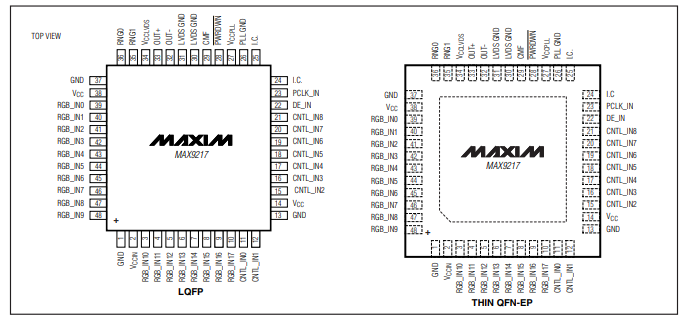

引腳配置描述

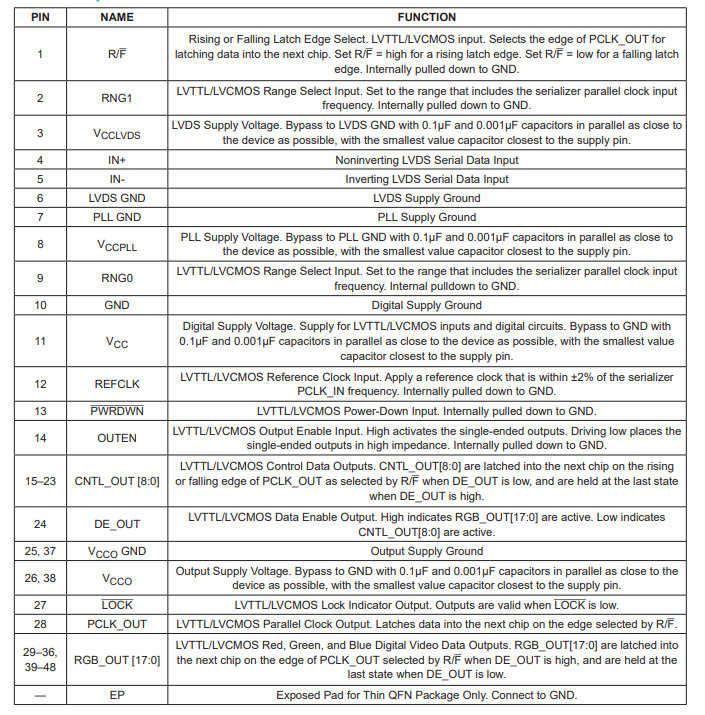

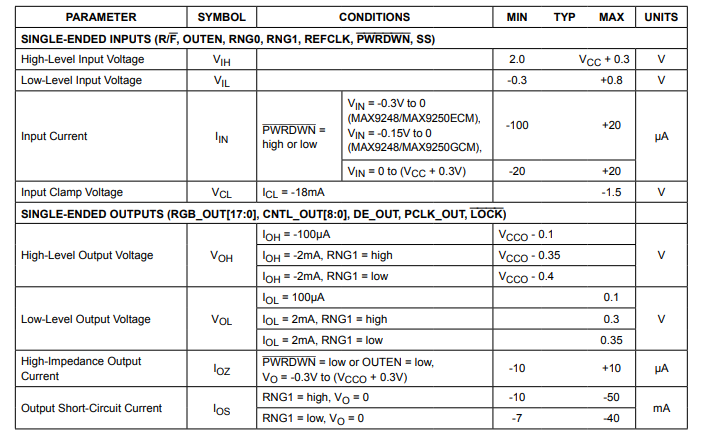

DC電氣特性

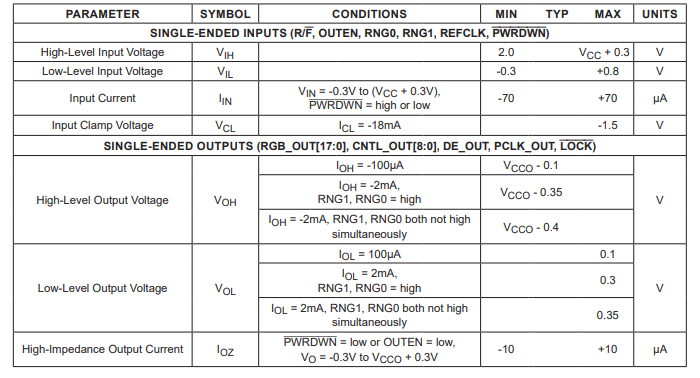

典型操作特性

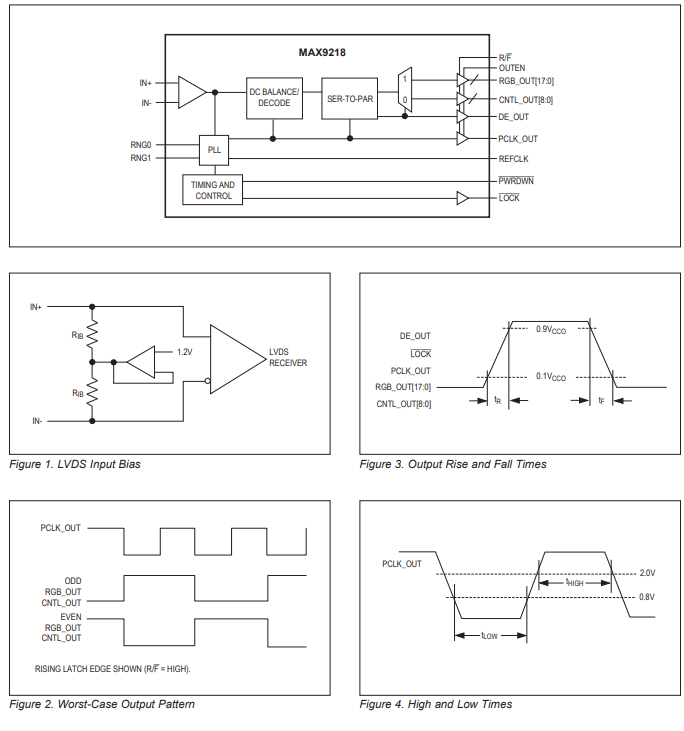

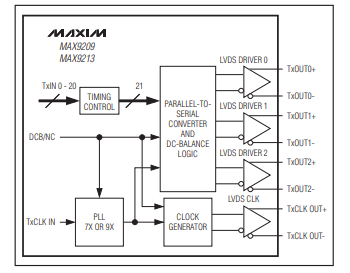

框圖

詳細(xì)說明

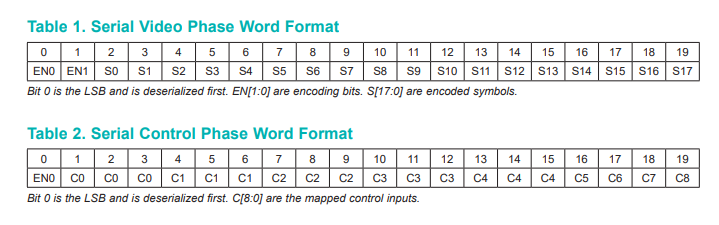

MAX9218直流平衡型解序列化器的并行時(shí)鐘頻率為7MHz至35MHz,對(duì)視頻數(shù)據(jù)進(jìn)行解序列化以輸出RGB_OUT[17:0],當(dāng)數(shù)據(jù)使能輸出DE_OUT為高電平時(shí)進(jìn)行輸出,或在控制數(shù)據(jù)時(shí)輸出CNTL_OUT[8:0],當(dāng)DE_OUT為低電平時(shí)進(jìn)行輸出。視頻數(shù)據(jù)字是對(duì)解碼后的開銷比特、EN0和EN1進(jìn)行解碼得到的。控制階段編碼字通過最大似然法進(jìn)行解碼,同時(shí)進(jìn)行誤碼檢測(cè)。由MAX9217序列化器執(zhí)行的EN0編碼可減少電磁干擾(EMI),并在直流平衡的情況下維持電纜長(zhǎng)度。串行輸入字格式見表1和表2。

控制數(shù)據(jù)輸入C0至C4,在每個(gè)串行比特時(shí)間內(nèi)由序列化器重復(fù)三次,使用多數(shù)表決法進(jìn)行解碼。通過三個(gè)比特中的兩個(gè)或三個(gè)處于相同狀態(tài)來確定恢復(fù)比特的狀態(tài),從而提供單比特誤碼容限。C0至C4的狀態(tài)由比特自身的電平?jīng)Q定(不使用表決法),C5由其自身電平?jīng)Q定(不使用表決法)。

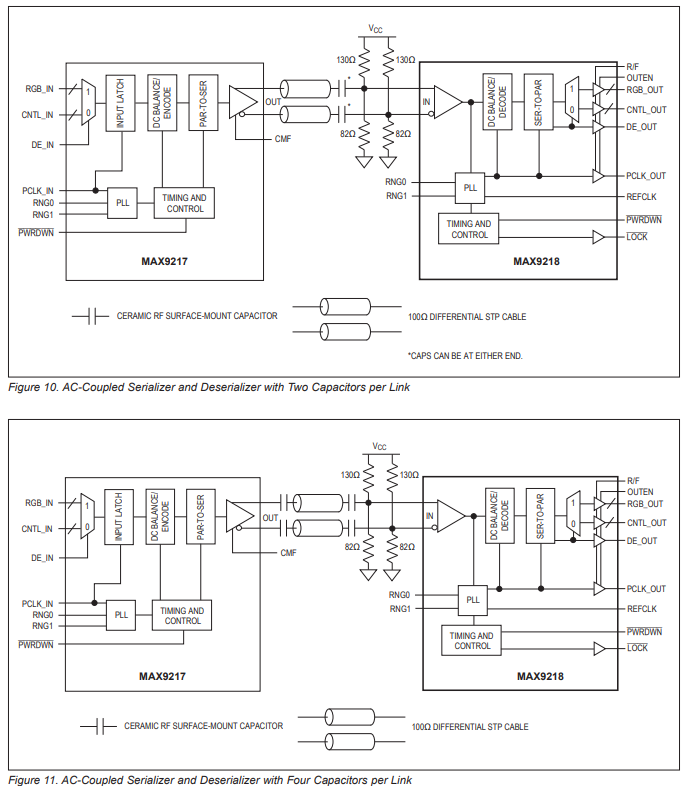

交流耦合優(yōu)勢(shì)

交流耦合將LVDS接收器的輸入電壓提升至電容的額定電壓。兩個(gè)電容就足以實(shí)現(xiàn)隔離,在序列化器輸出端和/or 解序列化器輸入端各放置一個(gè),以防止電纜短路時(shí)出現(xiàn)高電壓。交流耦合可阻斷低頻地電位偏移和共模噪聲。MAX9217序列化器也可與MAX9218解序列化器直流耦合。圖10展示了帶有兩個(gè)電容的交流耦合序列化器,圖11展示了每條鏈路帶有四個(gè)電容的交流耦合解序列化器。

應(yīng)用信息

交流耦合電容的選擇

有關(guān)根據(jù)并行時(shí)鐘頻率計(jì)算交流耦合電容值的內(nèi)容,見圖12。該圖展示了每條鏈路使用兩個(gè)和四個(gè)電容的系統(tǒng)的電容值。對(duì)于時(shí)鐘頻率低于18MHz的應(yīng)用,使用0.1μF的電容。

端接和輸入偏置

IN+和IN- LVDS輸入在內(nèi)部通過35kΩ(最小)電阻連接到+1.2V,為交流耦合(圖1)提供偏置。假設(shè)為100Ω互聯(lián),LVDS輸入可以用100Ω電阻進(jìn)行端接,以匹配差分互聯(lián)的阻抗。

在噪聲環(huán)境中的交流耦合鏈路上,采用戴維南端接來提供1.2V偏置。對(duì)于100Ω差分阻抗的互聯(lián),將每個(gè)LVDS線從VCC通過130Ω電阻上拉,并從地到解序列化器輸入下拉820Ω電阻(圖10和圖11)。此端接在差分模式和共模模式下均提供1.2V偏置。戴維南端接的阻抗應(yīng)為互聯(lián)差分阻抗的一半,并提供1.2V的偏置電壓。

-

lvds

+關(guān)注

關(guān)注

2文章

1112瀏覽量

67098 -

解串器

+關(guān)注

關(guān)注

1文章

133瀏覽量

13992 -

MAX9218

+關(guān)注

關(guān)注

0文章

6瀏覽量

7722

發(fā)布評(píng)論請(qǐng)先 登錄

瑞盟 MS9218 數(shù)字視頻串/并轉(zhuǎn)換器在數(shù)據(jù)和控制周期對(duì)總共 27 位數(shù)據(jù)解串

MAX9218 pdf

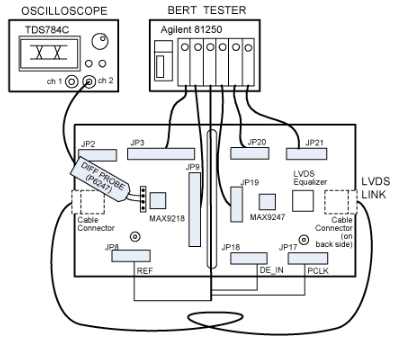

配合MAX9217/MAX9218/MAX9247/MAX9

配合MAX9217/MAX9218/MAX9247/MAX9

MAX9217/MAX9218 視頻鏈路中的音頻數(shù)據(jù)傳輸

MAX9217/MAX9218 視頻鏈路中的音頻數(shù)據(jù)傳輸

MAX9247/MAX9218串行器/解串器芯片組的性能測(cè)試

串行器和解串器對(duì)的性能測(cè)試:MAX9247和MAX9218

MAX9247/MAX9218串行器/解串器芯片組的性能測(cè)試

配合MAX9217/MAX9218/MAX9247/MAX9248/MAX9250評(píng)估板工作

DS90C124,DS90C241 5MHz至35MHz DC平衡24位FPD-Link Il串行器和解串器數(shù)據(jù)表

MAX9248/MAX9250 27位、2.5MHz至42MHz、直流平衡、LVDS解串器技術(shù)手冊(cè)

MAX9217 27位、3MHz至35MHz、直流平衡、LVDS串行器技術(shù)手冊(cè)

MAX9209/MAX9213可編程、直流平衡、21位串行器技術(shù)手冊(cè)

MAX9218 27位、3MHz至35MHz、直流平衡、LVDS解串器技術(shù)手冊(cè)

MAX9218 27位、3MHz至35MHz、直流平衡、LVDS解串器技術(shù)手冊(cè)

評(píng)論