1. PECL接口

PECL 由ECL 標準發展而來,但在PECL 電路中使用的是正電源。PECL 信號的擺幅相對ECL 要小,這使得該邏輯更適合于高速數據的串行或并行連接。PECL 標準最初由Motorola 公司提出,經過很長一段時間才在電子工業領域推廣開。

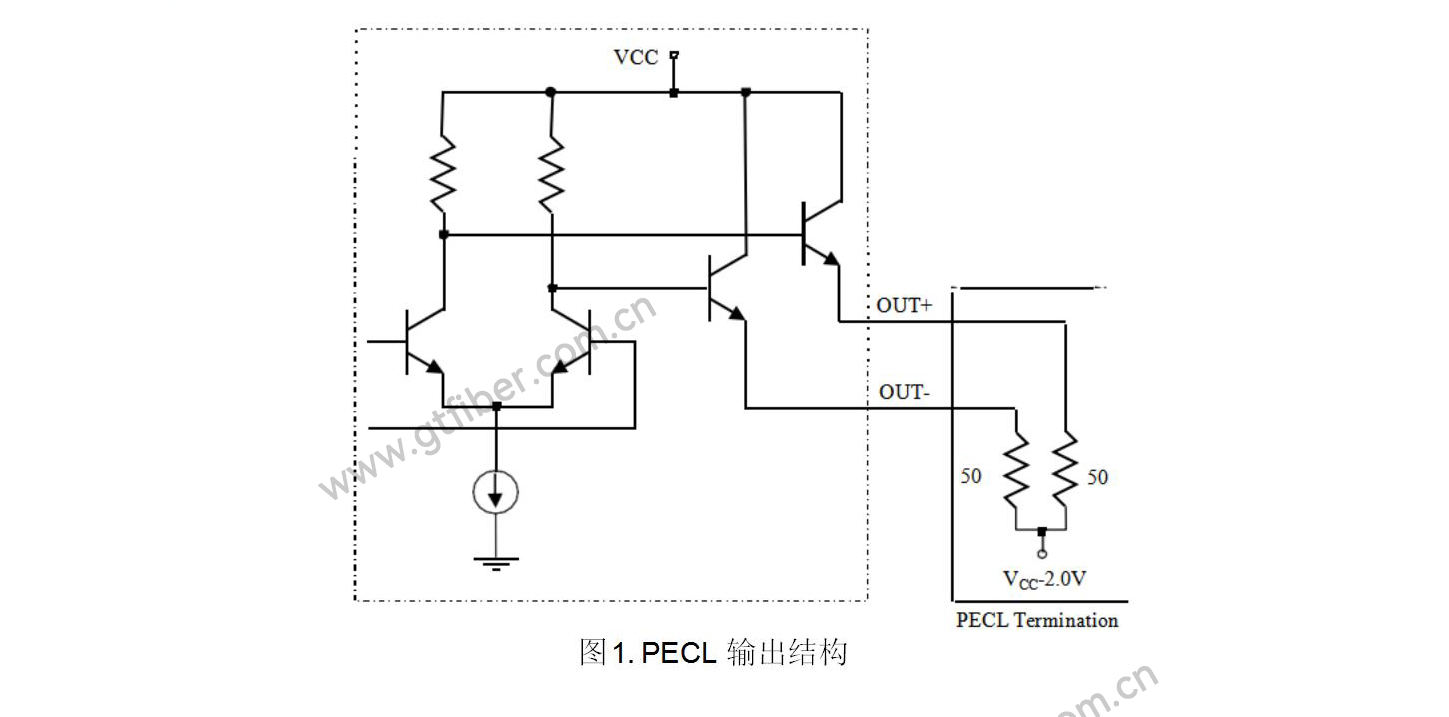

1.1 PECL輸出結構

PECL 電路的輸出結構如圖1 所示,包含一個差分對管和一對射隨器。輸出射隨器工作在正電源范圍內,其直流電流始終存在,這樣有利于提高開關速度,保持較快的關斷時間。PECL 輸出的適當端接是連接50? 電阻至(VCC-2V)電平。在這種端接條件下,OUT+與OUT-的典型值為(VCC-1.3V),輸出直流電流約為14mA。PECL 結構的輸出阻抗很低,典型值約為(4-5)?,這表明它有很強的驅動能力。但當負載與PECL 的輸出端之間有一段傳輸線時,低阻抗造成的背向端接失配將導致信號的高頻失真。

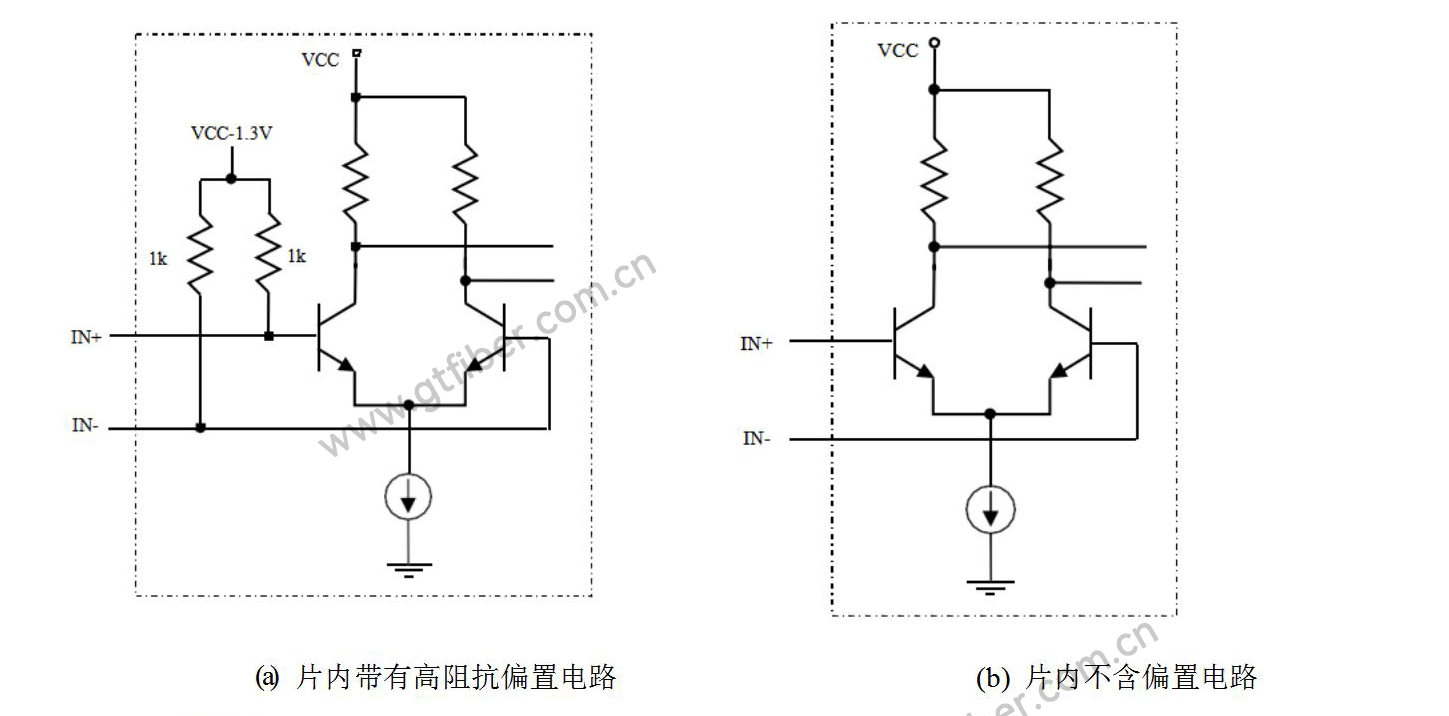

1.2 PECL輸入結構

PECL 輸入結構如圖2 所示,它是一個具有高輸入阻抗的差分對。該差分對共模輸入電壓需偏置到(VCC-1.3V),這樣允許的輸入信號電平動態范圍最大。

2.CML接口

CML 是所有高速數據接口形式中最簡單的一種,片內輸入與輸出端接減少了設置工作條件所需的外圍器件數量。CML 輸出所提供的信號擺幅較小,從而功耗更低。此外,50? 背向終端匹配減小了背向反射,從而降低了高頻失真。

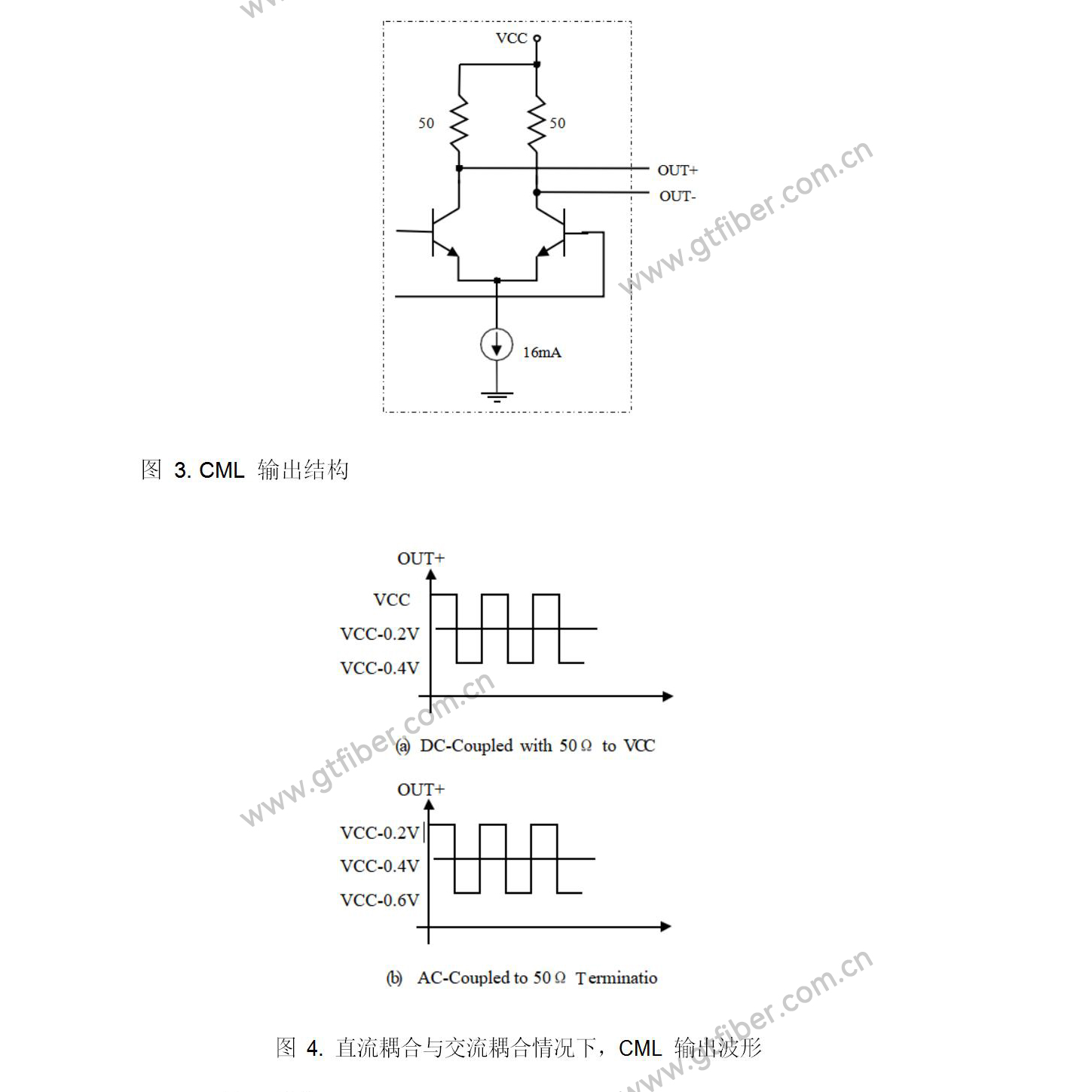

2.1 CML輸出結構

CML 的輸出電路形式是一個差分對管,該差分對的集電極電阻為50?,如圖3 所示。輸出信號的高低電平切換是靠共發射極差分對管的開關控制的。假定電流源的典型值為16mA,CML 輸出負載為上拉至VCC的50? 電阻,則單端CML 輸出信號的擺幅為VCC至(VCC-0.4V)。在這種情況下,CML 差分輸出信號擺幅典型值為800mV,共模電壓為(VCC-0.2V)。對同一個電流源來說,若CML 輸出采用交流耦合至50? 負載,這時的直流阻抗由50? 集電極電阻決定。CML 輸出共模電壓變為(VCC-0.4V) ,差分信號擺幅仍為800mV PP 。在交流和直流耦合情況下輸出波形如圖4 所示。

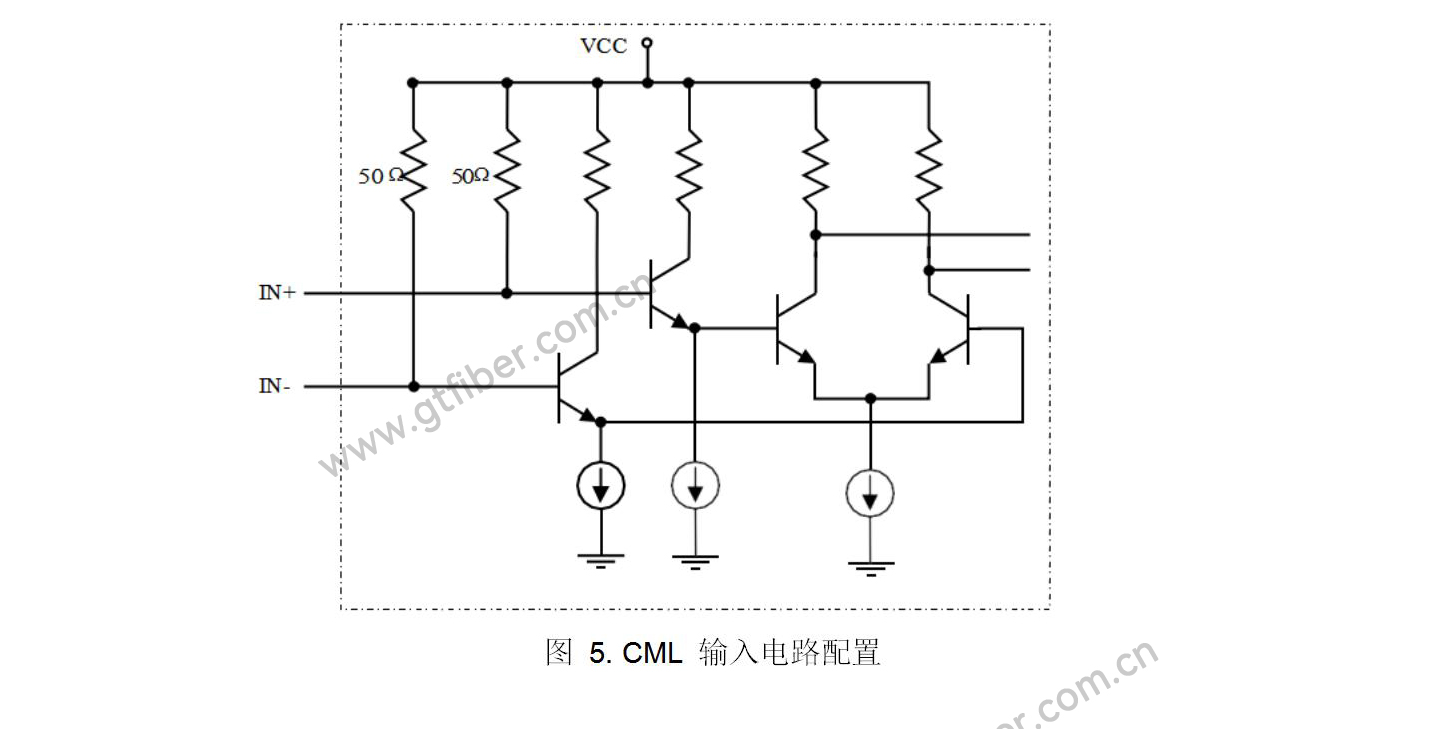

2.2 CML輸入結構

CML 輸入結構有幾個重要特點,這也使它在高速數據傳輸中成為常用的方式。如圖5 。

圖5. CML 輸入電路配置

3. LVDS****接口

LVDS 用于低壓差分信號點到點的傳輸,該方式有若干優勢,使其更具有吸引力。較小的信號擺幅使得功耗較低,一般負載阻抗為100? 的差分線上的電流不超過4mA。這一特征使得LVDS 適合做并行數據傳輸。此外信號的電平很低,從而使得該結構可以在2.5V 的低電壓下工作。LVDS 輸入信號電壓可以從0V 到2.4V 變化,單端信號擺幅為400mV,這樣允許輸入共模電壓從0.2V 到2.2V 范圍內變化,也就是說LVDS 允許驅動器和接收器兩端地電勢有±1V 的落差。

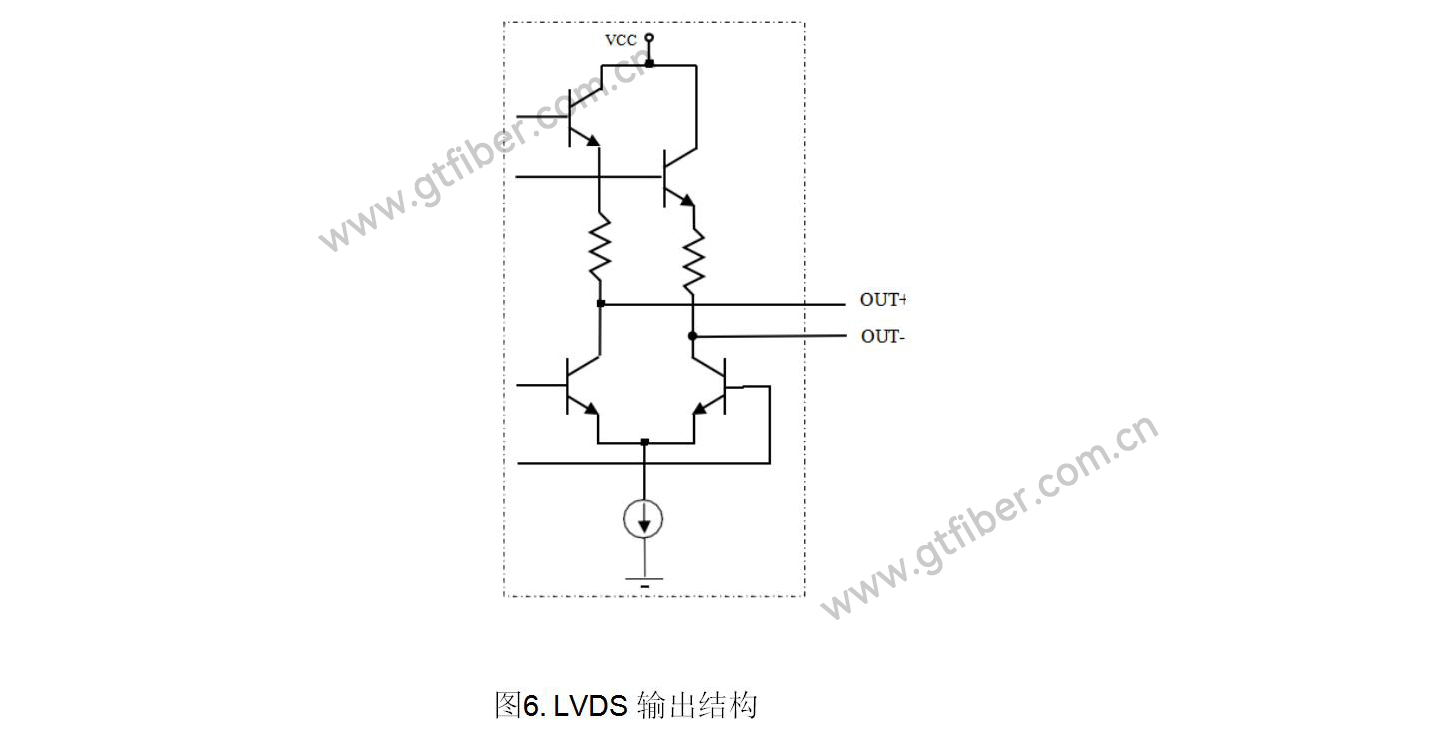

3.1 LVDS輸出結構

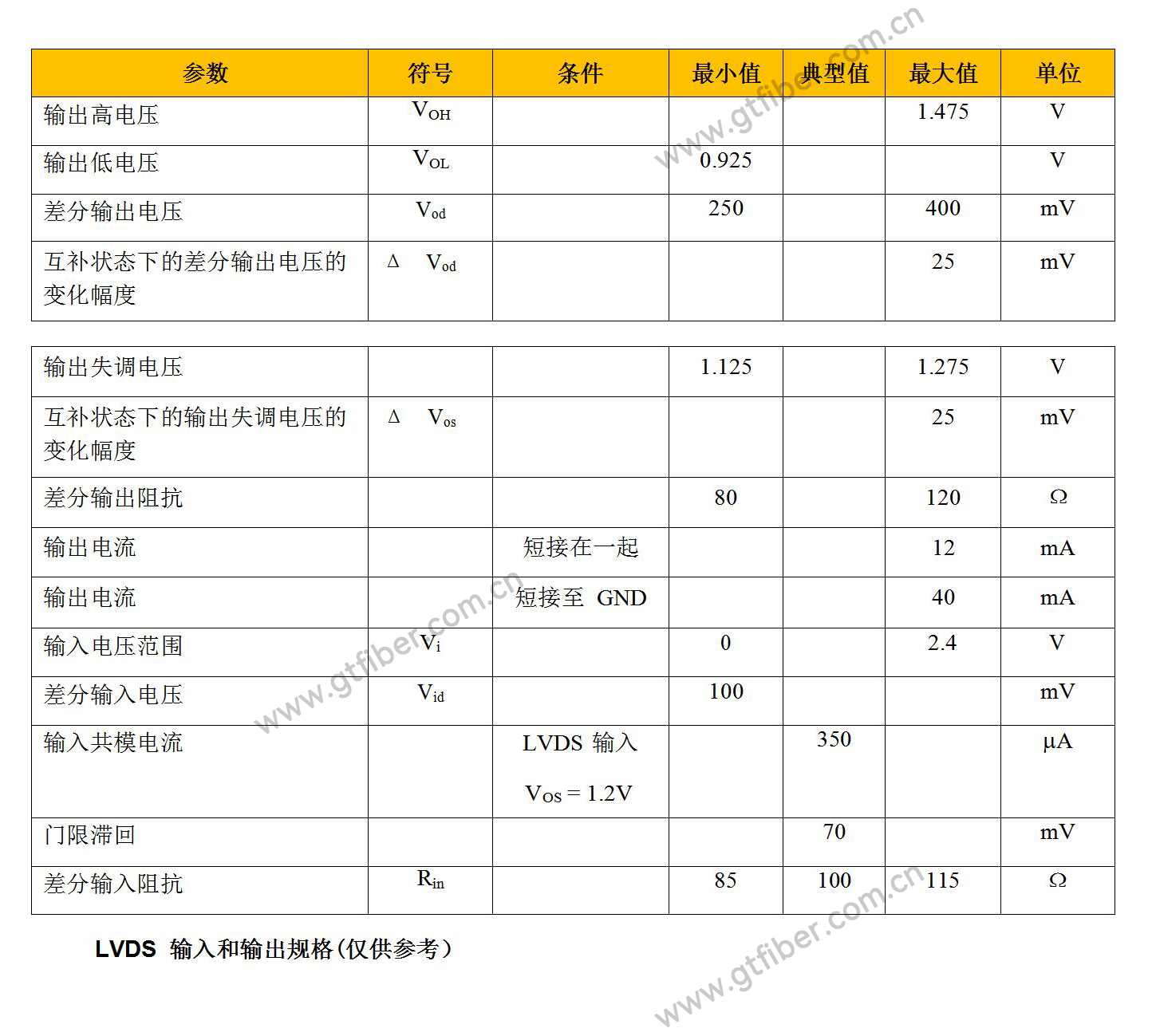

電路如圖6 所示。電路差分輸出阻抗典型值為100?,表III 列出了其它一些輸出指標。

圖6. LVDS 輸出結構

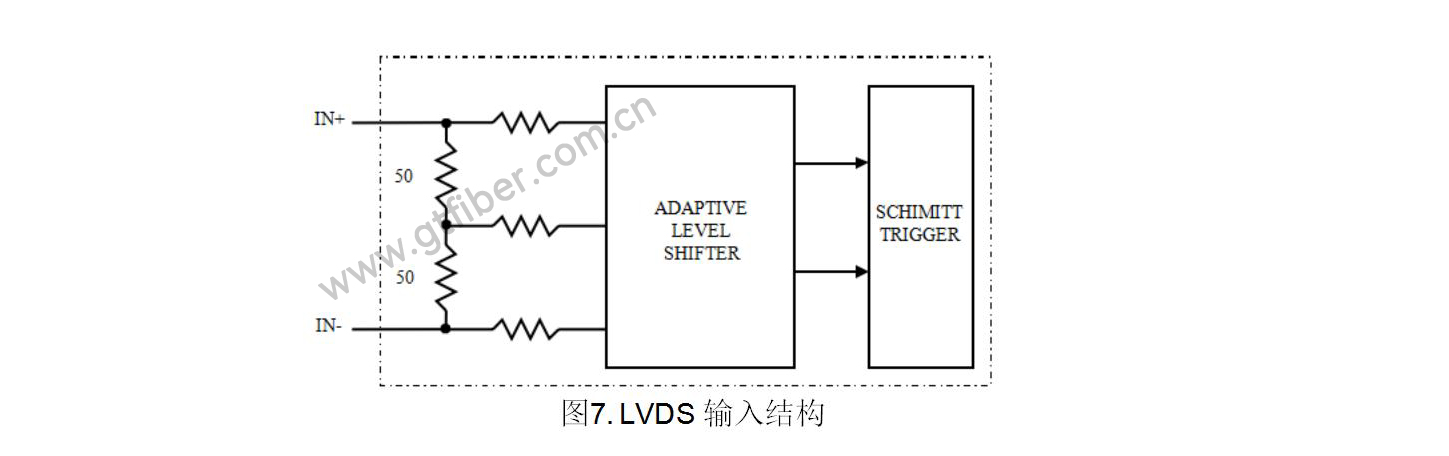

3.2 LVDS輸入結構

LVDS 輸入結構如圖7 所示,IN+與IN-輸入差分阻抗為100?。為適應共模電壓寬范圍內的變化,輸入級還包括一個自適應電平轉換電路,該電路將共模電壓設置為一固定值,該電路后面是一個施密特觸發器。施密特觸發器的輸入門限具有滯回特性,觸發器后級是差分放大器。

-

接口

+關注

關注

33文章

8952瀏覽量

153229 -

lvds

+關注

關注

2文章

1113瀏覽量

67104 -

PECL

+關注

關注

0文章

324瀏覽量

14444 -

光模塊

+關注

關注

80文章

1389瀏覽量

60047

發布評論請先 登錄

LVDS、CML、LVPECL不同邏輯電平之間的互連(二)

LVDS用戶手冊-包含高速CML和信號調理內容

LVPECL、VML、CML、LVDS 與LVDS之間的接口連接轉換

差分邏輯電平,LVDS、xECL、CML、HCSL/LPHCSL、TMDS等

如何在LVPECL、VML、CML、LVDS和子LVDS接口之間轉換

PTN3310 and PTN3311 LVDS-PECL

LVDS|PECL|CML

LVDS分離器簡化高速信號分配

lvds是什么意思?

高速轉換器的lvds,cml,coms數字輸出的分析和對比

詳解信號邏輯電平標準:CMOS、TTL、LVCMOS、LVTTL、ECL、PECL、LVPECL、LVDS、CML資料下載

獲得連接:LVPECL、VML、CML、LVDS 與子 LVDS 之間的接口連接

SN65CML100D 1.5 Gbps LVDS/LVPECL/CML-TO-CML轉換器/中繼器數據表

LVDS、PECL和CML輸出/入結構介紹

LVDS、PECL和CML輸出/入結構介紹

評論