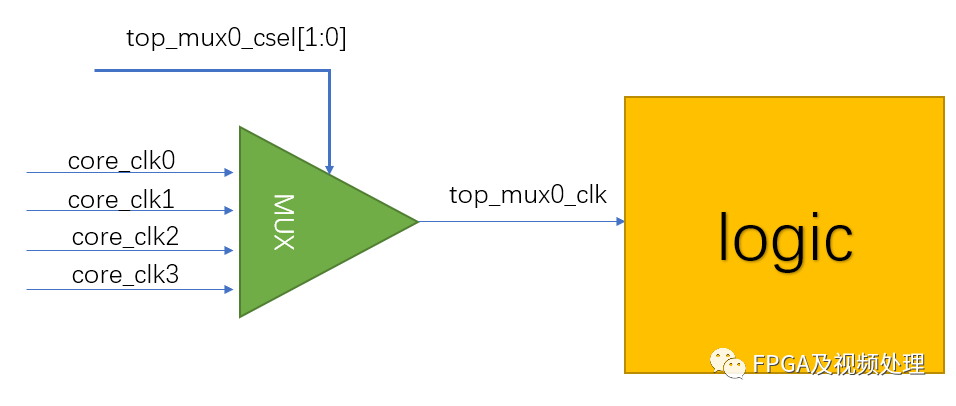

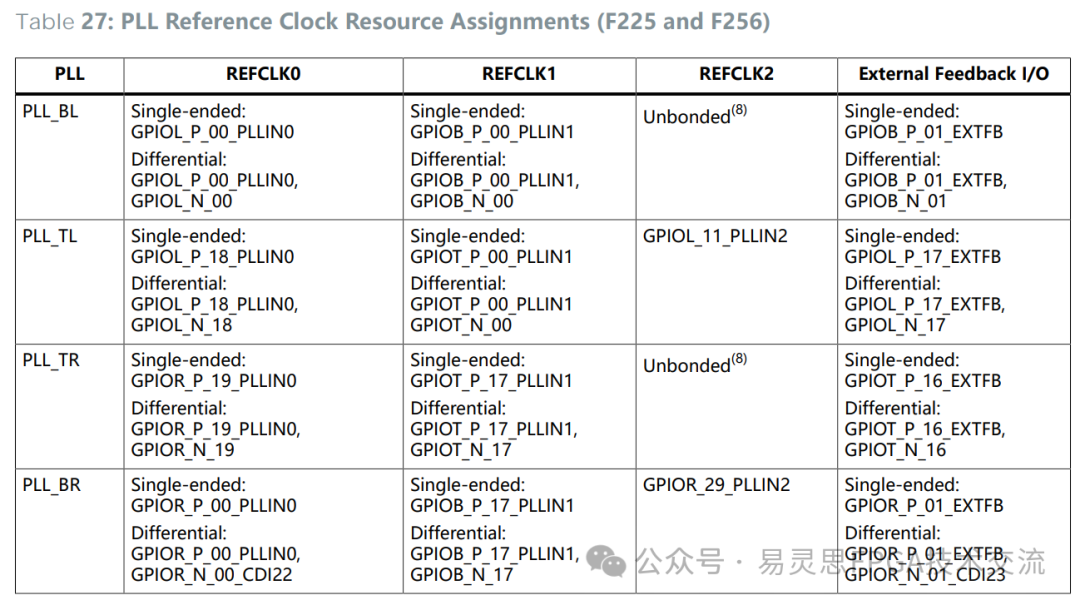

在trion要實現一個4選1時鐘復用或許比較麻煩。但是在鈦鑫上已經給出了解決方案。這里以Ti60F225為例來介紹如何實現下面的4選擇1時鐘選擇功能。

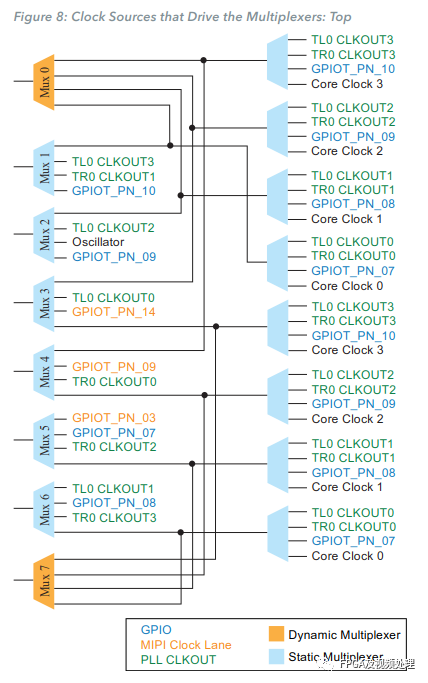

在FPGA的top,bottom,right和left各有8個clkmux,分別是Mux 0 ~ Mux 7。

每個MUX的時鐘來源包括GPIO,LVDS RX(支持gclk和rclk),MIPI RX LANE(用于時鐘的),PLL,Oscillator(片上晶振)和Core(從Core邏輯出來的信號)

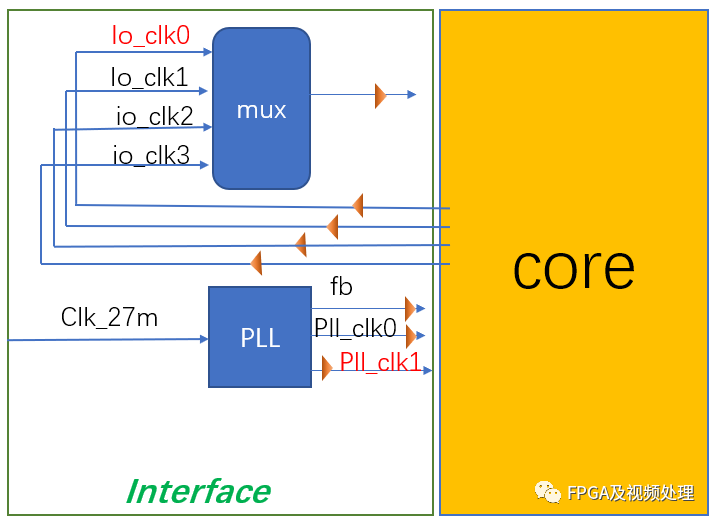

其中只有Mux0和Mux7可以支持4路動態復用,相當于Altera的clockctrl模塊用于時鐘動態選擇。下圖以top為例。

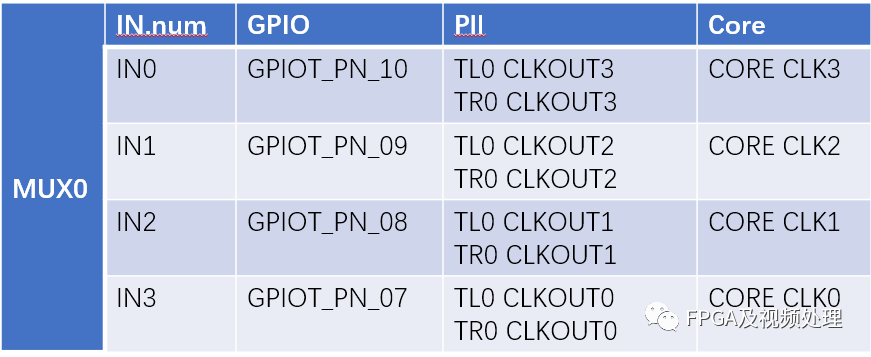

從上圖我們可以看到MUX0和MUX7的時鐘來源包括Core Clock,GPIO,PLL。我們詳細列出top部分Mux0的時鐘源。如表1

表1

有了上面的信息,我們來進行關于時鐘復用的設置。

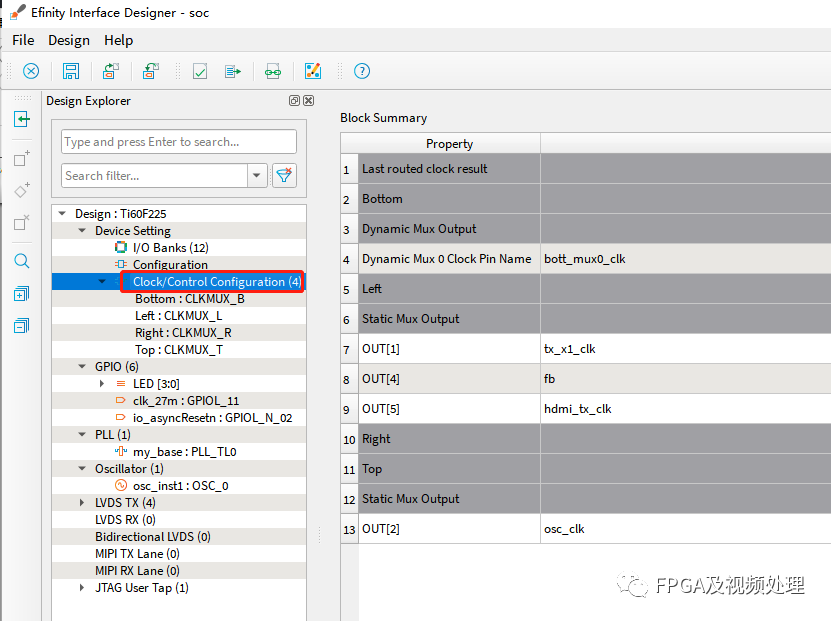

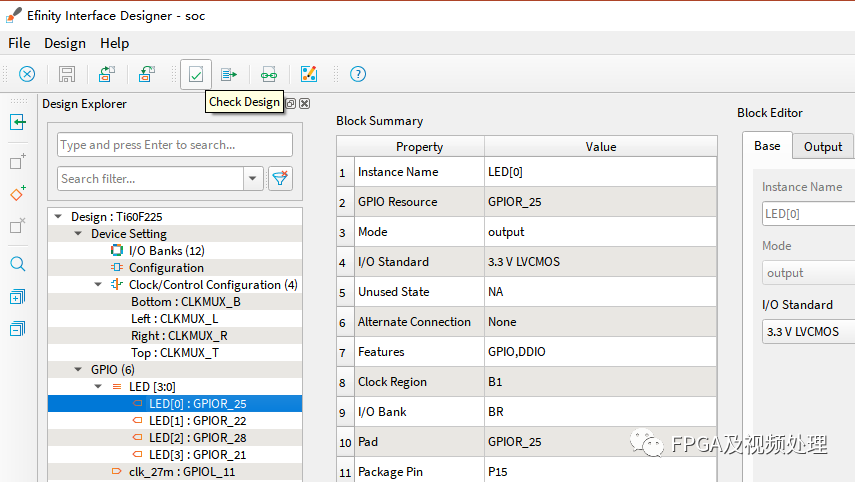

在interface中選擇Device Setting -> Clock/Control Configuration,可以看到對應的top,bottom,right和left的選項。

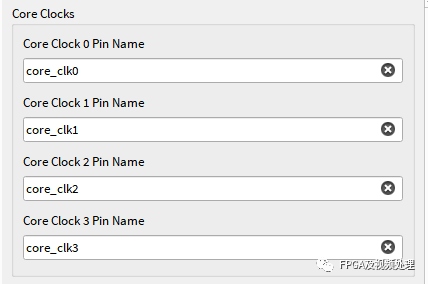

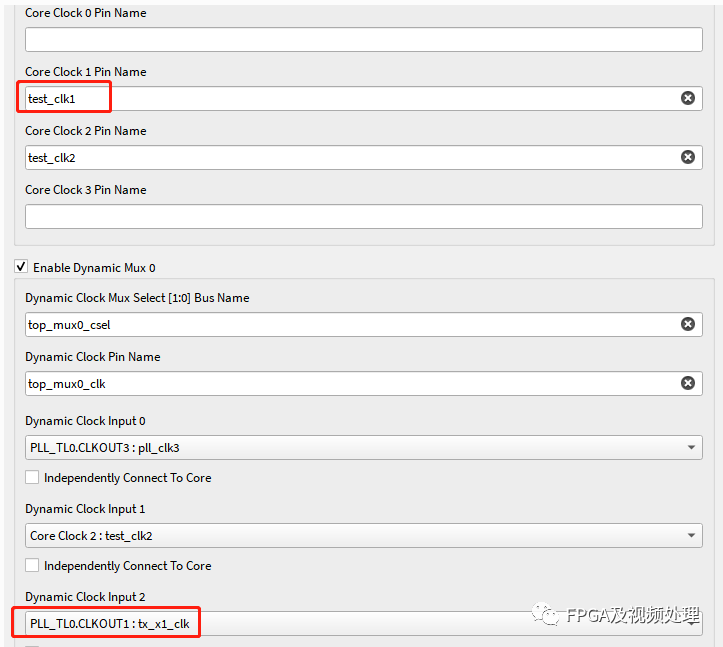

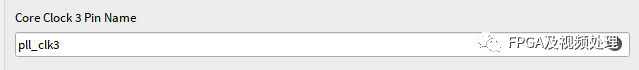

這里我們點擊Top:CLKMUX_T,在右側Global Buffers可以看到三部分。分別是Core Clocks, Enable Dynamic Mux0和Enable Dynamic Mux7(前面已經提到只有Mux0和Mux7支持動態復用)。 對于表1中的Core clocks就是在下圖的Core Clocks設置。它指由Core 到interface中的信號。該信號如果是Core中有邏輯信號需要添加相應的GPIO。這里分別命名為core_clk0,core_clk1,core_clk2和core_clk3. 對于GPIO和PLL的時鐘并不需要手動輸入,因為是固定的時鐘,只需要選擇即可(如果不明白,請繼續往下看)。

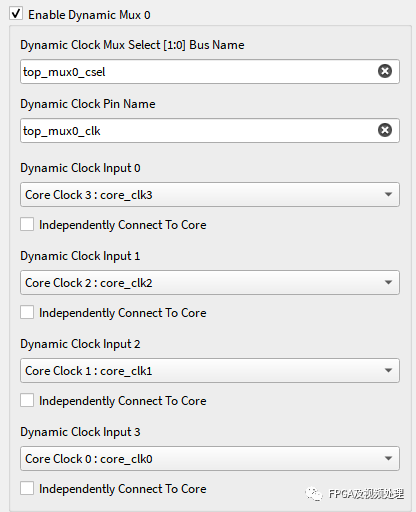

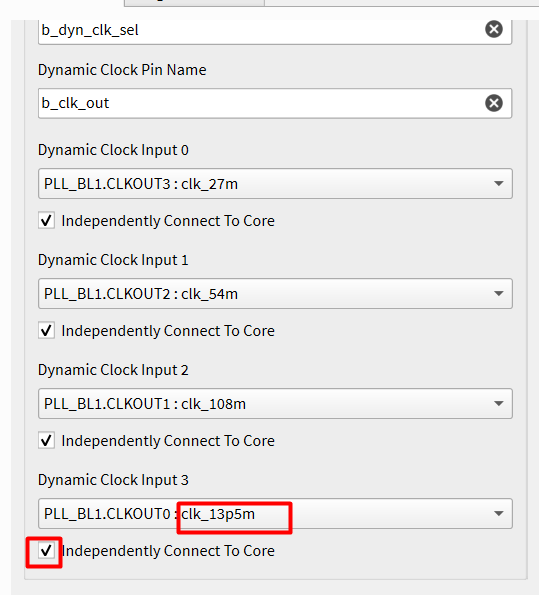

這里我們只打開Mux0,即勾選Enable Dynamic Mux0。

Dynamic Clock Mux Select[1:0] Bus Name是選擇信號的名稱,這里我們輸入top_mux0_csel;

Dynamic Clock Pin Name是指Mux輸出的信號,這是我們命名為top_mux0_clk;

Dynamic Clock Input n(0~3):是指每個輸入選擇項的時鐘來源。

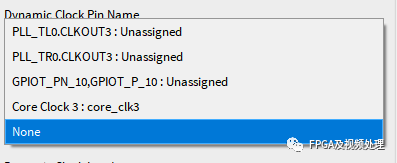

在Dynamic Clock Input N(N指0~3)下面的下拉框可以看到GPIO時鐘源、PLL時鐘源和Core時鐘源是可以選擇的。如果不需要配置該時鐘可以選擇None。Unassigned表示相應的時鐘并沒有設置。根據需要選擇相應的時鐘即可,這里我們都選擇了core_clock。

設置完成之后點擊Check Design來檢測設置是否有錯。

Check Design無誤后可以在生成的template中看到下面的信號,添加到頂層文件可以使用。

output[1:0]top_mux0_csel,inputtop_mux0_clk,

我們設置成如下時鐘方案,在使用中報出如下錯誤:

Rule:clkmux_rule_core_clock_static_mux(Error)

Description:Core clock pin

說明:從core給出的core clock是不能驅動靜態的MUX的,只能驅動動態MUX.包括在Core Clocks輸入了從core輸出的時鐘,但是實際沒有使用。如下圖,輸入了core clock名為test_clk1,但是實際使用的是PLL_TL0.CLKOUT1:tx_x1_clk,就會報上面的錯誤。

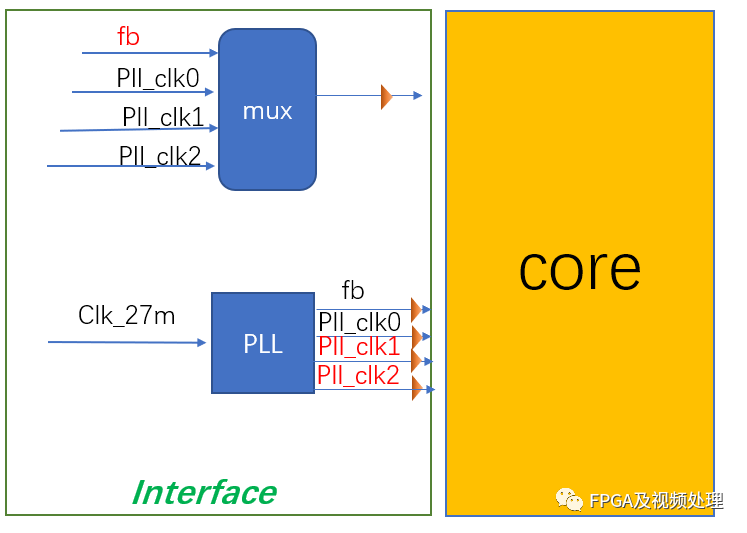

我們設置成如下方案,使用中可能會報如下錯誤:

Rule:clock_rule_dyn_clkmux_input

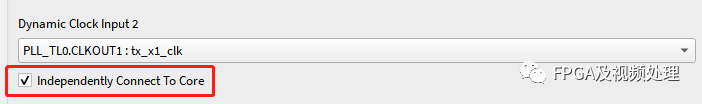

Description:The following clocks need to connect independently to core since they are dynamic clock mux input that also drives the clock pins on the periphery through clockout interface tx_x1_clk

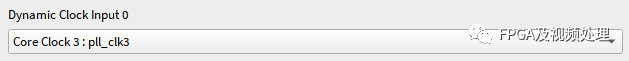

說明:這個問題是說tx_x1_clk即驅動動態的MUX,又驅動core內部的邏輯,這里需要勾選Indepndetly Connect to Core.

另外如果mux的時鐘既有來自core的也有來自PLL的會給出如下警告:

Rule:clkmux_rule_pll_clock(warning)

Description:Dynamic clock mux 0 connected to both inverting and non-inverting clock sources:Clock inversion will not be applied to to_mux0_clk

說明:如果時鐘來源既有core clock又有pll輸出,會有上面的告警信息。

也可以把pll輸入時鐘輸入Core Clock選項中,在時鐘選擇框中選擇Core Clock。就不需要勾選Indepndetly Connect to Core.

那區別在哪里呢,區別就在于如果選擇pll時鐘輸出,時鐘是在interface給到MUX的;如果選擇core clock,那么時鐘就要先進入core,然后再返回到interface再給到MUX,所占用的GBUF數量是不相同的.或者用另一種表達方式:core時鐘進入動態MUX的信號必須要先經過GBUF,而pll的輸出可以不經過GBUF而送給動態MUX.而有時候我們會發現pl給動態MUX的時鐘占用了GPUF,那是因為該時鐘驅動了core邏輯。

注意

(1)如果mux的4路輸入時鐘沒有完全選擇,比如只用到兩個時鐘,那么輸入0必須使用,否則不能運行,比如選擇的是2,3兩路,時鐘是沒有輸出的;

(2)如果某一路沒有時鐘,也不能進行選擇,否則無時鐘輸出也不能再切回來。比如只有0和1有時鐘,選擇時切到2上,肯定沒有輸出,再切回0或者1也沒有辦法再輸出。

(3)如果沒有勾選Independently Connect To Core,即使邏輯頂層定義了該時鐘也是不能使用的。

-

FPGA

+關注

關注

1643文章

21957瀏覽量

614046 -

時鐘

+關注

關注

11文章

1879瀏覽量

132839

發布評論請先 登錄

選擇賽靈思(Xilinx)FPGA 7系列芯片的N個理由

選擇系統時鐘的來源

STC8F/A系統時鐘源選擇外部時鐘串口測試程序

易靈思16nm FPGA助力汽車市場發展 天璣智慧監管解決方案亮相推進會

易靈思Ti60F100驅動LCD屏案例

易靈思鈦金系列時鐘選擇功能-2 以Ti60F225為例來介紹如何實現下面的4選擇1時鐘選擇功能

易靈思鈦金系列時鐘選擇功能-2 以Ti60F225為例來介紹如何實現下面的4選擇1時鐘選擇功能

評論