一、直接模擬頻率合成技術

一般是以高穩(wěn)定度參考源比如晶振所產(chǎn)生的頻率信號作為基準,經(jīng)過必要的的加減乘除運算(對不同信號混頻可以看作對相應頻率的加減運算,倍頻和分頻看作乘除運算)得到需要的新的頻率,由于這樣產(chǎn)生的頻率是一系列離散的值,可以通過濾波器和開關的選擇性提取出我們需要的指定輸出頻率,最后通過放大濾波電路輸出。直接模擬頻率合成技術屬于發(fā)展的早期階段,它的特點是較高分辨率和穩(wěn)定度,跳變頻時間短,但是也有因?qū)?a href="http://www.asorrir.com/v/tag/167/" target="_blank">電路設計的高要求而產(chǎn)生的成本尺寸問題。

二、直接數(shù)字頻率合成技術

基本思路

它首先是將波形的關鍵信息按已知邏輯置于芯片的集成寄存器中,通過控制信號可以有邏輯地讀取相應的波形信息,再經(jīng)過數(shù)模變換和濾波放大等內(nèi)部集成的電路結(jié)構(gòu)就可以合成我們想要的信號。

對于 DDS 的整個原理過程進行分析可知,將幅值相位等波形信息進行存儲時,從模擬到數(shù)字的過程避免不了數(shù)字量化誤差,這是導致相位失真和幅度失真的主要原因,其次,DDS 方案還存在雜散較大且不能消除、相位累加器截斷誤差、正弦查找表有限字長和時鐘信號泄漏等問題。它從波形信息單獨存儲提取的角度出發(fā),可以產(chǎn)生任意需要的波形和需要的初始相位,這種設計的靈活性也讓它可以在更廣闊的場景中發(fā)揮作用。

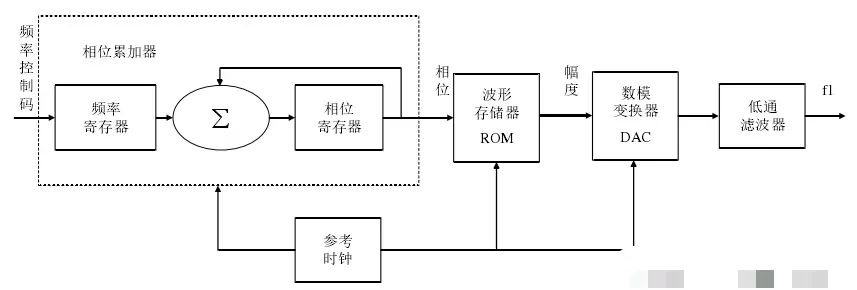

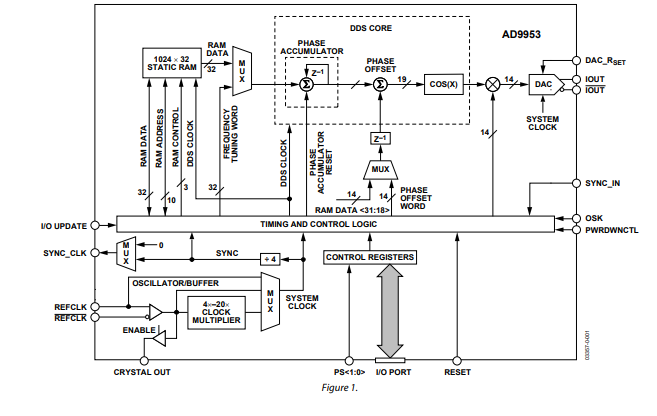

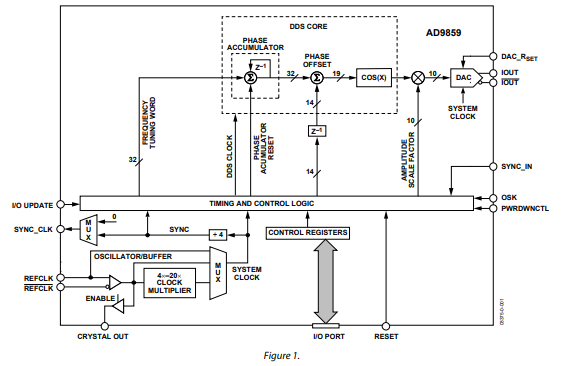

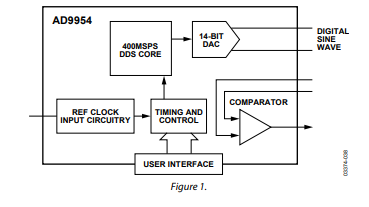

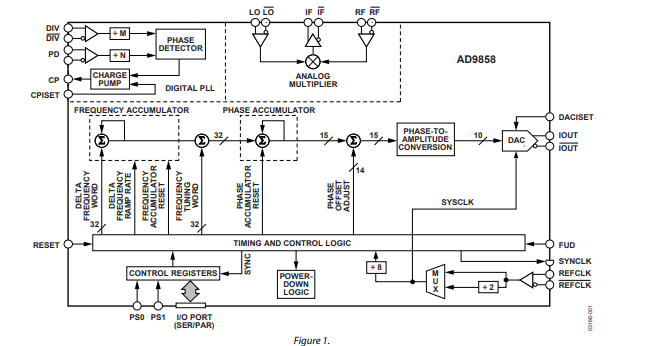

DDS 的基本原理框圖如上圖所示,從中看出,基本工作原理是邏輯控制產(chǎn)生的頻率碼控制累加器的一系列相位步進并且對應到相位信息,然后利用已知的存儲邏輯在 ROM 中找到對應的幅度,接下來經(jīng)過 DAC 模塊使信號的幅度成為階梯狀信號,最終再低通濾波得到連續(xù)的正弦信號。

三、間接模擬式頻率源

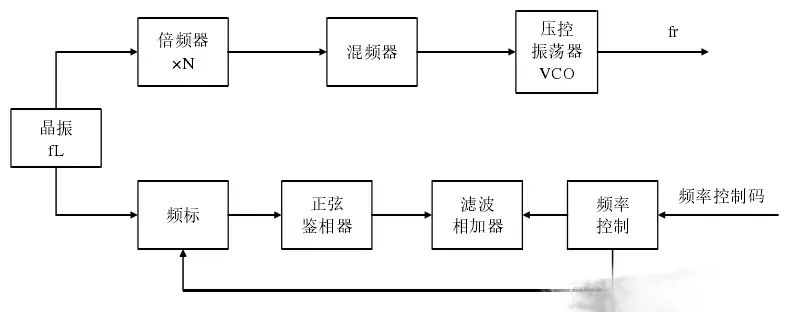

間接模擬式頻率源的核心是模擬鎖相環(huán),它的頻率響應時間比直接式的短得多,因為鎖相環(huán)等器件都有時延,另一方面,也是鎖相環(huán)類似于窄帶濾波的特性會讓此方案的雜散較好,而架構(gòu)中的正弦鑒相器也會有效提升相噪指數(shù)。它的原理框圖如下圖,但也會有電路結(jié)構(gòu)復雜等限制它應用的缺陷。

該類頻率源方案的架構(gòu)中,晶振產(chǎn)生一個Lf 的基準頻率,一路經(jīng)過倍頻后與壓控振蕩器的輸出信號進行上變頻操作,實現(xiàn)壓控振蕩器輸出信號向高頻段的頻譜搬移,另一路則是以初始晶振得到的信號作為參考,在邏輯控制下與目標信號進行同頻鑒相,最終讓壓控振蕩器與晶振輸出信號的相位保持一致,達到鎖定狀態(tài)。架構(gòu)中的倍頻和混頻操作只是為實現(xiàn)高頻 VCO 的目標,不是必要模塊。

四、間接數(shù)字式頻率源

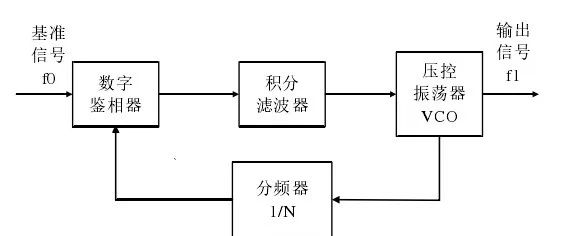

它的核心是數(shù)字鎖相環(huán),電路結(jié)構(gòu)方面加入了數(shù)字分頻器。特點是是頻率分辨

率高,易于集成等,因此通信系統(tǒng)中發(fā)揮著重要的作用,主要缺陷是相位噪聲差。

間接數(shù)字式頻率綜合器的結(jié)構(gòu)如上圖所示,從中可以看到,先對壓控振蕩器的輸出頻率被進行N分頻,再經(jīng)過反饋回路與用于參考的基準頻率比較相位和頻率等信息,二者之間的差異直接影響誤差電壓信號使 VCO 頻率重新鎖定到目標頻率的信號輸出。

五、鎖相環(huán)頻率合成技術

鎖相環(huán)合成技術核心是相位控制機制的鎖相環(huán),之前已經(jīng)有了一定介紹。具體而言分為整數(shù)分頻和小數(shù)分頻頻率合成技術,其中常用的小數(shù)分頻頻率合成技術又分為脈沖移除技術和雙模分頻技術。

整數(shù)分頻頻率合成技術是在鎖相環(huán)的反饋回路中增加了一個分頻器,工作機制區(qū)別不大,由于分頻器的作用使輸出信號 fo與輸入信號 fi 頻率不再相等,而是變?yōu)楣潭ū戎?N,即: fo=N?fi。

利用鎖相環(huán)路可以快速調(diào)節(jié)重新鎖定的特點,目前應用廣泛的是程序控制 N 來實現(xiàn)鎖相環(huán)輸出信號 fo 在壓控振蕩器的輸出范圍內(nèi)掃頻輸出。

整數(shù)分頻技術設計的系統(tǒng)能夠輸出的最精細頻率步進就是鑒相頻率 fi ,因此對同一輸出頻率,提高其頻率分辨率只有增大分頻比 N,但這樣也會使鎖相環(huán)系統(tǒng)的相位噪聲惡化,相比較而言小數(shù)分頻技術可以在保持內(nèi)部鑒相頻率不變的前提下有效提升輸出信號的頻率分辨率性能,在高分辨率頻率源的設計中更為適用。小數(shù)分頻中脈沖移除技術是在整數(shù)分頻的電路結(jié)構(gòu)基礎上又在鎖相環(huán)反饋環(huán)路加入一個脈沖移除器,它可以按照特定的周期移除信號中的脈沖,脈沖移除技術進一步發(fā)展形成了雙模分頻技術。

六、混合頻率合成技術

上述幾種單一類型的頻率合成技術方案都有自己比較明顯的優(yōu)缺點,所以目前頻率合成方案都會將直接和間接,數(shù)字和模擬,鎖相環(huán)頻率合成等多種頻率合成技術結(jié)合起來,盡可能保留各自的優(yōu)勢,避免較為明顯的缺陷,綜合形成混合頻率合成技術方案。

這樣可以實現(xiàn)單種頻率合成技術達不到的綜合性能指標。現(xiàn)今混合頻率合成方案已經(jīng)發(fā)展地較為完善,這里主要討論一下多環(huán)鎖相,DDS 激勵鎖相環(huán),PLL 和DDS 環(huán)內(nèi)和環(huán)外混頻這四種。

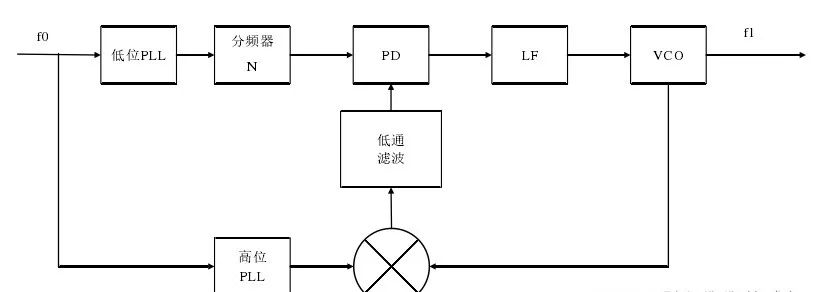

多環(huán)鎖相結(jié)構(gòu)相比于單環(huán)在頻率分辨率方面有明顯的提升,如下圖所示:

輸入信號頻率為 f0 ,分兩路,一路經(jīng)過低位鎖相環(huán)再經(jīng)過分頻器 N ,輸出頻率變?yōu)?N1f0/N ,相應頻率分辨率為 fo/N ,另一路經(jīng)過高位鎖相環(huán),輸出頻率變?yōu)?N2f0,相應頻率分辨率為 f0 ,這兩路的輸出信號再由鎖相環(huán)路實現(xiàn)相加輸出信號 f1,總體的頻率分辨率為 f0/N ,即: f1=(N2+N1/N)?f0。

綜合來看,為了實現(xiàn)高頻率分辨率的目標,此種方案也會存在由于電路復雜導致的相位噪聲和諧波惡化的問題。

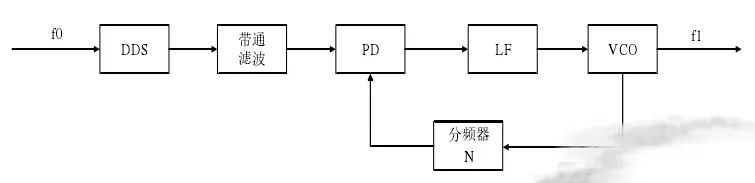

DDS 激勵鎖相環(huán)的系統(tǒng)框架如下圖:

系統(tǒng)的總體輸出信號頻率表示為式: f1=N?fDDS=N?MK?f0

其中直接數(shù)字頻率合成中的頻率控制字表示為 K ,相位累加器字長表示為 M ,此方案有效結(jié)合了兩種技術的優(yōu)勢,在寬帶高分辨率應用方面有重要的作用。

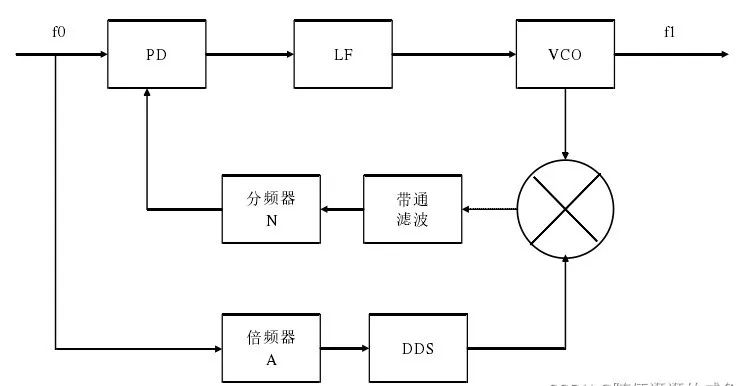

PLL 與 DDS 環(huán)內(nèi)混頻的原理框圖如下圖所示:

結(jié)構(gòu)方面,是將 DDS 引入基本的鎖相環(huán)路內(nèi),輸出頻率描述為: f1=A?fDDS+N?f0=(A?MK+N)?f0

此方案可以優(yōu)化輸出信號的相位噪聲參數(shù)并且改善雜散帶來的干擾(PLL 窄帶濾波特性),但是帶寬較窄并且濾波難度較大。

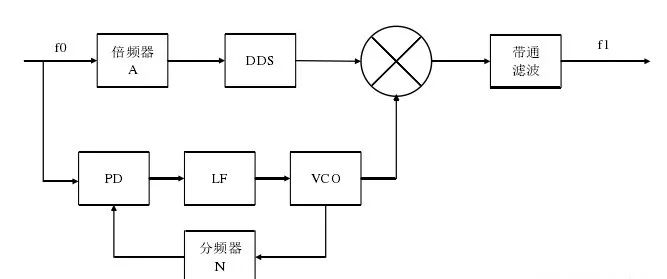

PLL 與 DDS 環(huán)外混頻的原理框圖如下圖:

結(jié)構(gòu)方面,核心是 DDS 輸出頻率和 PLL 輸出頻率在外部混頻,頻率分辨率為:(A/M)f0 ,輸出頻率表示為式:f1=A?fDDS±N?f0=(A?MK±N)?f0

此系統(tǒng)方案可以有效提升頻率分辨率,調(diào)頻速度和頻率輸出范圍的性能,但是和環(huán)內(nèi)混頻一樣會有雜散和濾波難度方面的問題。

原文鏈接:https://2048.csdn.net/6825b01ca5baf817cf4c613b.html

-

鎖相環(huán)

+關注

關注

35文章

592瀏覽量

88408 -

濾波器

+關注

關注

162文章

8045瀏覽量

180773 -

晶振

+關注

關注

34文章

3175瀏覽量

69426 -

頻率合成

+關注

關注

1文章

20瀏覽量

22119

原文標題:常見的頻率合成方案匯總

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

AD9953 400 MSPS、14位DAC、1.8 V CMOS直接數(shù)字頻率合成器技術手冊

AD9951 400 MSPS、14位DAC、1.8 V CMOS直接數(shù)字頻率合成器技術手冊

AD9859 400 MSPS、10位DAC、1.8 V CMOS直接數(shù)字頻率合成器技術手冊

AD9954 400MSPS、14位、1.8V CMOS、直接數(shù)字頻率合成器技術手冊

AD9858 1 GSPS直接數(shù)字頻率合成器技術手冊

ADF4155整數(shù)N/小數(shù)N分頻PLL頻率合成器技術手冊

一文詳解RAID技術

dds數(shù)字頻率是怎么合成的 DDS數(shù)字頻率信號發(fā)生器的設計

AN-1879小數(shù)N分頻頻率合成器

一文詳解頻率合成技術

一文詳解頻率合成技術

評論