概述

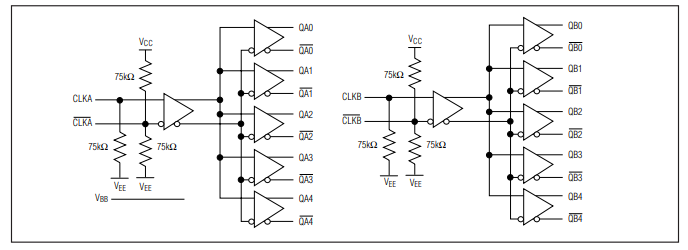

MAX9320B是一種低扭曲、1:2差分驅動器, 設計用于時鐘和數據分配,由一路輸入再生2路差分輸出。差分輸入經過調整后,可以允許單端輸入,只需外加基準電壓即可。

MAX9320B具有超低傳輸延遲(208ps)、20ps的器件至器件扭曲和6ps的輸出至輸出扭曲以及最大30mA的電源電流等特性,使其尤其適合于時鐘分配。為與差分PECL和LVPECL信號接口,該器件工作于+3.0V至+5.5V的電源電壓,能夠實現在3.3V或5V標稱電壓系統中,進行高性能的時鐘或數據分配。而對于差分ECL和LVECL工作方式,該器件工作于-3.0V至-5.5V的電源電壓。

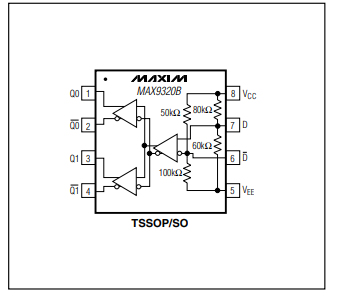

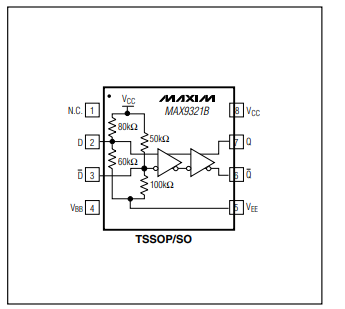

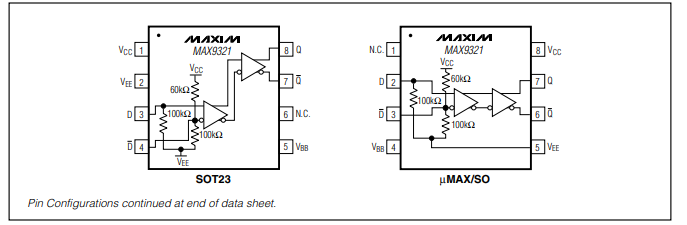

MAX9320B以工業標準的8引腳TSSOP和SO封裝。

數據表:*附件:MAX9320B 1比2差分PECL ECL LVPECL LVECL時鐘和數據驅動器技術手冊.pdf

應用

- 低抖動數據中繼器

- 精密時鐘分配

- 保護開關

特性

- 改進的MC10EP11D代用產品

- +3.0V至+5.5V差分PECL/LVPECL工作方式

- -3.0V至-5.5V ECL/LVECL工作方式

- 22mA的低電源電流

- 20ps器件至器件扭曲

- 6ps輸出至輸出扭曲

- 208ps傳輸延遲

- 3GHz時最小輸出300mV

- 輸入開路時,輸出為低電平

2kV的ESD保護(人體模型)

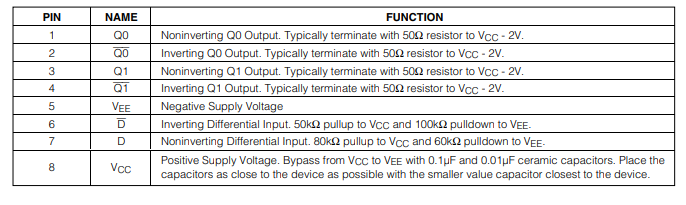

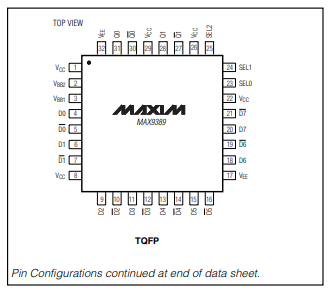

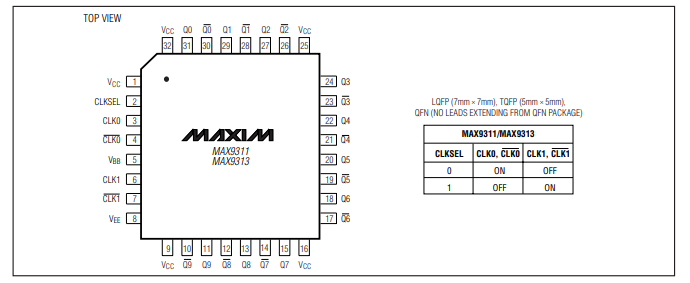

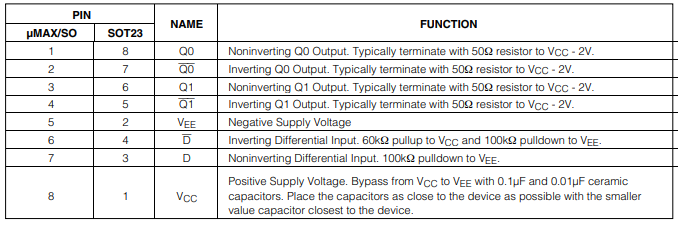

引腳配置描述

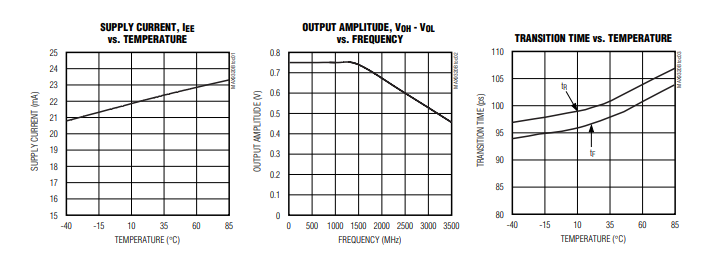

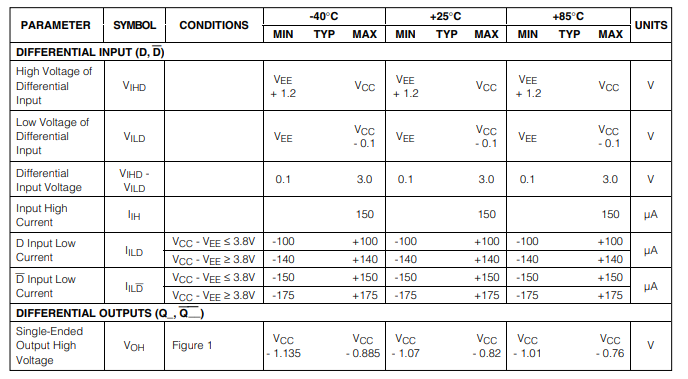

典型操作特性

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

驅動器

+關注

關注

54文章

8636瀏覽量

149103 -

時鐘

+關注

關注

11文章

1883瀏覽量

132853 -

差分驅動器

+關注

關注

0文章

64瀏覽量

15536

發布評論請先 登錄

相關推薦

熱點推薦

ecl差分接入的0.8v擺幅是否可以驅動ad10242,lvpecl電平是否可以滿足標準?

可以使用標準ECL GATE 驅動時鐘,但是一般認為ecl的擺幅只有0.8v

我的問題是:1 ecl

發表于 12-18 07:36

MAX9320B 1:2差分PECL/ECL/LVPECL/LVECL時鐘和數據驅動器技術手冊

MAX9320B 1:2差分PECL/ECL/LVPECL/LVECL時鐘和數據驅動器技術手冊

評論