概述

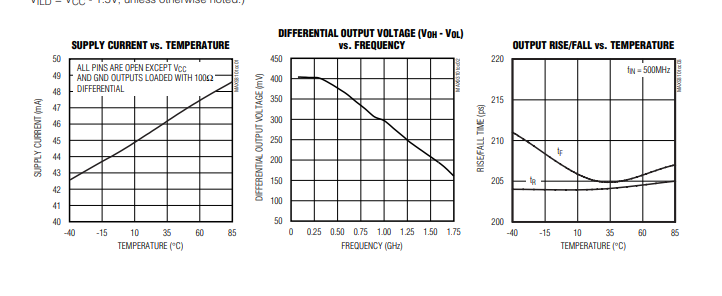

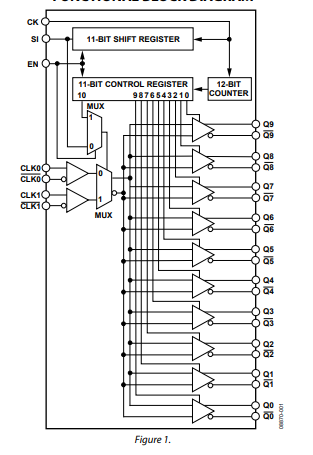

MAX9310是一種快速,低扭曲1:5差分驅動器,具有可選的LVPECL/HSTL輸入端和LVDS輸出端,設計應用于時鐘分配。這種器件的特點是具有345ps的極低傳輸延遲和45.5mA的電源電流。

MAX9310工作在2.375V至2.625V電源范圍,適用于2.5V系統。通過2:1輸入多路復用器,選擇兩路差分輸入中的一路。輸入選擇是由CLKSEL引腳控制,這種器件也具有同步使能功能。

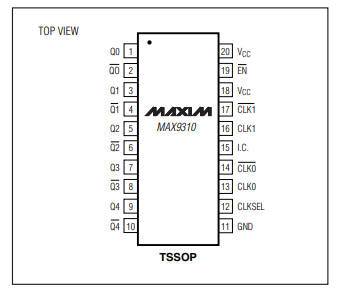

MAX9310提供節省空間的20引腳TSSOP封裝,可工作在-40°C至+85°C的寬溫度范圍。

數據表:*附件:MAX9310 1比5時鐘驅動器,可選的LVPECL輸入與LVDS輸出技術手冊.pdf

應用

- 自動測試設備(ATE)

- 局端背板時鐘分配

- 數據和時鐘驅動器與緩沖器

- DSLAM

- 無線基站

特性

- 保證1.0GHz工作頻率

- 8ps輸出至輸出扭曲

- 345ps傳輸延遲

- 接受LVPECL和差分HSTL輸入電平

- 同步輸出使能/禁止

- 兩路可選擇的差分輸入

- 2.375V至2.625V電源電壓

- ESD保護:±2kV (人體模型)

- 輸入開路時,輸入偏置電阻驅動輸出為低

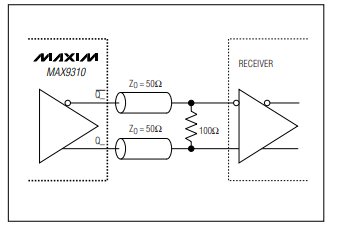

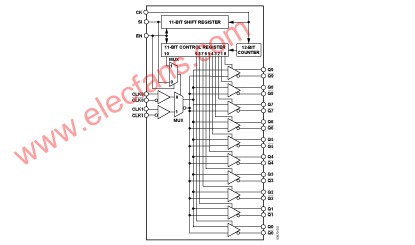

典型應用電路

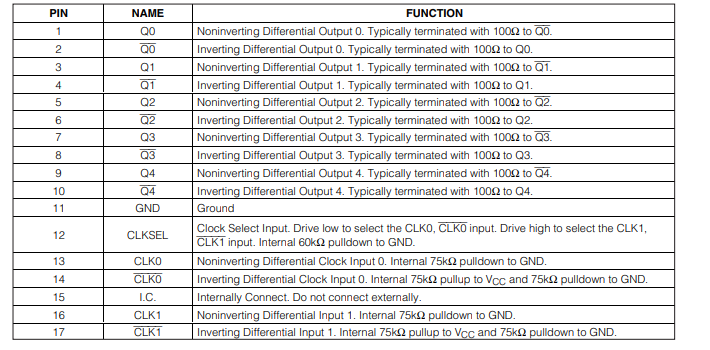

引腳配置描述

典型操作特性

詳細說明

MAX9310是一款低偏斜1:5差分驅動器,具有兩個可選的LVPECL輸入和LVDS輸出,專為時鐘分配應用而設計。選通時鐘接受差分輸入信號,并將其復制到五個獨立的差分LVDS輸出。輸入由內部偏置電阻進行偏置,這樣當輸入開路時,輸出為差分高電平。輸出驅動器保證在高達1.0GHz的頻率下工作,LVDS輸出電平符合EIA/TIA - 644標準。

MAX9310的設計工作電壓范圍為2.375V至2.625V,標稱值為2.5V。

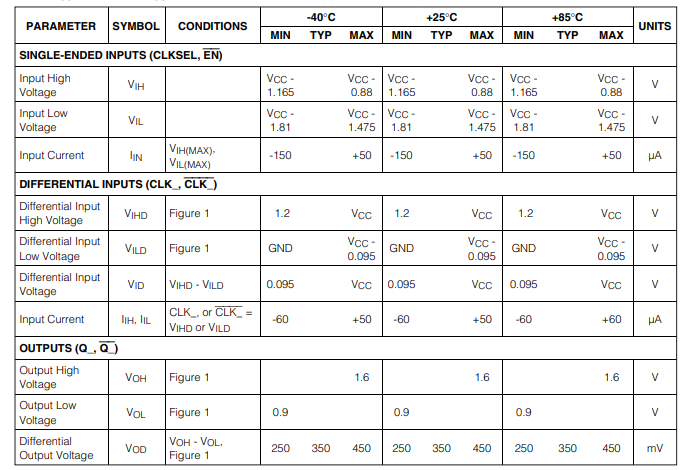

差分LVPECL輸入

MAX9310有兩個差分LVPECL輸入端口,每個差分輸入對都有獨立的端接。一個選擇引腳(CLKSEL)用于激活所需的輸入。施加到輸入的差分信號的最大幅度為Vcc。差分信號的高電平和低電平(VHD和VLD)以及差分輸入電壓(VIH - VIL)可同時施加。

同步使能

MAX9310的輸出在差分低電平狀態下同步使能和禁用,以消除選通時鐘脈沖中的短脈沖。EN連接到輸入的邊沿觸發D觸發器的置位端。上電后,將EN驅動為低電平并切換時鐘頻率以啟用輸出。輸出在所選輸入時鐘的下降沿使能。EN下降沿時,輸出設置為所選輸入時鐘下降沿的差分低電平狀態(圖2)。

輸入偏置電阻

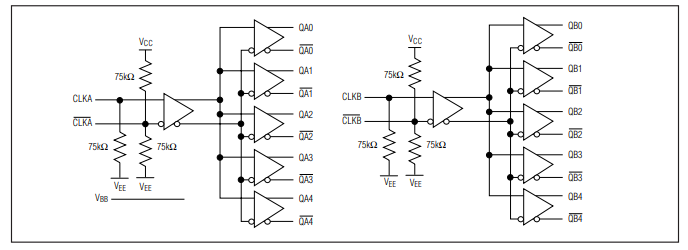

內部偏置電阻確保在輸入(差分)未連接的情況下輸出為低電平。反相輸入(CLK_)通過一個75kΩ下拉電阻偏置到地,同相輸入(CLK_)通過一個75kΩ上拉電阻偏置到Vcc。

差分LVDS輸出

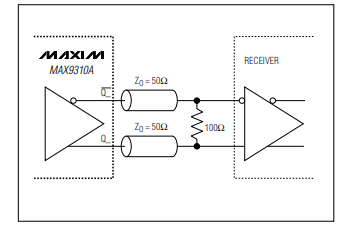

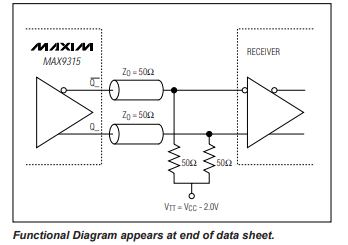

LVDS輸出必須按照典型應用電路所示,在Q_和Q_之間用100Ω電阻進行端接。輸出具有短路保護功能。

應用信息

電源去耦

將每個Vcc引腳通過0.1μF和0.01μF的高頻表面貼裝陶瓷電容旁路至地,盡可能將電容靠近器件安裝,0.01μF電容最靠近器件。使用多個并聯過孔,以最小化寄生電感并減少大電流瞬變引起的電源波動。

受控阻抗走線

輸入和輸出走線特性會影響MAX9310的性能。將高頻輸入和輸出連接到50Ω特性阻抗走線,盡量縮短走線長度,以防止阻抗不連續。通過匹配電纜和連接器保持50Ω特性阻抗,以減少反射。通過匹配差分對內走線的電氣長度來減少偏移。

輸出端接

按照典型應用電路所示,在Q_和Q_之間用100Ω電阻對輸出進行端接。

-

驅動器

+關注

關注

54文章

8615瀏覽量

149026 -

lvds

+關注

關注

2文章

1110瀏覽量

67062 -

LVPECL

+關注

關注

2文章

40瀏覽量

18244 -

差分驅動器

+關注

關注

0文章

64瀏覽量

15534

發布評論請先 登錄

LVPECL驅動器終端設計介紹

可編程低電壓1:10 LVDS時鐘驅動器ADN4670

AD9523-1:低抖動時鐘發生器,14路LVPECL/LVDS/HSTL輸出或29路LVCMOS輸出 數據手冊

CDCLVP111-SP具有可選輸入時鐘驅動器的低電壓1:10 LVPECL數據表

CDCLVP111低壓1:10 LVPECL,內置可選輸入時鐘驅動器數據表

CDCLVD110A可編程低壓1:10 LVDS時鐘驅動器數據表

CDCVF111 1:9差分LVPECL時鐘驅動器數據表

MAX9312/MAX9314雙路、1:5差分LVPECL/LVECL/HSTL時鐘和數據驅動器技術手冊

MAX9310 1:5時鐘驅動器,可選的LVPECL輸入與LVDS輸出技術手冊

MAX9310 1:5時鐘驅動器,可選的LVPECL輸入與LVDS輸出技術手冊

評論