做芯片設計的同學應該或多或少的聽到過“異步電路”(Asynchronous Circuit)。和我們實踐中使用的同步電路相比,異步電路好像一直是一個傳說中的存在。雖然甚至有過完全基于異步電路的處理器,但它始終沒有進入過主流的數(shù)字芯片領域。不過,伴隨AI芯片的熱潮,異步電路越來越多的出現(xiàn)在我們視野當中,甚至成了一些芯片的賣點。本文和大家一起探討一下異步電路原理及其優(yōu)勢和劣勢,并通過Intel的Loihi芯片看看它的實現(xiàn),希望能夠給大家一個更清晰的認識。

如果要了解異步電路,[1]是一個比較好的參考。首先我們可以從下面4個圖簡單回顧一下異步電路的概念。

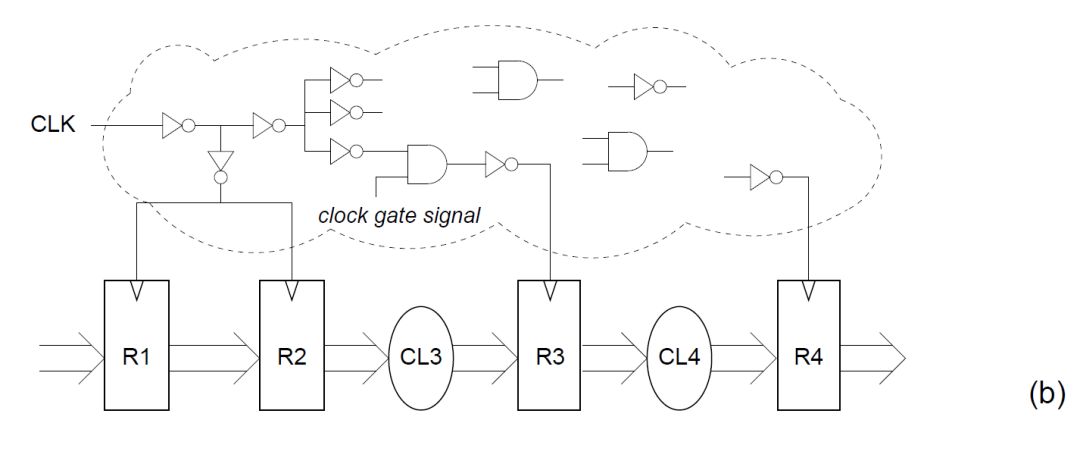

目前數(shù)字芯片的主流設計都是同步電路(Synchronous),它的基本結構如上圖所示。數(shù)據(jù)的流動靠一個全局時鐘信號(Clock)來同步。所有的時序器件(圖中的Rn)都是在時鐘邊沿采樣數(shù)據(jù)并向后傳輸。數(shù)據(jù)被處理(比如邏輯和算數(shù)操作)后到達下一級。相當于大家都只在約定好的時間點才觀察輸入數(shù)據(jù)線上的數(shù)據(jù),只要保證數(shù)據(jù)在這個時間點是穩(wěn)定正確的,數(shù)據(jù)就可以正確的被傳遞和處理。可以說,這種以時鐘信號驅(qū)動的流水線結構是現(xiàn)代數(shù)字電路的基礎。隨著設計和測試的復雜度的不斷提高,加之低功耗設計(比如clock gating)的需求,在一個實際設計中,時鐘信號會變得異常復雜,如下圖所示。這也是困擾目前大規(guī)模芯片設計的主要問題之一。

言歸正傳,我們還是重點看看異步電路。異步電路有時也稱為無時鐘(clockless)或者自定時(self-timed)電路,顧名思義,就是沒有全局時鐘的電路,如下圖所示。在異步電路中,大家沒有一個統(tǒng)一的時鐘,前后級直接告知對方能否接收數(shù)據(jù)。具體來說,就是通過前后級直接發(fā)送握手信號(Request和Acknowledge)來保證數(shù)據(jù)傳輸?shù)恼_性。Bundled-data是這種機制的一個標準術語,其含義是數(shù)據(jù)和控制信號捆綁在一起,而其中控制信號則起到了在同步電路中時鐘信號所起的作用。

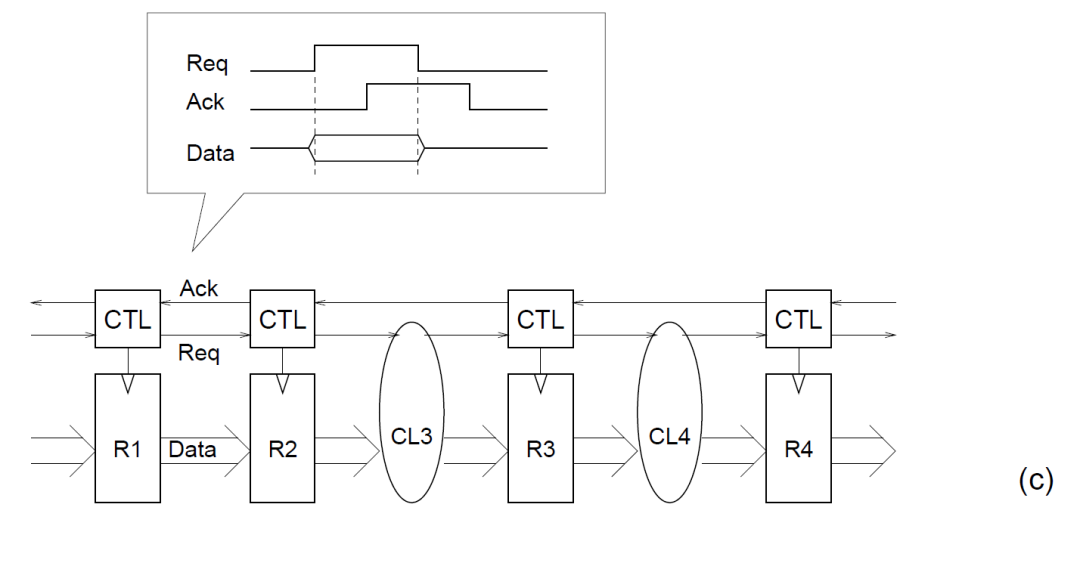

Bundled-data使用的控制協(xié)議包括幾種,比如數(shù)據(jù)傳輸要進行4次握手的4-phase bundled-data protocol,和只要兩次握手的2-phase bundled-data protocol。下圖來自[2],圖靈獎得主Ivan Edward Sutherland的一篇論文。正是這篇論文提出了2-phase bundled-data protocol(論文還包括了其它非常豐富的內(nèi)容和思考,非常值得一看)。這張圖非常清楚的描述了用兩次握手來實現(xiàn)數(shù)據(jù)傳輸?shù)姆椒ǎ揖筒欢嘟忉屃恕_@里要注意的是,控制信號Request和Acknowledge的上升沿和下降沿是完全等效的。

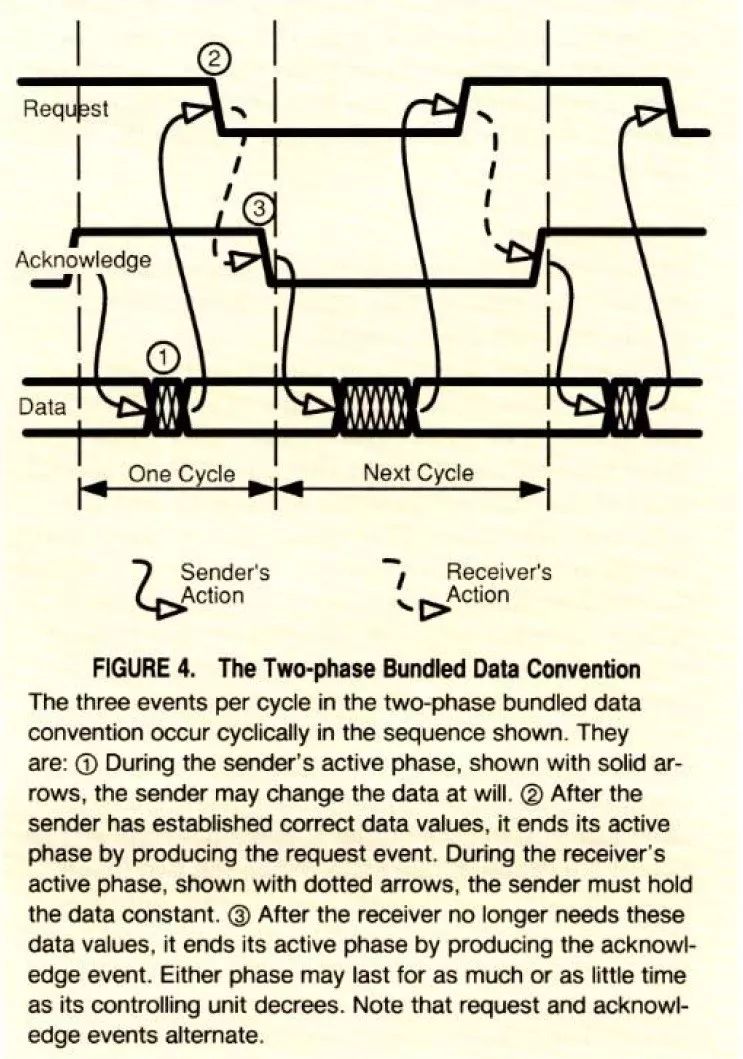

從這里不難看出在異步電路中控制信號是非常重要的。回想一下Petascale AI芯片Vathys:靠譜項目?清奇腦洞?還是放衛(wèi)星?,印度小哥給的一頁PPT就是在說他們的異步電路設計的控制信號性能多好。不管是不是忽悠,關鍵點還是抓住了。

???

下面我們來討論一下異步電路和同步電路相比的優(yōu)勢和劣勢,以及它在AI芯片里的應用。在Wikipedia的“Asynchronous circuit”詞條里,對兩者進行了比較完整的對比。(可能因為主題詞是異步電路,對優(yōu)勢講的比較多)

優(yōu)勢:

Robust handling ofmetastabilityofarbiters.

對做數(shù)字芯片的同學來說,亞穩(wěn)態(tài)(metastability)一直是個頭疼的問題。它主要是指數(shù)字信號在翻轉(zhuǎn)(比如從低電平‘0’變?yōu)楦唠娖健?’)的過程中會有一段時間(transition time)信號不穩(wěn)定,如果我們正好在這個過程中對信號進行采樣,則結果是不確定的,可能是‘0’也可能是‘1’。因此在同步電路中,必須保證在采樣的時刻(時鐘邊沿)信號必須是穩(wěn)定狀態(tài)。這在時鐘頻率很高,和跨時鐘域數(shù)據(jù)傳輸時是很有挑戰(zhàn)的。而在異步設計中,由于控制信號本身就和數(shù)據(jù)信號的狀態(tài)相關,可以比較容易的解決這個問題。

Higher performance function units, which provide average-case (i.e. data-dependent) completion rather than worst-case completion.

使用異步設計,有可能實現(xiàn)更高性能的功能單元。這是因為在同步設計中,由于大家都在相同時鐘下工作,最小的時鐘周期必須保證電路在信號傳輸?shù)淖畈钋闆r(worst-case)下仍然能正確工作,所以整體性能被最差的點限制。而異步設計中,每一級完成操作的時間只和本級相關,整體性能是平均的結果,因此可能在整體上超過同步電路。可以說異步設計如果發(fā)揮“出色”,在性能上是可以超過同步設計的,當然這對技術能力是個巨大的挑戰(zhàn)。

Early completionof a circuit when it is known that the inputs which have not yet arrived are irrelevant.

當知道尚未到達的輸入數(shù)據(jù)與功能不相關時,可以提前早完成這一級電路的操作。

Lower power consumption because no transistor ever transitions unless it is performing useful computation...Also, clock drivers can be removed which can significantly reduce power consumption. However, when using certain encodings, asynchronous circuits may require more area, which can result in increased power consumption if the underlying process has poor leakage properties (for example, deep submicrometer processes used prior to the introduction ofHigh-k dielectrics).

低功耗是可能異步電路在宣傳中最多的提法。原因也很簡單,在沒有數(shù)據(jù)發(fā)生變化的時候,異步電路是不工作的。此外,在同步電路中我們需要很多的時鐘驅(qū)動電路來保證全局時鐘信號的質(zhì)量,這也非常耗電。異步電路當然沒有這個問題。

但是,在說異步電路的功耗低的時候,我們必須相當謹慎。首先,異步電路需要額外的控制信號,當使用某些編碼時,異步電路可能需要更多面積,而更多的面積意味著更大的靜態(tài)功耗。我們知道,CMOS工藝尺寸越小,靜態(tài)功耗在整體功耗里所占比例越大。因此,異步電路雖然只在必要時工作,但整體在能耗上的表現(xiàn)還是需要認真分析才能有準確結果。第二,目前同步設計也會采用各種低功耗設計手段,比如門控時鐘技術等等,對比的時候應該考慮這個因素。

"Elastic" pipelines, which achieve high performance while gracefully handling variable input and output rates and mismatched pipeline stage delays.

異步電路可能實現(xiàn)“彈性”流水線,這個話題在[2]中有非常詳細的說明,確實是“gracefully”。

Freedom from the ever-worsening difficulties of distributing a high-fan-out, timing-sensitive clock signal.

之前已經(jīng)提到,目前的數(shù)學芯片設計中的復雜時鐘信號已經(jīng)是一個最有挑戰(zhàn)性的問題。在一個芯片設計項目中,需要把大量的精力放在時鐘樹的設計和驗證上。

Better modularity and composability.

更好的模塊化和可組合性?這個可能還是強調(diào)異步電路的控制完全在本地進行,可以比較好的集成。

Far fewer assumptions about the manufacturing process are required (most assumptions are timing assumptions).

目前的芯片設計,必須對生產(chǎn)工藝做很多假設,特別是時序上的問題。而對異步電路來說,這個問題要簡單一些。

Circuit speed adapts to changing temperature and voltage conditions rather than being locked at the speed mandated by worst-case assumptions.

相對而言,異步電路的速度可以比較好的適應變化的溫度和電壓條件,而不是必須考慮最壞情況。換句話說,如果溫度,電壓等條件發(fā)生變化,導致電路延時變大,異步電路本身就可以適應這種變化,“自動”降低速度,而不會發(fā)生功能的錯誤。

Immunity to transistor-to-transistor variability in the manufacturing process, which is one of the most serious problems facing the semiconductor industry as dies shrink.

對制造過程中的variation可以比較好的適應。而這個問題隨著工藝尺寸的縮小,是半導體行業(yè)面臨的最嚴重的問題之一。

Less severeelectromagnetic interference(EMI). Synchronous circuits create a great deal of EMI in the frequency band at (or very near) their clock frequency and its harmonics; asynchronous circuits generate EMI patterns which are much more evenly spread across the spectrum.

電磁干擾(EMI)問題相對要少。 同步電路的時鐘信號,在其時鐘頻率及其諧波處(或非常接近)的頻帶內(nèi)產(chǎn)生大量EMI; 異步電路會產(chǎn)生EMI,但其模式在整個頻譜上是均勻分布的。

In asynchronous circuits, local signaling eliminates the need for global synchronizationwhich exploits some potential advantages in comparison with synchronous ones. They have shown potential specifications in low power consumption, design reuse, improved noise immunity and electromagnetic compatibility. Asynchronous circuits are more tolerant to process variations and external voltage fluctuations.

這個不解釋了,基本是前面所說的優(yōu)勢的一個總結。不過還是強調(diào)一下,這些優(yōu)勢的原因是異步電路“l(fā)ocal signaling”的本質(zhì)特點。

Less stress on the power distribution network. Synchronous circuits tend to draw a large amount of current right at the clock edge and shortly thereafter. The number of nodes switching (and thence, amount of current drawn) drops off rapidly after the clock edge, reaching zero just before the next clock edge. In an asynchronous circuit, the switching times of the nodes are not correlated in this manner, so the current draw tends to be more uniform and less bursty.

還是由于不需要一個強有力的全局時鐘,異步電路中對供電網(wǎng)絡的壓力也會減輕。

小結一下,異步電路還是有很多特點的,我們不能簡單的說一句“異步電路可以降低功耗”就作為概括。它的很多優(yōu)勢都是源于“l(fā)ocal signaling”的基本特點。抓住這一點,對于思考它在特定應用的作用非常重要。

劣勢:

Area overhead may be up to double the number of circuit elements (transistors), due to addition of completion detection and design-for-test circuits.

由于增加了控制和用于DFT的電路,異步電路的面積開銷可能高達同步設計的的兩倍。

Fewer people are trained in this style compared to synchronous design.

與同步設計相比,了解這種風格的人要少很多。當然,這也是因為在實際設計中用的少的原因。

Synchronous designs are inherently easier to test and debug than asynchronous designs.However, this position is disputed by Fant, who claims that the apparent simplicity of synchronous logic is an artifact of the mathematical models used by the common design approaches.

與異步設計相比,同步設計更易于測試和調(diào)試。當然,這一觀點也有爭議。

Clock gatingin more conventional synchronous designs is an approximation of the asynchronous ideal, and in some cases, its simplicity may outweigh the advantages of a fully asynchronous design.

這一點之前已經(jīng)提到了,同步設計中的時鐘門控是異步設計的一種近似,并且在某些情況下,其簡單性帶來的好處要遠比異步設計帶來的好處多。

Performance (speed) of asynchronous circuits may be reduced in architectures that require input-completeness (more complex data path).

在需要輸入完整性(更復雜的數(shù)據(jù)路徑)的結構中,異步電路的性能(速度)可能會降低。這一點我也沒想到很好的例子。

Lack of dedicated, asynchronous design-focused commercialEDAtools.

缺乏專用于異步設計的商用EDA工具。由于現(xiàn)在芯片設計的復雜度越來越高,EDA工具對芯片設計來說是不可替代的,因此這一點也是我們對異步電路的實用性詬病最多的地方。

異步電路曾一度在高性能處理器和低功耗設計領域占有重要地位的,但隨著同步設計更快的發(fā)展,異步電路越來越邊緣化;而用的人越少,這種傾向就更加嚴重。總的來說,異步電路目前還是“異類”,真正了解并且有經(jīng)驗的人非常少。沒有EDA工具的支持下,做一個大型設計幾乎是mission impossible。

???

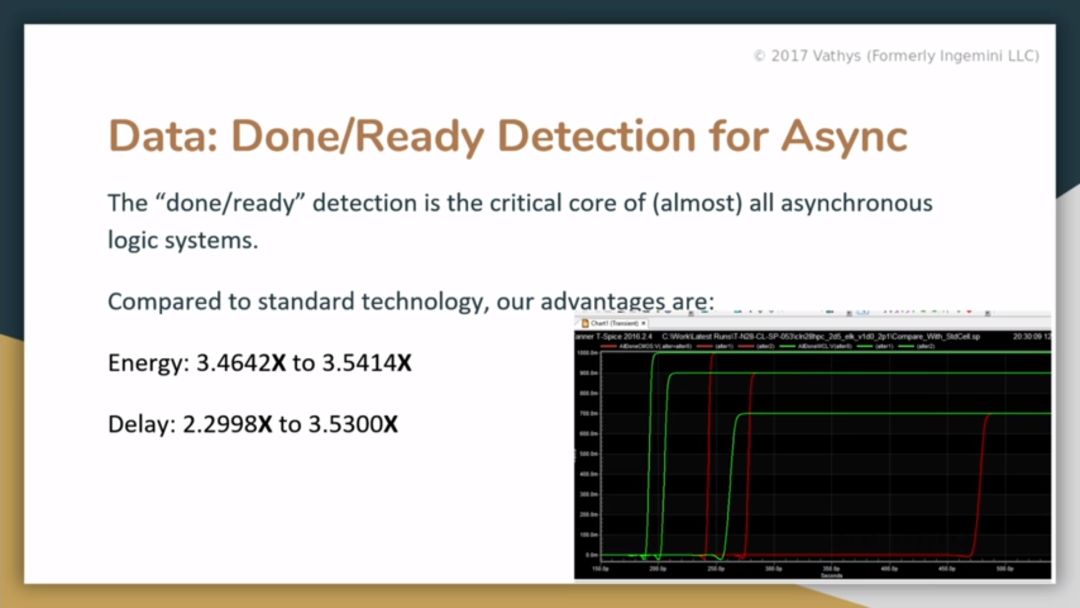

異步設計雖然比較冷門,但在AI芯片領域,還是看到一些有趣的嘗試。特別是在類腦計算(Neuromorphic)芯片中,異步電路是一個比較普遍的選擇。

如Intel的Loihi論文[3]所說:

“Biological neural networks are fundamentally asynchronous, as reflected by the absence of an explicit synchronization assumption in the continuous time SNN model given in the Spiking Neural Networks section. Accordingly, asynchronous design methods have long been seen as the appropriate tool for prototyping SNNs in silicon, and most published chips to date use this methodology.Loihi is no different, and, in fact, the asynchronous design methodology developed for Loihi is the most advanced of its kind. For rapid neuromorphic design prototyping, we extended and improved on an earlier asynchronous design methodology used to develop several generations of commercial Ethernet switches. In this methodology, designs are entered according to a top-down decomposition process usingthe CAST and CSP languages...

Given a hierarchical design decomposition written in CSP, a pipeline synthesis tool converts the CSP module descriptions to Verilog representations that are compatible with standard EDA tools.”

這段話里我們可以看到一些重要信息。1.生物神經(jīng)網(wǎng)絡從根本上說是異步的,因此類腦芯片使用異步電路也是很自然的選擇;2. Loihi開發(fā)的異步設計方法是同類中最先進的。設計使用CAST和CSP語言,采用自頂向下的設計過程。3. 在使用了CSP描述之后,他們使用了一個“pipeline synthesis”工具把CSP描述翻譯成Verilog,之后的流程就和目前標準的EDA工具流程兼容了。

其實,Loihi的設計方法可以給我們一些啟示,因為這種設計方法盡可能的把傳統(tǒng)EDA工具無法支持的部分限定到了最小的范圍。這樣,我們之前提到的目前EDA工具和異步設計無法兼容的問題就得到一定的緩解。當然,具體的設計和驗證的細節(jié)我們還不得而知。

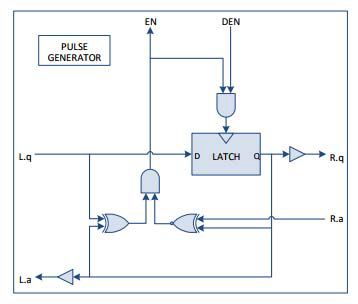

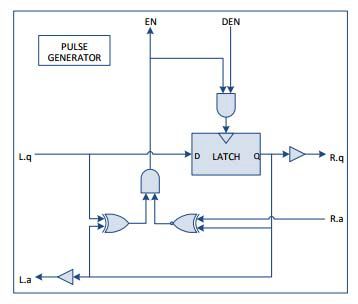

以下是Loihi中的Bundled data pipeline和Bundled data pulse generator電路,實現(xiàn)的就是前面介紹的2-phase bundled-data的機制。

???

除了類腦計算外,目前的ML加速器和處理器很多也采用了數(shù)據(jù)流驅(qū)動的結構。因此,異步設計應該可能在其中發(fā)揮一定的作用。但由于ML加速芯片和類腦計算芯片在基本處理和數(shù)據(jù)傳輸?shù)男枨笊嫌休^大的差別,目前把異步電路用在其中的嘗試還不是主流。雖然我們也看到一些宣傳中提到異步設計的說法,但還不知道實現(xiàn)細節(jié)和設計的方法。在這種情況下,還很難斷言異步設計能在ML芯片中發(fā)揮多大作用。

本文主要希望使讀者對異步電路有一個比較全面和公平的認識。正如我多次說過的,脫離應用環(huán)境,很難評價一個架構的優(yōu)劣。放在AI芯片的環(huán)境中,異步電路的一些特色確實可能發(fā)揮作用。大家可以把異步電路作為一種選擇放進自己的工具箱,但也應該看到,它并非輕松就能駕馭的武器。

-

異步電路

+關注

關注

2文章

48瀏覽量

11354 -

AI芯片

+關注

關注

17文章

1983瀏覽量

35908

原文標題:“傳說中”的異步電路是否能在AI芯片中異軍突起?(純干貨!)

文章出處:【微信號:eetop-1,微信公眾號:EETOP】歡迎添加關注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

異步電路原理及其優(yōu)勢和劣勢,并通過Intel的Loihi芯片看看它的實現(xiàn)

異步電路原理及其優(yōu)勢和劣勢,并通過Intel的Loihi芯片看看它的實現(xiàn)

評論