文章來源:學(xué)習(xí)那些事

原文作者:小陳婆婆

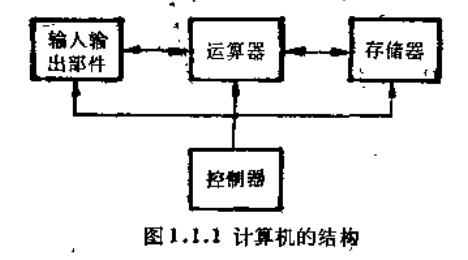

本文介紹了存儲器測試中的晶圓揀選工作。

在半導(dǎo)體存儲器測試中,測試圖形(Test Pattern)是檢測故障、驗證可靠性的核心工具。根據(jù)測試序列長度與存儲單元數(shù)N的關(guān)系,測試圖形可分為N型、N2型和N3/?型三大類。

以下從行業(yè)視角,對這三類測試圖形進(jìn)行技術(shù)解析與案例分享,分述如下:

N型測試圖形

N2型測試圖形

N3/?型測試圖形

N型測試圖形

N型測試圖形:基礎(chǔ)故障的“篩查利器”

N型測試圖形的測試序列長度與N成正比,聚焦于存儲單元、輸入/輸出緩沖器等基礎(chǔ)模塊的故障檢測。

一、 全“0”/全“1”圖形

測試原理:按地址順序向所有存儲單元寫入全“0”或全“1”,再按相同順序讀出并比較。

行業(yè)價值:

優(yōu)勢:可檢測輸入緩沖器、輸出驅(qū)動器及存儲單元的固定故障(Stuck-at Fault)。

局限:幾乎無法檢測地址解碼器故障(如地址線短路)。

案例:某DRAM芯片通過全“0”測試后,發(fā)現(xiàn)輸出驅(qū)動器存在固定“0”故障,導(dǎo)致數(shù)據(jù)總線沖突。

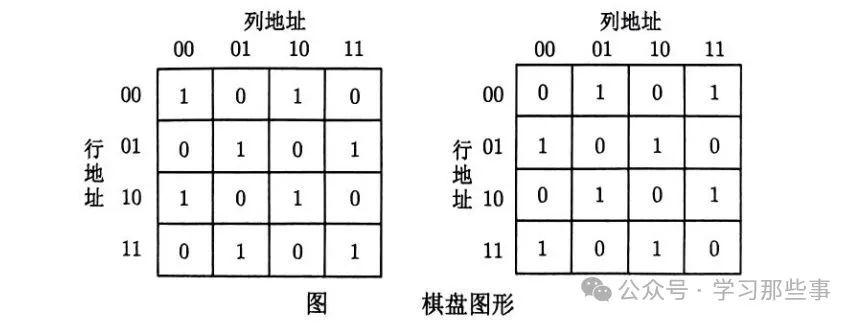

二、棋盤圖形(Checkerboard)

測試原理:向相鄰存儲單元交替寫入“0”和“1”,形成棋盤狀分布。

行業(yè)價值:

優(yōu)勢:可檢測相鄰單元間的干擾故障(如電荷共享)。

局限:對地址故障檢測能力有限。

案例:某SRAM芯片在棋盤測試中,發(fā)現(xiàn)相鄰單元在寫入相反數(shù)據(jù)時出現(xiàn)位翻轉(zhuǎn),定位為字線耦合電容過大。

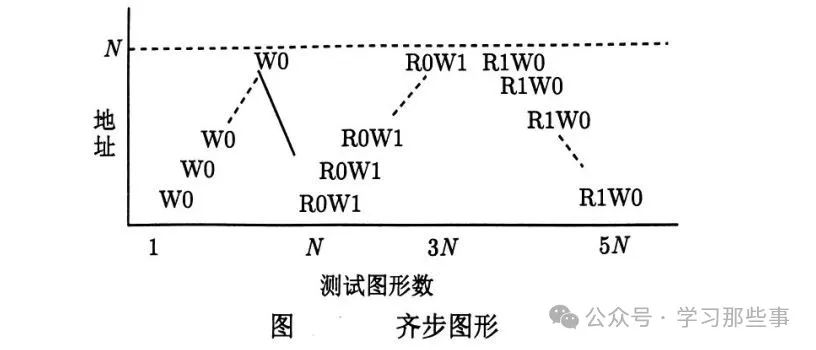

三、 齊步圖形(Marching Pattern)

測試原理:在全“0”或全“1”背景上,按地址順序逐個讀寫并改寫存儲單元,再反向重復(fù)。

行業(yè)價值:

優(yōu)勢:可檢測地址故障(如地址線開路)和數(shù)據(jù)保持故障。

標(biāo)準(zhǔn):JEDEC標(biāo)準(zhǔn)中March C+算法即基于此原理,覆蓋95%以上的存儲器故障。

案例:某NAND Flash通過齊步測試發(fā)現(xiàn)地址解碼器存在偏移故障,導(dǎo)致連續(xù)地址映射錯誤。

N2型測試圖形

N2型測試圖形:地址與數(shù)據(jù)故障的“雙重獵手”

N2型測試圖形的測試序列長度與N2成正比,通過全面覆蓋地址與數(shù)據(jù)組合,檢測復(fù)雜故障。

一、走步圖形(Walking Pattern)

測試原理:以某一存儲單元為基準(zhǔn),逐次寫入反碼并檢測其他單元是否受干擾。

行業(yè)價值:

優(yōu)勢:可檢測存儲單元間干擾(如行/列相鄰干擾)。

案例:某DRAM芯片在走步測試中,發(fā)現(xiàn)某字線上的單元在寫入反碼時,相鄰字線單元出現(xiàn)位翻轉(zhuǎn),定位為字線間距過小。

二、 跳步圖形(Galloping Pattern)

測試原理:在走步圖形基礎(chǔ)上,每次檢測后增加對基準(zhǔn)單元的復(fù)核。

行業(yè)價值:

優(yōu)勢:覆蓋所有地址與數(shù)據(jù)變化組合,檢測隱蔽故障。

局限:測試時間較長,適用于高可靠性要求場景(如汽車電子)。

案例:某MRAM芯片通過跳步測試發(fā)現(xiàn)讀出放大器存在閾值漂移,導(dǎo)致數(shù)據(jù)誤判。

三、 跳步寫恢復(fù)圖形(Galloping Write Recovery)

測試原理:在寫操作后,持續(xù)檢測基準(zhǔn)單元內(nèi)容是否受干擾。

行業(yè)價值:

優(yōu)勢:專用于檢測寫操作引發(fā)的干擾故障(如寫恢復(fù)時間不足)。

案例:某ReRAM芯片在跳步寫恢復(fù)測試中,發(fā)現(xiàn)寫操作后相鄰單元出現(xiàn)數(shù)據(jù)翻轉(zhuǎn),定位為寫驅(qū)動電路設(shè)計缺陷。

N3/?型測試圖形

N3/?型測試圖形:大容量存儲器的“效率革命”

隨著存儲器容量向Tb級演進(jìn),N2型測試圖形的時間成本激增。N3/?型測試圖形通過優(yōu)化測試策略,將序列長度壓縮至N3/?,成為大容量存儲器的首選。

一、 正交走步圖形(Orthogonal Walking)

測試原理:基準(zhǔn)單元在地址空間移動時,僅檢測其所在行/列的干擾。

行業(yè)價值:

優(yōu)勢:測試時間縮短至N3/?,同時保持對行/列干擾的檢測能力。

案例:某3D NAND芯片通過正交走步測試,發(fā)現(xiàn)層間干擾導(dǎo)致的數(shù)據(jù)保持失效。

二、 對角線走步圖形(Diagonal Walking)

測試原理:基準(zhǔn)單元沿存儲矩陣主對角線移動,其他單元全面檢測。

行業(yè)價值:

優(yōu)勢:進(jìn)一步壓縮測試時間,適用于大規(guī)模陣列。

局限:對非對角線方向的干擾檢測能力較弱。

案例:某CMOS圖像傳感器通過該測試,發(fā)現(xiàn)像素陣列對角線方向的耦合噪聲。

三、移動對角線圖形(Moving Diagonal)

測試原理:每次移動對角線后,重新寫入并檢測所有單元。

行業(yè)價值:

優(yōu)勢:平衡測試時間與覆蓋率,適用于中等規(guī)模存儲器。

案例:某LPDDR5芯片通過該測試,發(fā)現(xiàn)多bank并行訪問時的時序沖突。

行業(yè)趨勢:從“全面覆蓋”到“智能篩選”

四、現(xiàn)代存儲器測試正面臨兩大挑戰(zhàn)

容量爆炸:Tb級存儲器使N2型測試時間長達(dá)數(shù)小時,需通過壓縮算法(如CompactTest)將時間壓縮至分鐘級。

低功耗需求:移動設(shè)備對測試功耗提出嚴(yán)苛要求,需采用動態(tài)電壓調(diào)整(DVS)技術(shù)降低測試能耗。

從N型到N3/?型測試圖形,半導(dǎo)體行業(yè)在測試效率與故障覆蓋率之間不斷尋求平衡。隨著3D集成、存算一體等新技術(shù)涌現(xiàn),測試圖形設(shè)計正從“經(jīng)驗驅(qū)動”向“AI驅(qū)動”演進(jìn),通過機(jī)器學(xué)習(xí)預(yù)測故障模式,實現(xiàn)測試資源的精準(zhǔn)配置。未來,測試圖形將成為連接芯片設(shè)計與制造工藝的“智能紐帶”,持續(xù)推動存儲器技術(shù)的可靠性邊界。

-

測試

+關(guān)注

關(guān)注

8文章

5628瀏覽量

128298 -

存儲器

+關(guān)注

關(guān)注

38文章

7634瀏覽量

166404 -

晶圓

+關(guān)注

關(guān)注

52文章

5118瀏覽量

129161

原文標(biāo)題:晶圓揀選——存儲器測試

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導(dǎo)體所】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

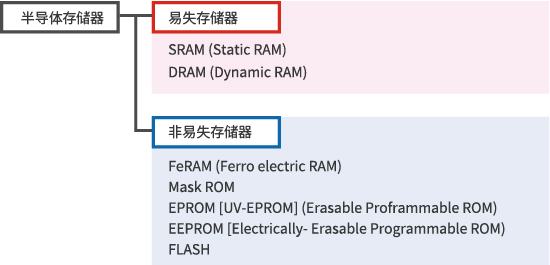

什么是半導(dǎo)體存儲器

半導(dǎo)體存儲器課件(PPT電子教案)

半導(dǎo)體存儲器,半導(dǎo)體存儲器原理圖解

半導(dǎo)體存儲器芯片的基本結(jié)構(gòu)解析

半導(dǎo)體存儲器及其測試.pdf

存儲器集成電路測試,記憶體積體電路測試,Memory IC Test

半導(dǎo)體存儲器測試圖形技術(shù)解析

半導(dǎo)體存儲器測試圖形技術(shù)解析

評論