概述

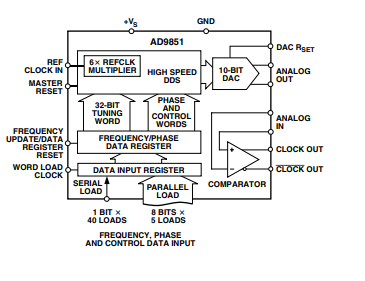

AD9851是一款高度集成的器件,采用先進(jìn)的DDS技術(shù),內(nèi)置一個高速、高性能數(shù)模轉(zhuǎn)換器和比較器,共同構(gòu)成數(shù)字可編程頻率合成器和時鐘發(fā)生器。以精密時鐘源作為基準(zhǔn)時,AD9851能產(chǎn)生一個頻率穩(wěn)定、相位可編程的數(shù)字化模擬輸出正弦波。該正弦波可以直接用作頻率源,或在內(nèi)部轉(zhuǎn)換為適合捷變時鐘發(fā)生器應(yīng)用的方波。

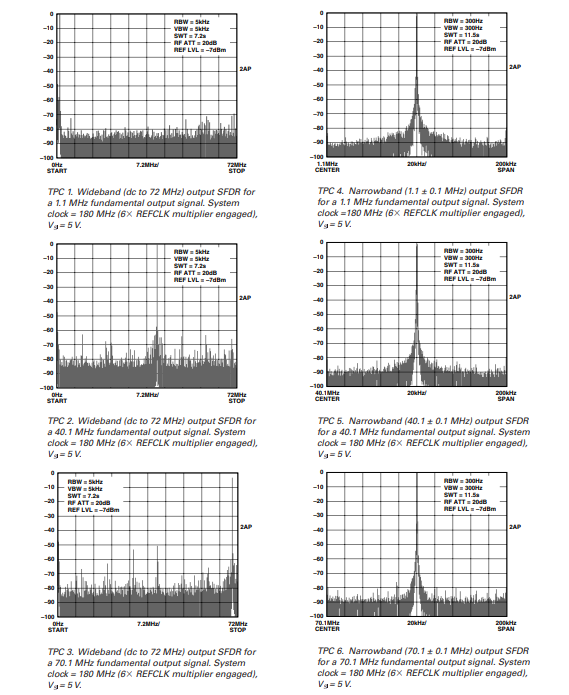

AD9851的創(chuàng)新型高速DDS內(nèi)核提供一個32位頻率調(diào)諧字;對于180 MHz基準(zhǔn)時鐘,輸出調(diào)諧分辨率可以達(dá)到0.040 Hz。AD9851內(nèi)置獨(dú)特的X6基準(zhǔn)時鐘乘法器電路,無需高速參考振蕩器。該6X PLL乘法器對無雜散動態(tài)范圍(SFDR)和相位噪聲特性的影響極小。該器件還提供5位數(shù)字控制相位調(diào)制,使其輸出能夠以180°、90°、45°、22.5°、11.25°及其任意組合的增量發(fā)生相移。

數(shù)據(jù)表:*附件:AD9851 180MHz完整DDS頻率合成器技術(shù)手冊.pdf

特性

- 180 MHz時鐘速率,具有可選6x基準(zhǔn)時鐘乘法器

- 片內(nèi)高性能10位DAC和具遲滯特性的高速比較器

- SFDR >43 dB (70 MHz AOUT)

- 32位頻率調(diào)諧字

- 簡化的控制接口:并行或串行異步加載格式

- 5位相位調(diào)制與偏移能力

- 比較器抖動:小于80 ps 峰峰值 (20 MHz)

- 2.7 V至5.25 V單電源供電

- 低功耗:555 mW (180 MHz)

- 省電功能:4 mW (2.7 V)

- 超小型28引腳SSOP封裝

框圖

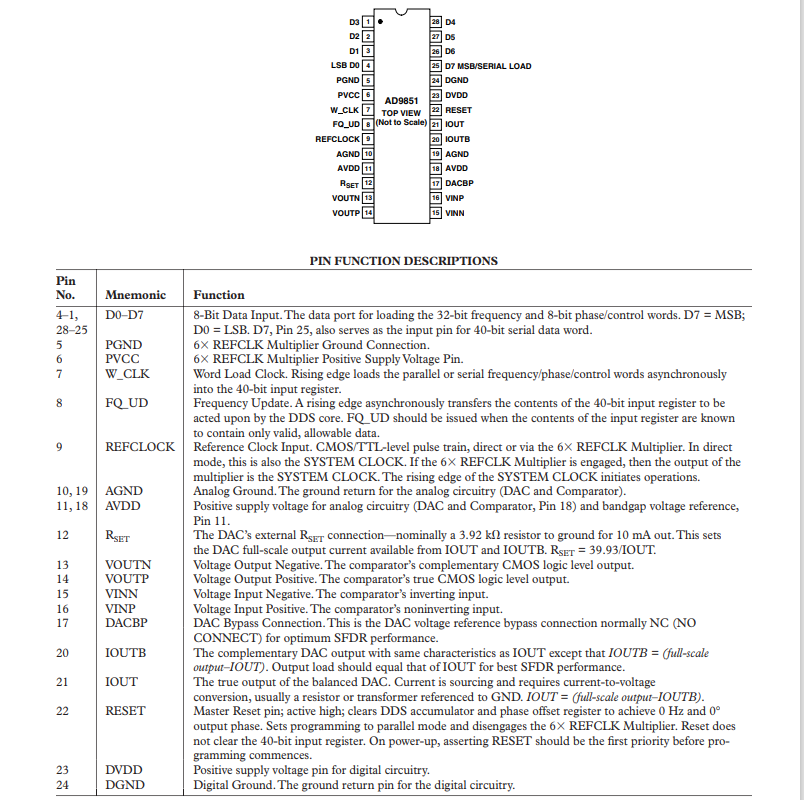

引腳配置描述

典型性能特征

工作原理與應(yīng)用

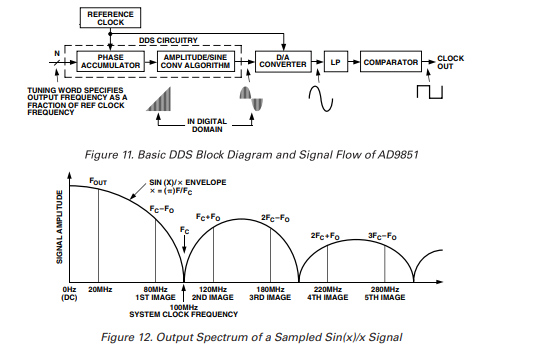

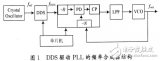

AD9851采用直接數(shù)字合成(DDS)技術(shù),通過數(shù)控振蕩器(NCO)生成頻率/相位可調(diào)的正弦波。數(shù)字正弦波通過內(nèi)部10位高速數(shù)模轉(zhuǎn)換器(D/A轉(zhuǎn)換器)轉(zhuǎn)換為模擬正弦波。板載高速比較器可將模擬正弦波轉(zhuǎn)換為低抖動、與TTL/CMOS兼容的輸出方波。DDS技術(shù)是一種創(chuàng)新的電路架構(gòu),允許完全數(shù)字控制頻率、相位和幅度,從而實(shí)現(xiàn)高分辨率的增量輸出頻率選擇。AD9851在180 MSPS的頻率下可實(shí)現(xiàn)約0.04 Hz的頻率分辨率。用戶可選擇直接使用參考時鐘,或啟用6倍REFCLK乘法器。AD9851的輸出波形始終是連續(xù)的,一個輸出頻率的變化不會影響另一個頻率。

AD9851的基本功能框圖和信號流程如圖11所示。

DDS電路本質(zhì)上是一個數(shù)字頻率合成器,其增量分辨率由系統(tǒng)時鐘和相位累加器調(diào)諧字中的位數(shù)(N)決定。相位累加器是一個可變模計(jì)數(shù)器,每次接收到時鐘脈沖時,其存儲的值都會增加。當(dāng)計(jì)數(shù)器達(dá)到滿量程時,它會循環(huán),使相位累加器的輸出相位連續(xù)。調(diào)諧字設(shè)置計(jì)數(shù)器的模數(shù),這實(shí)際上決定了每個時鐘脈沖時相位累加器中添加的增量(Δ相位)的大小。添加的值越大,下一個時鐘脈沖時相位累加器循環(huán)的速度就越快,從而導(dǎo)致輸出頻率越高。

AD9851采用創(chuàng)新的14位三角函數(shù)算法,以數(shù)學(xué)方式將32位相位累加器的值轉(zhuǎn)換為10位量化幅度,并傳遞給DAC。該獨(dú)特算法使用的查找表比傳統(tǒng)方法少得多,有助于AD9851實(shí)現(xiàn)小尺寸和低功耗。

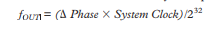

AD9851的輸出頻率、系統(tǒng)時鐘和調(diào)諧字之間的關(guān)系由以下公式確定:

其中:

- ( Delta text{相位} ) = 32位頻率調(diào)諧字的十進(jìn)制值。

- 系統(tǒng)時鐘 = 直接輸入?yún)⒖紩r鐘(單位:MHz),若啟用6倍REFCLK乘法器,則為輸入時鐘(單位:MHz)的6倍。

- ( f_{OUT} ) = 輸出信號頻率,單位為MHz。

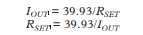

DDS內(nèi)核的數(shù)字正弦波驅(qū)動內(nèi)部高速10位D/A轉(zhuǎn)換器,該轉(zhuǎn)換器針對動態(tài)性能和低毛刺能量進(jìn)行了優(yōu)化,從而實(shí)現(xiàn)了AD9851的低雜散和低抖動性能。DAC可配置為單端(見圖9和圖10)、2倍輸出或差分輸出,輸出值由以下表達(dá)式確定:

由于AD9851的輸出是采樣信號,其頻譜遵循奈奎斯特采樣定理。具體而言,其輸出頻譜包含基波加上采樣時鐘(fs)的整數(shù)倍頻率的混疊信號。所選輸出頻率的圖形表示如圖12所示,顯示了采樣頻譜與混疊圖像的關(guān)系。正常可用帶寬被認(rèn)為從直流擴(kuò)展到1/2系統(tǒng)時鐘。

-

頻率合成器

+關(guān)注

關(guān)注

5文章

293瀏覽量

32704 -

DDS

+關(guān)注

關(guān)注

22文章

671瀏覽量

154013 -

AD9851

+關(guān)注

關(guān)注

4文章

38瀏覽量

23516

發(fā)布評論請先 登錄

DS856直接數(shù)字頻率合成器(DDS)替代AD9851,AD9858,AD9914S-CSL

基于DDS的頻率合成器設(shè)計(jì)介紹

什么是頻率合成器

如何采用DDS實(shí)現(xiàn)頻率合成器的設(shè)計(jì)?

AD9850 DDS 頻率合成器的原理及應(yīng)用

DDS PLL短波頻率合成器設(shè)計(jì)

基于DDS驅(qū)動PLL結(jié)構(gòu)的寬帶頻率合成器的設(shè)計(jì)與實(shí)現(xiàn)

ad9850和ad9851模塊介紹

AD9851 180 MHz完整DDS頻率合成器

AD9851高集成度DDS頻率合成器的電路原理圖數(shù)據(jù)手冊免費(fèi)下載

AD9850:CMOS,125 MHz完整DDS合成器數(shù)據(jù)表

AD9851數(shù)字信號合成變頻資料分享

AN-587: 同步多個基于DDS的頻率合成器AD9850/AD9851

AD9851 180MHz完整DDS頻率合成器技術(shù)手冊

AD9851 180MHz完整DDS頻率合成器技術(shù)手冊

評論