這一個星期認真學習了硬件原理圖的知識,做了一些筆記,方便以后查找。

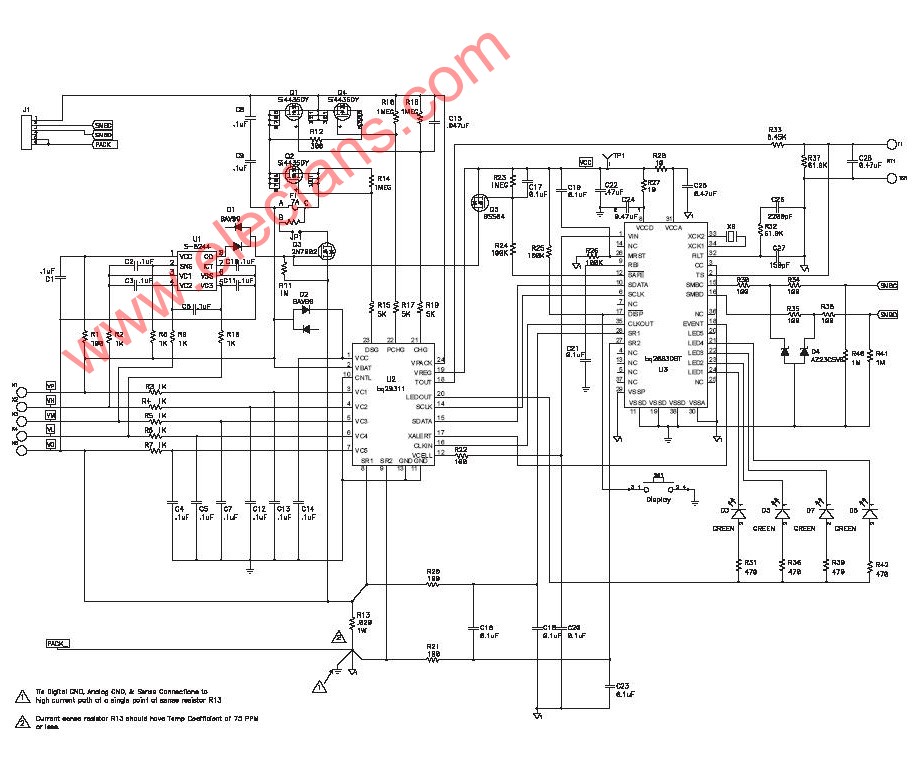

硬件原理圖分為三類

1.管腳類(gpio)和門電路類

輸入輸出引腳,上拉電阻,三極管

與門,或門,非門

上拉電阻:正向標志作用,給懸空的引腳一個確定的狀態

三極管:反向三極管(gpio輸出高電平,NP兩端導通,被控制端導通,電壓為0)->NPN

正向三極管(gpio輸出低電平,PN兩端導通,被控制端導通,電壓為0)->PNP

2.協議類(1.雙方約定一定的信號傳輸協議 2.雙方滿足一定的時序要求),硬件協議就是硬件的工作流程一般只能通過硬件的芯片手冊看出來,比如nand flash只能通過具體的nand芯片的手冊如K9F2G08U0C手冊。看它的工作時序圖看一看出部分硬件協議;

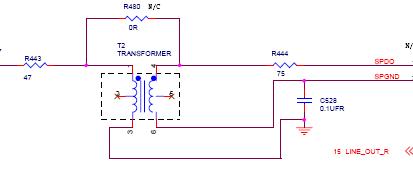

uart: (原理圖接線+硬件協議+軟件啟動流程)

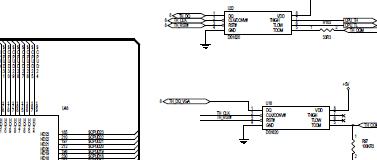

波特率:一秒鐘可以傳輸多少位數據

原理圖:一般是cpu接出兩根線TXD0,RXD0分別為發線,收線,但一般還要接一根地線作為上面兩根數據線的電平參考值0; cpu接出來的兩根數據線的高電平1用3.3v的電壓表示,0用0v表示,但是因為串口線一般有一段距離從開發板到PC,所以3.3v的驅動力是不夠的,一般TXD0,RXD0都要經過一個電平轉換芯片增強電壓的驅動力,數據0用(-9v~-12v表示),數據1用(9v~12v表示)經過電平轉換之后TXD0,RXD0才分別與PC機的兩根數據線相連。

硬件協議:比如2440想要發0x41(0100 0001)這個數據給PC機,那么就要通過TXD0這根數據線發出去。協議過程如下:

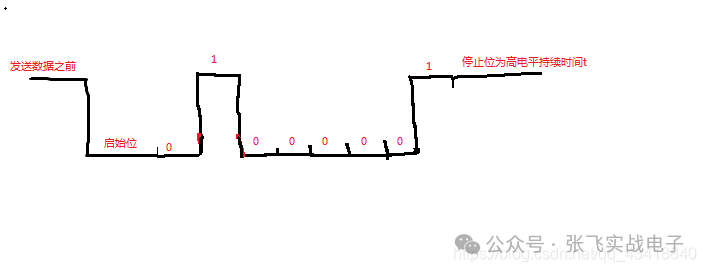

在發送之前2440的TXD0線一直是高電平的,想要發出數據(0100 0001)到數據線上了,先要發出一個啟始位(相當于i2c的start信號),這個啟始位就是拉低數據線為0v并且這個低電平要維持一段時間T(這就是時序),PC機發現自己的RXD0被拉低了T時間段,知道這是對方發出的start信號了,這個啟始位就是雙方約定的協議內容。起始位一般都是一個bit,起始位信號發出去之后,就要將數據01000001一位一位地發送到數據線上,8bit都發送完畢之后,發出停止位(類似于i2c的stop信號,這個停止位一般是1個bit,將數據線的電平拉高并且維持T時間段就行了)具體的協議流程可以觀看圖片:串口協議圖示.png

奇偶檢驗位是指在發完數據位之后在發停止位之前在這兩者之前發一個0或者1作奇偶檢驗

比如如果是奇檢驗,假如數據是0x41(01000001),則校驗位就要發一個1,使得發送的數據的1的個數為奇數。但這個校驗位的數據不會放進數據位里,不影響數據傳輸。一般也可以不用校驗位。數據位一般都用8bit,停止位1bit,起始位和停止位的維持的時間t=1/115200,所以2440和PC機都要遵守一個協議

1.波特率一致,使得雙方的起始位與停止位維持的時間t一致,雙方可以分辨出起始信號和停止信號。

2.數據位一致,都是8bit數據一次傳輸。

3.奇偶檢驗一致。

4.起始位個數一致,一般都是1位,而且免設置。

5.停止位一致。都是1位就行

軟件的啟動流程:看2440的芯片手冊有關uart的接口設置那一章,設置波特率為115200,數據位為8位,奇偶校驗不用,停止位1位,PC段串口接收也同樣這樣設置。雙方協議一致才可以互相認得對方是什么意思才可以通信。

i2c:(原理圖接線+硬件協議+軟件啟動流程)

原理圖:2根線接到i2c的控制器,分別是sclk(時鐘線),sdat(數據線),cpu給i2c外設提供時鐘,并且根據外設的slave id區別從機,8位地址的最多可以接128個從機(2的7次方),10位的地址要發兩次slave id(byte0:11110A9A8)(byte1:A7~A0)

硬件協議(讀):sda/scl兩根線匹配發出start信號(硬件觸發),通過data線將8位的slave id發出去,從機匹配產生ACK響應,重新發出start信號,通過data線將8位的片內地址發出去從機響應ACK,從機通過data線將8bit數據傳回來到i2c控制器。

軟件的啟動流程:具體的驅動流程,要看cpu的i2c control手冊以及i2c外設手冊共同決定。

spi:

原理圖:4根線接到cpu的spi控制器,分別是spimosi(主機輸出從機輸入,寫線),spimiso(主機輸入從機輸出,讀線),時鐘線(clk,cpu給設備提供時鐘),片選線(區別各個設備從機的根據,一般用gpio管腳作片選線)

硬件協議:片選,發出cmd/addr/data(每次8bit)到寫線上,數據開始傳輸,取消片選。

軟件啟動流程:要看cpu的spi control手冊以及spi外設手冊共同決定。

nand: soc有專門的nand接口

一般存儲芯片都是先發出地址信號再發出數據信號,數據信號有專門的數據線DATA0~DATA7,那地址信號是否有對應的ADDR0~ADDR7呢?

nand的芯片手冊會告訴你怎么通過nand芯片的各個引腳來對nand進行訪問(讀寫操作)

nand的操作其實就是訪問一個存儲設備,需要發出命令,發出片內地址,然后啟動數據傳輸,這個原始的訪問過程需要多條管腳相互配合來完成。

寫nand的設備驅動,要先看nand的外設芯片手冊了解了其硬件協議之后,再看主控芯片2440的nand控制器的手冊,兩者配合才可以寫出nand的驅動程序。

假如現在要寫nand的設備驅動,要遵循以下的步驟:

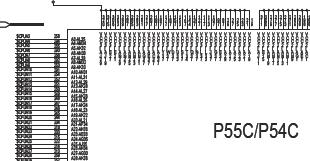

原理圖:nand芯片的各個管腳是怎么接到主控芯片2440的nand控制器的?看原理圖發現

nand芯片上有8根IO線(IO0~IO7)被接到主控芯片2440的LDATA0~LDATA7;

nand芯片上的管腳R/B被接到主控芯片2440的RnB接口;

nand芯片上的管腳CLE被接到主控芯片2440的CLE接口;

nand芯片上的管腳CE被接到主控芯片2440的nFCE接口;

nand芯片上的管腳ALE被接到主控芯片2440的ALE接口;

nand芯片上的管腳WE被接到主控芯片2440的nFWE接口;

nand芯片上的管腳RE被接到主控芯片2440的nFRE接口;

nand芯片上的管腳WP被接到3.3v電源上;

必須明白一點:硬件協議都是通過讀外設的芯片手冊得到的

那nand芯片的這些管腳有什么意義呢?看nand flash的外設芯片手冊發現:

WP:如果這個管腳被拉低那么nand就被寫保護了,現在原理圖上是接死3.3v的電壓,就是一直拉高,那么就是一直取消寫保護;

I/O0 ~ I/O7:寫操作的時候這8根數據線被用作輸入命令,地址和數據,讀操作的時候這8根數據線被用作輸出數據;

CLE:當這個管腳為高電平的時候,主控芯片2440里command register里的數據就會通過I/O0 ~ I/O7發出去;

CE:當這個管腳被拉低的時候,這個設備被選中了,當假如設備正忙的時候強制拉低這個管腳,nand也是不可被訪問的;

ALE:如果這個管腳被拉高,那么主控芯片2440里的addr register里的數據就會通過8根io線發出去;

R/B:這一個管腳表明nand這個設備的狀態,假如這個管腳向2440輸出低電平,那說明nand正忙;

WE:當這個管腳被拉低的時候,數據的運輸的方向為2440->nand,即為寫操作,每拉低一次傳一個字節;

RE:當這個管腳被拉低的時候,數據的運輸方向為2440<-nand,即為讀操作,每拉低一次傳一個字節;

但是明白了這些管腳的意義了好像也不知道怎么訪問nand,比如我想讀devID,我要怎么操作呢?

猜想為:1.管腳CE拉低 2.管腳CLE拉高 3.管腳RE拉低 4.去8根io線那里讀取數據值就行了

硬件協議:有多少種工作模式就有多少種硬件協議。

但是標準的硬件協議還是從nand的芯片手冊找答案:我們發現不同的操作有不同的協議:

如讀ID的協議:

1.先片選(將CE線拉低)。

2.發出讀ID命令信號0x90(將0x90放在IO線上,將CLE線拉高并持續時間段T同時將ALE線拉低并且維持時間t說明IO線上的數據是命令),然后將WE線拉低并且持續時間t(此時已經將0x90作為命令發送出去了);

3.發出地址0x00(將0x00放在IO線上,將ALE線拉高并持續時間段T同時將CLE線拉低并且維持時間t說明IO線上的數據是地址),然后將WE線拉低并且持續時間t(此時已經將0x00作為地址值發送出去)了;

4.從IO線上讀回數據(將RE線拉低一次可以從IO線上讀回一個字節的數據,反復拉低5次就可以讀到5個字節的數據。

5.取消片選(將CE線拉高)。

隨意寫的硬件協議:比如2440想往nand的0x10地址寫入數據0x88;其硬件協議是這樣的:

1.片選(將CE線拉低)

2.發出寫命令0x85(將0x85放在IO0~IO7上,將nand芯片的CLE線拉高并且維持一段時間t同時ALE線要拉低一段時間t(說明io線上的數據作為命令),將WE線拉低并且維持一段時間t->這個時候命令0x85已經發送出去了)

3.發出地址0x10(將0x10放在IO0~IO7上,將nand芯片的CLE線拉低并且同時將ALE線拉高(說明IO線上的數據是地址),將WE線拉低并且維持一段時間t->這個時候地址0x10已經發送出去了)

4.發出數據0x88(將數據0x88放在IO0~IO7上,將nand芯片的CLE,ALE兩根線同時拉低并且維持一段時間(說明IO線上的數據就是純數據),將WE線拉低并且維持一段時間t->這個時候數據0x88已經發送出去了)

5.取消片選(CE線拉高)

隨意讀的硬件協議:比如2440想讀nand芯片的0x10地址的值;其硬件協議是這樣的:

1.片選(將CE線拉低)

2.發出讀命令0x05(將0x05放在IO0~IO7上,將nand芯片的CLE線拉高并且維持一段時間t同時ALE線要拉低一段時間t(說明io線上的數據作為命令),將WE線拉低并且維持一段時間t->這個時候命令0x05已經發送出去了)

3.發出讀命令0xE0(將0xE0放在IO0~IO7上,將nand芯片的CLE線拉高并且維持一段時間t同時ALE線要拉低一段時間t(說明io線上的數據作為命令),將WE線拉低并且維持一段時間t->這個時候命令0xE0已經發送出去了)

4.發出地址0x10(將0x10放在IO0~IO7上,將nand芯片的CLE線拉低并且同時將ALE線拉高(說明IO線上的數據是地址),將WE線拉低并且維持一段時間t->這個時候地址0x10已經發送出去了)

5.讀回數據0x88(將RE線拉低一次就從IO0~IO7上讀到一個字節,這個數據就是之前寫進去的0x88)

6.取消片選(CE線拉高)

軟件驅動設計:就是通過2440的nand控制器去完成上面的各個步驟,比如我想去讀flash的devID

首先看原理圖nand芯片的ALE CLE RnB NCON nFCE nFRE nFWE這些管腳被連到的2440 GPA17,18,19,20,22,可能先要管腳初始化。

1.先片選(NFCONT的bit1置0)

2.發出讀ID命令信號0x90(將0x90寫入NFCMMD寄存器),自動將WE線拉低一段時間

3.發出地址0x00(將0x90寫入NFADDR寄存器),自動將WE線拉低一段時間

4.從IO線上讀回數據(讀寄存器NFDATA),自動將RE線拉低一段時間

5.取消片選(NFCONT的bit1置1)

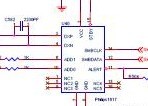

lcd:最關鍵的是看LCD的外設芯片手冊,結合管腳分析各個管腳的作用,確定lcd芯片的電源,屏幕的背光電源的來源;

電路圖:EN表示高電平有效,nEN或者/EN表示低電平有效,或者EN上面有一根橫線也表示低電平有效;

lcd的原理圖:管腳對接并且分析管腳,從lcd屏的插槽開始分析,因為插槽一邊鏈接主控芯片2440,一邊連接lcd芯片;

VCLK: 負責噴槍的移動,ic的內部設計原理是->每來一個時鐘噴槍就會移動在下一個像素的位置;

VSYNC: 水平方向的同步信號,當像素的橫坐標等于圖像的水平像素數量時發出信號告訴噴槍去到下一行像素的起點;

HSYNC: 垂直方向的同步信號,當像素的縱坐標等于圖像的垂直像素數量時發出信號告訴噴槍回到起點(0.0),準備開始下一張圖像的開始描繪;

VD0~VD23: 24根管腳發送像素的RGB數據,每一根線對應一個bit;

DE: data enable數據使能引腳,當這個管腳使能(拉高或拉低),數據線(VD0~VD23)的24bit RGB數據才可以輸出,否則即使時鐘使能噴槍移動,沒有RGB數據,屏幕也只是背光點亮,沒有顏色;

VDD: LCD芯片的內部電源供電,分析原理圖可以得知VDD的電源來自一個電壓轉換芯片,而這個電壓轉換芯片的啟動電壓來自2440的一個GPIO管腳,這個管腳輸出高電壓就會使得電壓轉換芯片輸出電壓供電給LCD芯片的VDD管腳。

LED+,LED-: LCD屏幕的背光電壓,上面的VDD只是給LCD芯片供電,這個LED+,-是給屏幕供電,我們可以看到屏幕亮起來;分析原理圖得知這兩根LED+,-也接來源一個電壓轉換芯片,這個電壓轉換芯片的供電也是來自2440的一個GPIO管腳,2440要使能這個管腳讓其輸出對應的電壓就可以啟動電壓轉換芯片給LED+,-供電從而點亮屏幕背光;

lcd的協議:clk(數據輸出時鐘),vsync(水平同步信號),hsync(垂直同步信號),de(像素數據使能),VD0~VD23(像素RGB數據管腳);

LCD的協議就是這28根線互相配合工作。配置好主控芯片的LCD接口之后(包括各個信號的時序,時鐘這些),lcd芯片的ic內部就會根據時鐘一個時鐘周期一個描繪一個像素的原理

去24根數據線那里取到數據去噴涂在屏幕上(前提是DE管腳使能,24根線的數據得以輸出);clk線負責驅動噴槍并且逐個像素點移動至于是怎樣的移動原理那是ic內部設計的問題

反正主控芯片給時鐘就可以驅動噴槍了,vsync線負責讓噴槍噴滿水平像素之后自動跳到下一行,hsync線負責噴槍的縱坐標到達像素的屏幕的豎直最大像素之后自動回到(0.0)準備開始下一張圖像;

DE線負責讓24根數據線的數據得以輸出到屏幕,如果DE線不使能RGB數據將無法隨著噴槍到達像素點導致噴槍填進去的數據為0,屏幕一直為黑屏。

軟件驅動設計: 電路供電部分:lcd芯片的電壓要供電(可能是驅動某一個gpio管腳輸出電壓給某一個電壓轉換芯片,然后電壓轉換芯片的輸出電壓接到lcd芯片的VDD端)

lcd屏幕的電壓要供電(可能是驅動某一個gpio管腳輸出電壓給某一個電壓轉換芯片,然后電壓轉換芯片的輸出電壓接到lcd芯片的背光屏正電壓,如LED+,LED-)

lcd芯片的負電壓DFF,可能是接到主控芯片的某一個gpio管腳,讓這個管腳輸出低電壓就可以了;

協議部分:就是填寫主控芯片的LCD接口的寄存器,設置時鐘(clk線),設置vsync線的時序,設置hsync線的時序,使能DE,往24根數據線寫像素值。

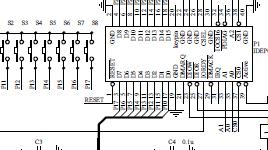

3.類似內存的接口,就是接到內存控制器的那類設備;

sdram,ddr,nand,nor,dm9000:這些設備共用數據線,地址線,靠片選線來區分這些設備;

接到內存控制器上的內存類設備每一個設備都有一根片選線,這根片選線要接到內存控制器對應bank的片選接口,這樣當cpu發出對應bank的地址時內存控制器就會

自動將設備的片選管腳選中,不需要程序手工選中.例如sdram接到內存控制器的bank6(0x30000000~0x380000000),那sdram的片選管腳也要連到主控芯片的內存控制器的GCS6

不同位寬的接線,訪問過程

怎么確定訪問地址,設置內存控制器

cs#:井號也是表示低電平有效的意思;

4.從頭到尾看幾個開發板的原理圖

1.如果原理圖里看到nWAIT接口表示這個設備要使用nwait信號,在memory control的每一個bank都會有一個nwait接口,如果設備的nwait線接到了對應的bank,那么在初始化memory control時就要enable對應的bank的nwait信號;

2.一款芯片的原理圖一般由兩部分組成:核心板,底板;核心板是指SOC(cpu+ddr+net+uart+nand,也包括soc里的片內外設)等cpu相關的,底板是指核心板的下一層(承載核心板的底板),主要是接純外設比如spi設備,i2c設備等等;

3.usb分為host接口,slave接口

5.總結

寫設備驅動的思路:先看原理圖,弄清楚設備芯片的原理圖的各個管腳是什么含義有什么作用分別接到哪里(要結合設備芯片的數據手冊與原理圖一起看才能弄懂);

然后弄明白各個管腳是怎么一起配合實現硬件協議的。(硬件協議可以通過外設芯片手冊的時序后者簡介看明白),反正就是要弄明白各個管腳是

怎樣配合訪問設備芯片的。最后根據外心芯片的時序要求等設置要求通過主控芯片的對應接口配置外設芯片,使其正常工作。

原文鏈接:https://blog.csdn.net/qq_43418840/article/details/118357285

-- END --

免責聲明:本文轉自網絡,版權歸原作者所有,如涉及作品版權問題,請及時與我們聯系,謝謝!

-

芯片

+關注

關注

459文章

52169瀏覽量

436108 -

三極管

+關注

關注

145文章

3653瀏覽量

123951 -

硬件

+關注

關注

11文章

3460瀏覽量

67193

發布評論請先 登錄

想要學習硬件設計(原理圖以及ARM開發)

宏基筆記本PCB原理圖

硬件原理圖學習筆記

硬件原理圖學習筆記

評論