摘要: 本文深入剖析了芯片軟錯誤概率問題,結合 AEC-Q100 與 IEC61508 標準,以 130 納米工藝 1Mbit RAM 芯片為例闡述其軟錯誤概率,探討汽車芯片安全等級劃分及軟錯誤對汽車關鍵系統的影響,分析先進工藝下軟錯誤變化趨勢,并提出相應的應對策略,旨在為芯片在汽車等安全關鍵領域的應用提供理論參考與實踐指導,保障電子系統可靠性。

一、引言

隨著電子技術在汽車領域的廣泛應用,芯片作為核心部件,其可靠性直接關系到車輛的安全性能。其中,軟錯誤這一可靠性問題日益受到關注。軟錯誤是指芯片在運行過程中,因外部環境因素導致其內部存儲狀態或邏輯狀態發生臨時性錯誤,與硬錯誤不同,軟錯誤并不會造成芯片物理損壞,但可能引發系統功能異常。鑒于汽車應用環境的復雜性與高安全性要求,深入研究芯片軟錯誤概率及其應對措施具有極為重要的現實意義。

二、芯片軟錯誤概率分析

依據 AEC-Q100(汽車電子委員會制定的汽車級集成電路應力測試標準)和 IEC61508(電氣 / 電子 / 可編程電子安全系統的功能安全標準)兩大權威標準,選取 130 納米工藝制造的 1Mbit RAM 芯片作為研究對象。研究表明,大氣中子單粒子效應引發的軟錯誤概率超過 1000FIT(Failure In Time,定義為在 10^9 小時內出現一次故障即為 1FIT。例如,某器件失效率為 100FIT,則平均預期可安全工作時間為 10^7 小時)。從數值上看,1000FIT 的軟錯誤概率相對較高,尤其對于汽車剎車等安全等級要求極為嚴苛的應用場景而言,這一概率意味著潛在的巨大安全風險。汽車剎車系統作為車輛安全的關鍵組成部分,其控制芯片一旦遭受軟錯誤,可能導致剎車指令無法準確執行或延遲執行,從而危及駕乘人員生命安全以及道路行車安全。

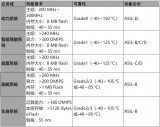

三、汽車芯片安全等級劃分與軟錯誤關聯

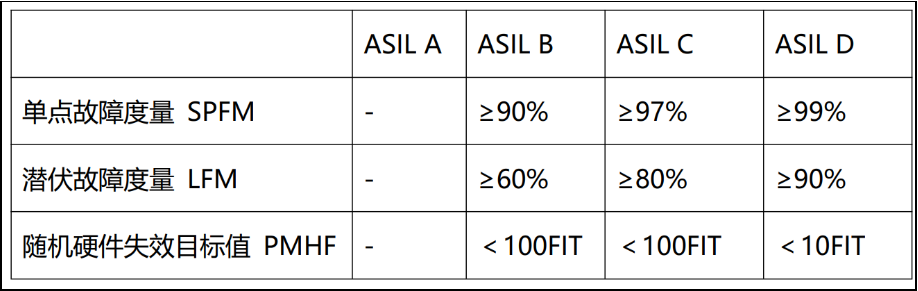

汽車芯片根據其應用場景對應的風險程度,被精細劃分為不同安全等級,依次為 QM、ASIL-A、ASIL-B、ASIL-C、ASIL-D,其中 ASIL-D 為最高等級,代表最嚴格的安全要求。芯片安全等級的劃分依據包括三個關鍵指標的計算,這些指標綜合考量了系統故障對人員、環境等可能造成的危害程度。以 130 納米工藝下的 CMOS 工藝設計為例,當芯片時序存儲容量不斷增加時,其對安全設計的要求呈指數級增長。1000FIT 的故障率已遠超 ASIL-B 的等級要求,這凸顯了在先進工藝推進下,芯片軟錯誤問題對汽車芯片安全等級達標構成的嚴峻挑戰,設計者需在芯片架構、電路設計、軟件算法等多層面協同優化,以提升芯片的抗軟錯誤能力,確保芯片在全生命周期內符合既定安全等級標準。

四、汽車關鍵系統對芯片軟錯誤的敏感性

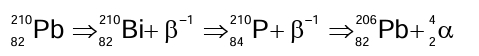

汽車系統的安全等級對所選用的芯片有著明確且嚴格的要求,尤其是 ASIL-D 等級的動力能源、汽車制動、EBS(電子制動系統)等關鍵系統,對控制芯片的要求近乎苛刻。以汽車制動系統為例,其對指令的執行精度與時效性要求極高。若芯片出現軟錯誤,導致制動指令 “隨機故障”,即制動指令未能按預期執行,后果將不堪設想。駕駛員和乘客將面臨著巨大的生命危險,車輛可能因無法及時制動而發生碰撞事故。此外,軟錯誤的來源具有高度不確定性,涵蓋大氣中子、α粒子、電源電壓波動等多種因素,這使得設計者在芯片設計與系統集成過程中,必須全面、系統地考慮每一層級可能出現的軟錯誤,并制定相應的應對方案,構建多層級的容錯機制,保障汽車關鍵系統的可靠性與安全性。

五、先進工藝下芯片軟錯誤趨勢

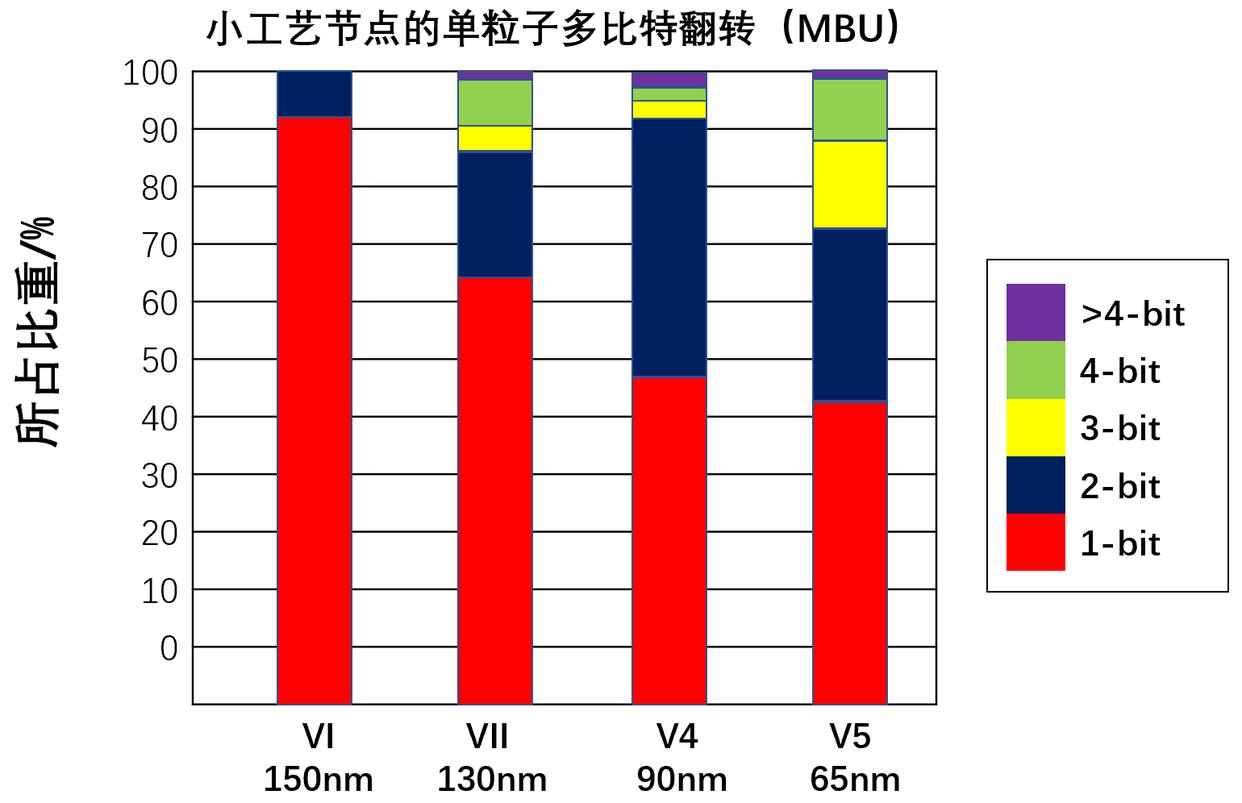

隨著半導體制造工藝的不斷演進,芯片尺寸持續縮小,當前大多芯片已采用 28 納米甚至 7 納米工藝進行生產。然而,工藝的微型化卻帶來了一個不容忽視的問題 —— 器件的容軟錯誤能力顯著下降。在先進工藝下,不僅單比特翻轉(SBF)錯誤概率增加,還出現了更為復雜的多比特翻轉(MBU)錯誤,這進一步加大了故障恢復的難度。研究表明,采用 28 納米 CMOS 工藝設計的器件相較于 130 納米工藝器件,在軟錯誤概率上至少高出 3 個數量級。這一趨勢對系統的安全性設計提出了前所未有的挑戰,迫使芯片設計者與系統工程師必須重新審視傳統的可靠性設計方法,探索適應先進工藝的新型軟錯誤防護策略,以平衡芯片性能提升與系統安全性保障之間的矛盾。

六、芯片軟錯誤應對策略

盡管芯片軟錯誤在一定程度上難以完全避免,但這并不意味著芯片無法在眾多應用場景中得到有效利用。對于商業級器件和普通工業級器件而言,即使發生軟錯誤,通常可通過簡單的重啟或復位操作予以消除,且此類故障對人身財產造成的損害風險較低,可接受一定程度的軟錯誤率。然而,對于涉及人民群眾生命安全的場景,如汽車安全等級達到 ASIL-D 或工業安全要求達到 SIL-1 的場景,就必須對芯片的軟錯誤特性進行嚴格評估與控制。

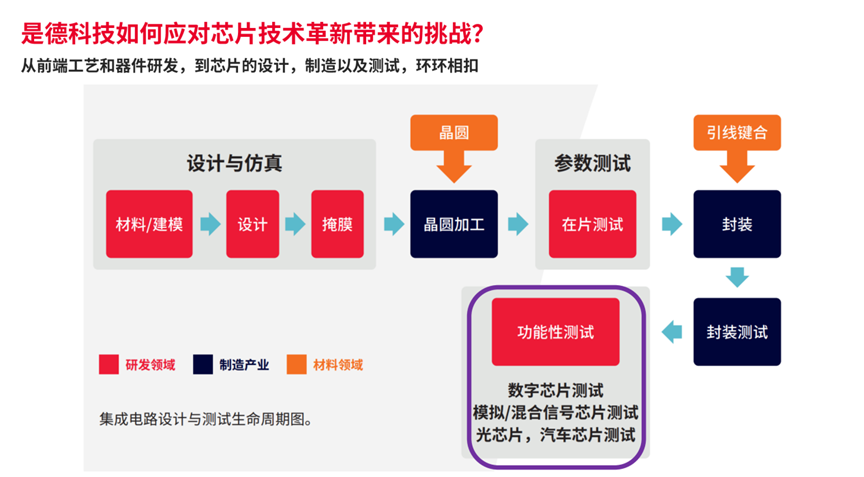

針對器件容軟錯誤的技術方法豐富多樣。在太空環境下,器件往往不計成本地在設計與生產環節采取極端冗余、加固等措施以保障任務成功,因太空環境的特殊性與高風險性使得任何微小的故障都可能導致重大任務失敗。而對于地面器件,由于其應用場景更為廣泛且對成本敏感,在保證安全要求的前提下,追求極致的性價比成為關鍵目標,這就需要在芯片設計、制造工藝選擇、系統架構設計以及軟件開發等多個環節進行權衡與優化,綜合運用多種軟錯誤防護技術,如錯誤檢測與糾正碼(ECC)、冗余設計、時序裕度優化等,以實現芯片在性能、成本與可靠性之間的最佳平衡,滿足不同應用場景對芯片軟錯誤特性的差異化要求。例如,國科安芯的AS32A601車規芯片基于自研工藝級軟錯誤防護技術,支持端到端ECC保護。這種設計能夠有效檢測和糾正存儲器中的軟錯誤,從而提高芯片的可靠性。此外,該芯片還集成了硬件加密模塊,支持AES、SM2/3/4和TRNG等加密算法,能夠有效防止數據在傳輸過程中被篡改或竊取。

七、結論

芯片軟錯誤概率是影響汽車芯片乃至各類電子產品可靠性的重要因素。通過對 130 納米工藝 1Mbit RAM 芯片的分析,結合汽車芯片安全等級劃分以及先進工藝下軟錯誤趨勢的探討,深刻認識到芯片軟錯誤問題的復雜性與嚴峻性。在汽車智能化、電動化、網聯化快速發展的當下,芯片作為核心支撐,其軟錯誤防護技術研發與應用至關重要。未來,隨著芯片制造工藝的持續進步,軟錯誤問題將進一步凸顯,需要芯片設計者、系統集成商、標準制定機構以及科研人員等各方協同合作,不斷探索創新的軟錯誤應對策略與解決方案,從芯片架構設計、制造工藝改進、系統容錯機制構建以及軟件算法優化等多維度入手,全面提升芯片的抗軟錯誤能力,確保汽車電子系統以及其他關鍵應用電子系統的穩定、可靠運行,為人們的出行安全以及社會的數字化發展提供堅實的技術保障。

審核編輯 黃宇

-

芯片

+關注

關注

459文章

52205瀏覽量

436457 -

汽車芯片

+關注

關注

10文章

932瀏覽量

43886

發布評論請先 登錄

東軟睿馳NeuSAR OS榮膺“2025年度汽車芯片生態力產品”

雙核鎖步技術在汽車芯片軟錯誤防護中的應用詳解

共筑國產汽車芯片未來,中國汽車芯片聯盟全體大會即將開啟

東軟睿馳NeuSAR成功適配紫光同芯THA6系列芯片

低α粒子錫膏是如何降低微電子封裝軟錯誤率的?

使用低α粒子錫膏降低微電子封裝的軟錯誤率

芯片軟錯誤概率探究:基于汽車芯片安全設計視角

芯片軟錯誤概率探究:基于汽車芯片安全設計視角

評論