概述

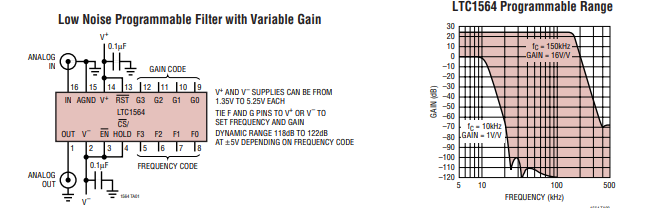

LTC 1564 是一款新型連續時間濾波器,適用于抗混疊、重構和其他頻帶限制應用。使用該器件無需具備其他模擬組件或濾波器專門知識。LTC1564 具有一個模擬輸入引腳和一個模擬輸出引腳。截止頻率 (f C ) 和增益是可編程的,而低通濾波器響應的形狀則是固定的。一個鎖存數字接口負責存儲 fC和增益設定值,也可繞開此接口以直接由引腳進行控制。LTC1564 的工作電壓范圍為 2.7V 至 10V 總值 (單電源或分離型電源),其采用 16 引腳表面貼裝型封裝

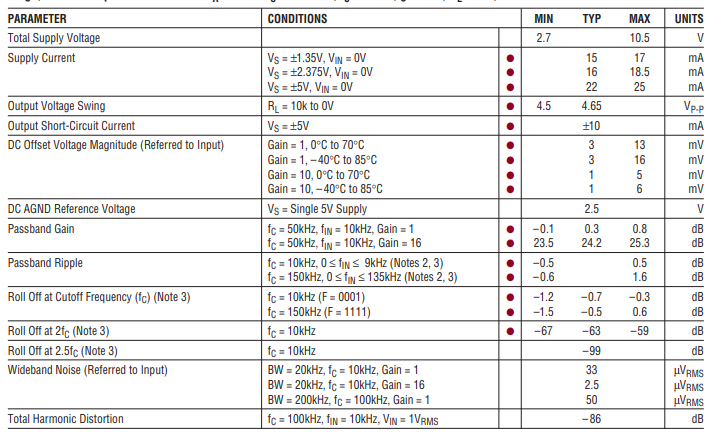

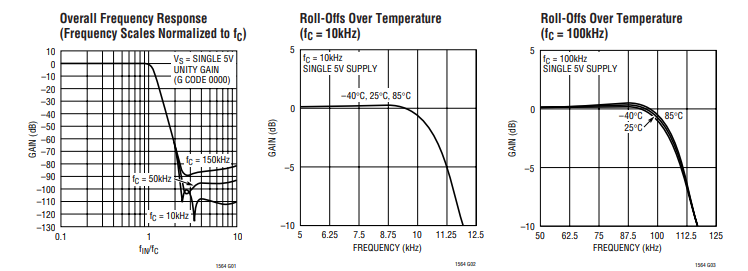

LTC1564 是一款具有兩個阻帶陷波的軌至軌高分辨率 8 階低通濾波器,可在 2.5 倍的通帶截止頻率 fC 下提供大約 100dB 的衰減 (針對 DSP 前端的一項事實標準)。低電平或可變電平信號可利用內置可變增益進行歸一化,當采用一個 ±5V 電源時,對于 122dB (20 個等效位,采用 20kHz f C ) 和 118dB (在 100kHz f C ) 的典型動態范圍 (最大信號電平至最小噪聲之差),這可通過提升增益來降低輸入參考噪聲。

其他頻率響應形狀可根據客戶的要求提供。請與凌力爾特 (現隸屬 ADI) 聯系。

數據表:*附件:LTC1564 10kHz至150kHz數字控制式抗混疊濾波器和4位P.G.A技術手冊.pdf

應用

特性

- 4 位數字控制式 8 階低通濾波器

- f

CUTOFF可調范圍從 10kHz 至 150kHz (以 10kHz 步進)

- f

- 4 位數字控制式可編程增益放大器

- G = 1 至 16 (以 1V/V 步進)

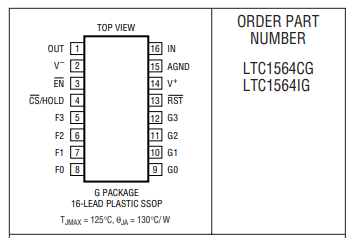

- 小型 16 引腳 SSOP 封裝

- 無外部組件

- 122dB 總系統動態范圍

- 軌至軌輸入和輸出范圍

- 2.7V 至 10V 工作電壓范圍

- 低噪聲靜音模式

- 低功率停機模式

- 采用 16 引腳塑料 SSOP 封裝

典型應用

引腳配置描述

引腳功能

- OUT(引腳1) :模擬輸出。在正常濾波時,它是內部運算放大器的輸出,能夠在電源軌(即**V^{+}和V^{-}之間)間擺動。此輸出設計用于驅動標稱5 kΩ負載和50pF電容。為實現最低信號失真,應盡量輕載。它可驅動低至5 kΩ的電阻負載,但失真可能會增加,輸出電流將限制在約±10mA。電容高于50pF時,可能需隔離電阻為500Ω或更高,以保持交流穩定性。在靜音狀態(F碼為0000或RST = 0)下,該引腳在正常濾波時的功能與正常情況相同,但增益變為零,輸出噪聲降低。在關斷狀態(overline{EN} = 1或overline{EN}**開路或短路)下,LTC1564電路中的大部分器件關閉,OUT引腳呈現高阻抗狀態。

- V^{-},V^{+}(引腳2、14) :電源引腳。**V^{+}和V^{-}**引腳應使用0.1μF電容旁路至接地層,布線時應盡量縮短距離。干凈的電源和低阻抗接地對于高動態范圍和高抑制比很重要(更多詳細信息見AGND)。建議使用低噪聲線性電源。開關電源不推薦,因為它們不可避免地存在將開關噪聲耦合到信號路徑的風險,從而降低動態范圍。

- overline{EN}(引腳3) :CMOS電平數字芯片使能輸入。邏輯1或開路電路會使該引腳進入關斷模式,LTC1564關閉,輸出呈高阻抗狀態。如果在關斷狀態下鎖存CS/HOLD = 1時F和G位被鎖存(保持其內容)。**overline{EN}輸入處的小上拉電流源會使LTC1564在overline{EN}引腳懸空時進入關斷狀態。因此,用戶必須將overline{EN}**引腳連接到邏輯0(V^{-},或可選0V ±5V電源),以實現濾波器正常工作。

- CS/HOLD(引腳4) :CMOS電平數字使能輸入,用于鎖存F和G位。邏輯0使鎖存器透明,F和G輸入可直接控制濾波器的截止頻率和增益。邏輯1將這些輸入值鎖存到邏輯轉換前的狀態。該引腳在開路時由于小電流源會變為邏輯0(V^{-})(見電氣特性,注5)。

- F3,F2,F1,F0(引腳5、6、7、8) :CMOS電平數字頻率控制(“F碼”)輸入。F3是最高有效位(MSB)。這些引腳設置LTC1564的截止頻率f_{C},通過內部鎖存器實現。

電特性

典型性能特征

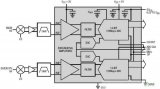

框圖

-

濾波器

+關注

關注

162文章

8039瀏覽量

180699 -

數字控制

+關注

關注

2文章

192瀏覽量

26112

發布評論請先 登錄

ADS7066有可編程濾波器,請問使用該濾波器時,是否可以簡化設計抗混疊濾波的截止頻率?

LTC1564濾波器驅動LTC1608 16位500ksps模數轉換器

ADC的過采樣與抗混疊濾波器

LTC1564 10kHz 至 150kHz 數字控制式抗混疊濾波器和 4 位 P.G.A

LTC1564 10kHz至150kHz數字控制式抗混疊濾波器和4位P.G.A技術手冊

LTC1564 10kHz至150kHz數字控制式抗混疊濾波器和4位P.G.A技術手冊

評論