概述

AD8330是一款DC至150 MHz寬帶寬可變增益放大器,適合要求完全差分信號通路、低噪聲、精確定義增益和適度低失真的應用。輸入引腳也可以采用單端源驅動。峰值差分輸入為±2 V,允許1 V 均方根(rms)正弦波以寬裕的動態余量工作。輸出引腳基本上以軌到軌方式驅動單端負載。差分輸出電阻為150 ?。輸出擺幅是作用于VMAG引腳電壓的線性函數,該電壓的內部默認設置為0.5 V,提供±2 V峰值輸出。峰值輸出可以提高至10 V p-p,主要受電源電壓的限制。

數據表:*附件:AD8330低成本、DC至150MHz可變增益放大器技術手冊.pdf

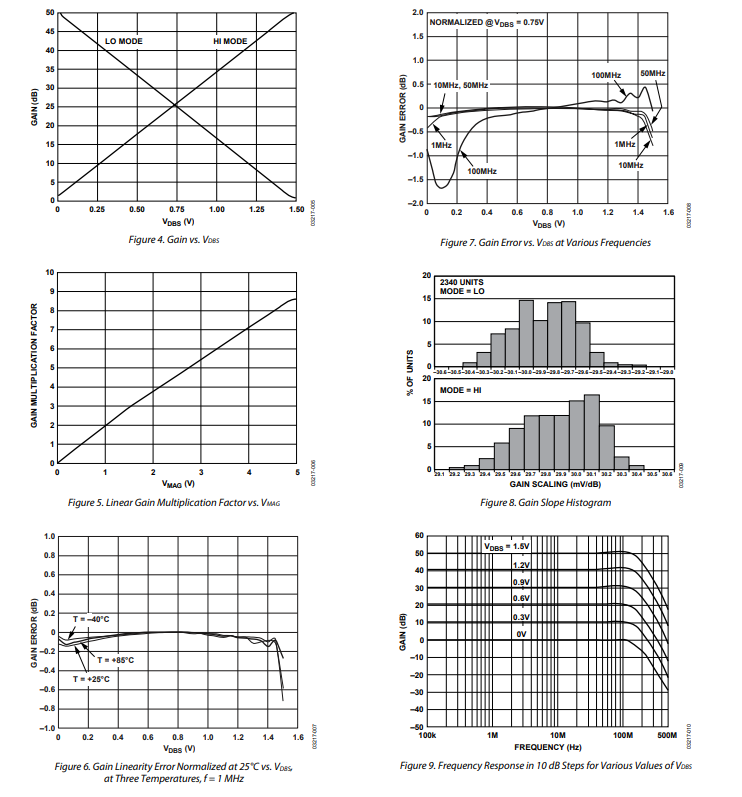

基本增益函數為線性dB,受引腳VDBS上所施加電壓的控制。增益范圍為0 dB至50 dB,相應控制電壓為0 V至1.5 V,因此斜率為30 mV/dB。增益線性度典型值在±0.1 dB以內。通過改變引腳MODE上的邏輯電平,增益可在相同范圍內減小,斜率相反。VMAG引腳上還提供第二增益控制端口,用戶可以利用它改變數字增益,變化系數為0.03至10。AD8330的參數對溫度和電源電壓的敏感度均較低。根據應用需要,可以使用VMAG重新定位0 dB至50 dB基本增益范圍,最高值可以提高20 dB(即20 dB至70 dB),最低值可以降低30 dB(即–30 dB至+20 dB),從而提供前所未有的100 dB增益范圍。AD8330的獨特之處在于,其帶寬和脈沖響應對增益基本上恒定,上述增益不僅包括50 dB基本線性dB范圍,而且包括用線性幅度函數所得到的范圍。在那些高頻時必須遵守精確的增益法則的VGA應用中,高頻響應在增益范圍內的出色穩定性顯得尤為重要。

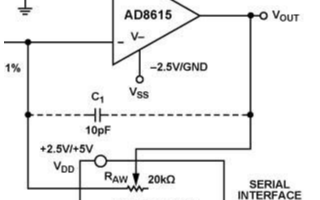

引腳OFST上的外部電容可設置失調降低環路的高通轉折頻率,它可以低至5 Hz。如果此引腳接地,信號通路就會去耦。用于驅動ADC時,可以將引腳CNTR上的外部共模控制電壓驅動至地電壓或VS的0.5 V范圍內,以滿足各種要求。兩個輸出默認定位在電源電壓的中點VS/2。這款多功能VGA還具有其它特性,如兩種省電模式(完全關斷和休眠模式)等,進一步增強了其實用價值。

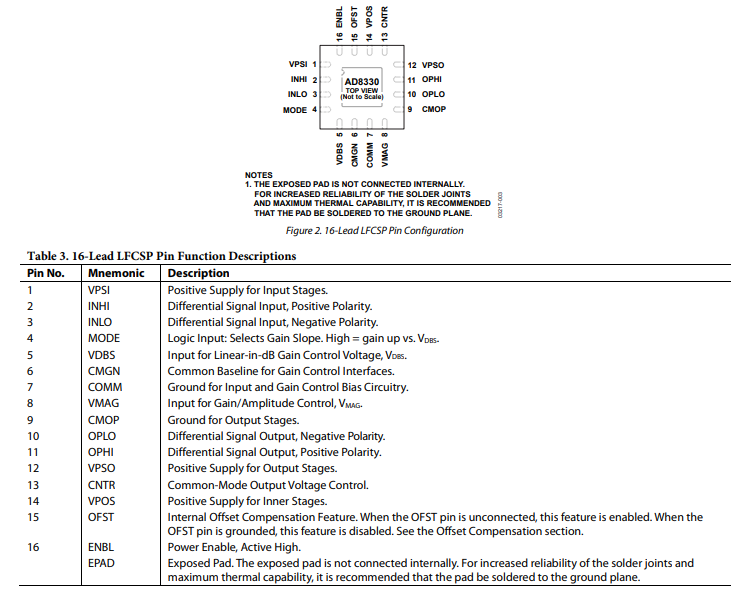

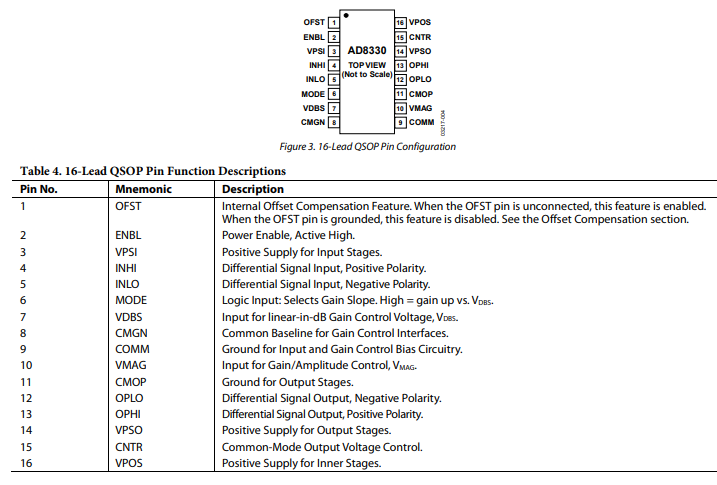

AD8330采用16引腳LFCSP和16引腳QSOP封裝,額定工作溫度范圍為?40°C至+85°C。

應用

- 前置ADC信號調理

- 75 Ω電纜驅動調整

- AGC放大器

特性

- 完全差分信號通路,也可使用單端信號

- 輸入范圍為0.3 mV至1 V均方根值,軌到軌輸出

- 差分輸入阻抗R

IN= 1 kΩ;輸出阻抗ROUT(每個輸出),75 Ω - 自動失調補償(可選)

- 線性dB和線性幅度增益模式

- 0 dB至50 dB,0 V < V

DBS< 1.5 V (30 mV/dB)

- 0 dB至50 dB,0 V < V

- 反向增益模式:50 dB至0 dB (-30 mV/dB)

- 標稱增益:x0.03至x10(15 mV< V

MAG< 5 V) - 恒定帶寬:150 MHz(全部增益)

- 低噪聲:5 nV/√Hz(典型值,最大增益時)

- 低失真:≤-62 dBc(典型值)

- 低功耗:20 mA(典型值,V

S= 2.7 V - 6 V) - 提供節省空間的3 mm x 3 mm LFCSP封裝

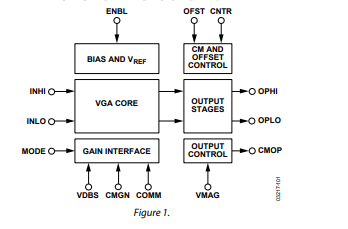

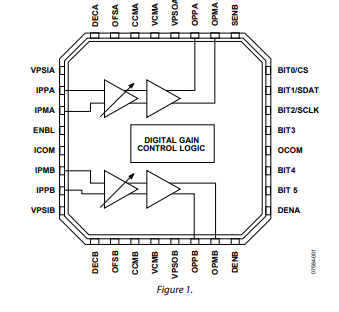

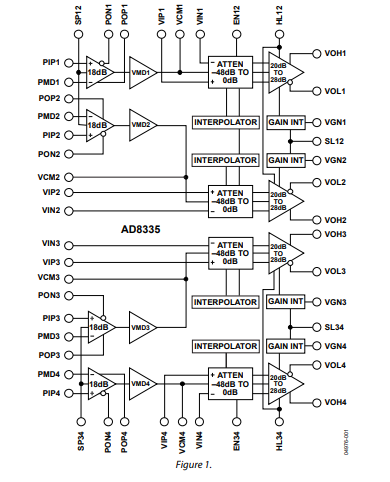

框圖

引腳配置描述

典型性能特征

電路描述

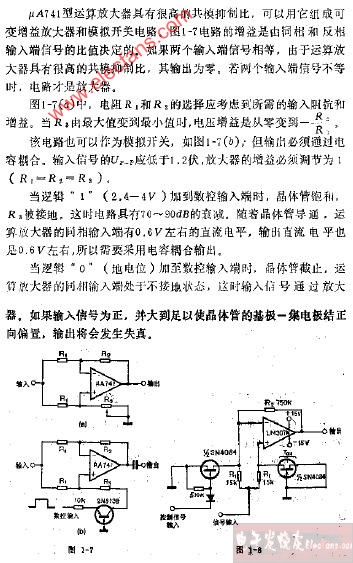

許多單片可變增益放大器采用的技術,大致可歸類為跨線性技術。這個術語指的是其功能直接依賴于雙極結型晶體管可預測特性的電路,尤其是其集電極電流與基極 - 發射極電壓之間的指數關系。20世紀70年代初,商用產品開發過程中廣泛應用跨線性原理,此后,精確寬帶模擬乘法器、除法器和可變增益放大器不斷涌現。

盡管這些技術已廣為人知,但要實現高性能可變增益放大器(VGA),在其設計中仍需特殊技術和對各個子電路的深入關注。AD8330采用了多項前沿技術,這些技術是在過去幾十年開發眾多領先信號處理產品的過程中逐步形成的,運用跨線性原理實現了前所未有的多功能性。

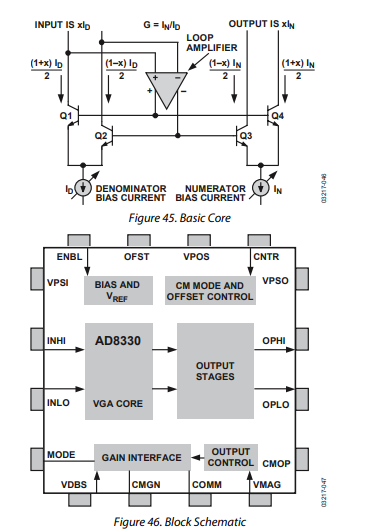

圖45展示了一個基本的代表性單元,僅由四個晶體管組成,或可看作一個非常緊密耦合的電路,這正是大多數跨線性乘法器、除法器和VGA的核心。其關鍵概念如下:首先,左側和右側的電流對在理想情況下相等,這是由于基爾霍夫電壓定律(KVL)。其次,跨導放大器將輸入信號A轉換為調制固定尾電流Io的可變電壓,Io在右側對進行復制,然后通過調制其標稱固定尾電流來生成輸出電流。在幾十年間,該電流的可變增益精確為G = Io/Io 。

實際上,這種電路全部潛力的實現,涉及許多其他因素,這些因素融合了這三個基本理念的變體。

通過對Io進行平方運算,可實現與雙象限模擬乘法器相關的功能,即輸出電流是輸入信號調制因子(k)和尾電流的函數。另一方面,通過除以Io,可實現雙象限模擬除法器的功能,即輸出電流與輸入信號成雙曲線增益函數關系。AD8330在兩種模式下均可運行。不過,由于雙曲線增益函數在大部分增益范圍內是一種擴展函數,因此在VGA中需要加入一個特殊接口,以便在Io上實現指數控制。

總體結構

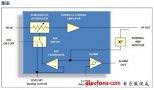

圖46展示了AD8330的框圖,標明了關鍵部分。關于其結構和特性的更詳細描述,請參閱“工作原理”部分;不過,圖46提供了其功能的總體概述。

VGA核心包含一個更復雜的指數控制單元,如圖45所示。該電流Io由通過VGA核心引腳VINDS和其本地連接引腳VINCM的電壓進行控制。增益范圍(即最大值與最小值之間的差值)由該增益控制輸入略大于50dB提供。絕對增益從輸入信號、源和負載阻抗的函數變化,并取決于第二增益控制引腳(VMAG)上的電壓,這在“正常工作條件”部分有解釋。

-

放大器

+關注

關注

145文章

14090瀏覽量

216149 -

增益放大器

+關注

關注

2文章

152瀏覽量

29446 -

函數

+關注

關注

3文章

4367瀏覽量

64113

發布評論請先 登錄

AD8330構造AGC的attack time能達到多少?

如何利用數字變阻器和運算放大器構建可變增益反相放大器?

MAX2092 700MHz至2700MHz頻率范圍可變增益放大器

AD8330 低成本、DC至150 MHz可變增益放大器

低成本可變增益反相放大器的電路設計與實現

AD8330低成本、DC至150MHz可變增益放大器技術手冊

AD8330低成本、DC至150MHz可變增益放大器技術手冊

評論