概述

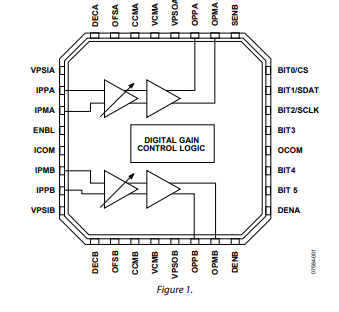

AD8372是一款雙通道、數字控制、可變增益放大器,能提供精密的增益控制、高IP3與低噪聲系數。出眾的低失真性能與寬信號帶寬使得AD8372非常適合多通道接收機應用。

數據表:*附件:AD8372 41dB增益范圍、1 dB步長、可編程雙通道VGA技術手冊.pdf

對于寬動態范圍應用而言,AD8372能提供41dB的寬增益范圍。其增益可以通過4引腳、雙向串行端口進行編程。每通道串行接口包括時鐘、閂鎖、數據輸入線和數據輸出線。

AD8372利用一個外部電阻提供設置輸出級跨導能力。RXT1與RXT2引腳通常通過一個2.0 kΩ的電阻接地,將最大增益額定值設置為31 dB。調整電流設置電阻,可以控制每個通道的增益和失真性能。這個靈活特性可用于功耗與失真性能折中的應用。

AD8372利用ENB1、ENB2引腳的適當邏輯電平供電。在省電模式下,AD8372待機電流不足2.6 mA,提供出色的輸入-輸出隔離。省電模式下保持增益設置。

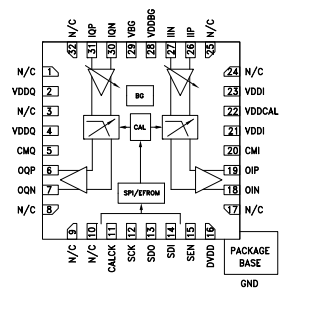

AD8372采用ADI公司的高頻BiCMOS工藝制作,具有精密增益控制調節能力和低失真性能。AD8372每通道的靜態電流通常為106 mA。AD8372放大器采用緊湊的、散熱增強型5 mm × 5 mm 32引腳LFCSP封裝,工作溫度范圍是:–40°C ~ +85°C 。

應用

特性

- 獨立的雙通道數字控制VGA

- 差分輸入和輸出

- 150 Ω差分輸入

- 開集差分輸出

- 7.8 dB噪聲指數至100 MHz(最大增益時)

- HD2/HD3優于77 dBc(1 V峰峰值差分輸出)

- ?3 dB帶寬:130 MHz

- 41 dB增益范圍

- 1 dB步長±0.2 dB

- 串行8位雙向SPI控制接口

- 寬輸入動態范圍

- 引腳可編程輸出級

- 關斷特性

- 5 V單電源:每通道106 mA

- 32引腳LFCSP、5 mm × 5 mm封裝

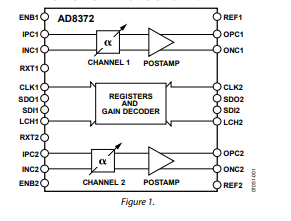

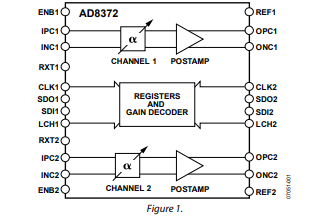

框圖

串行控制接口時序

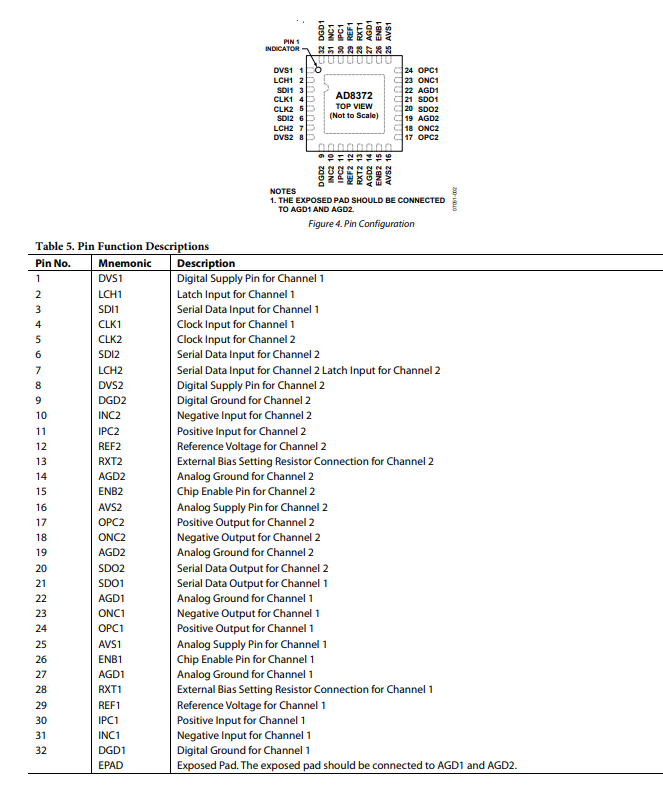

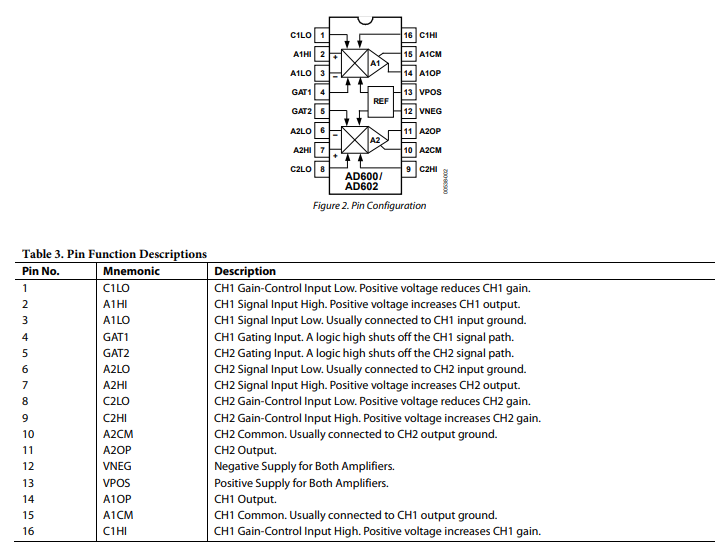

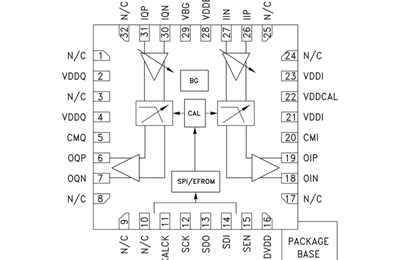

引腳配置描述

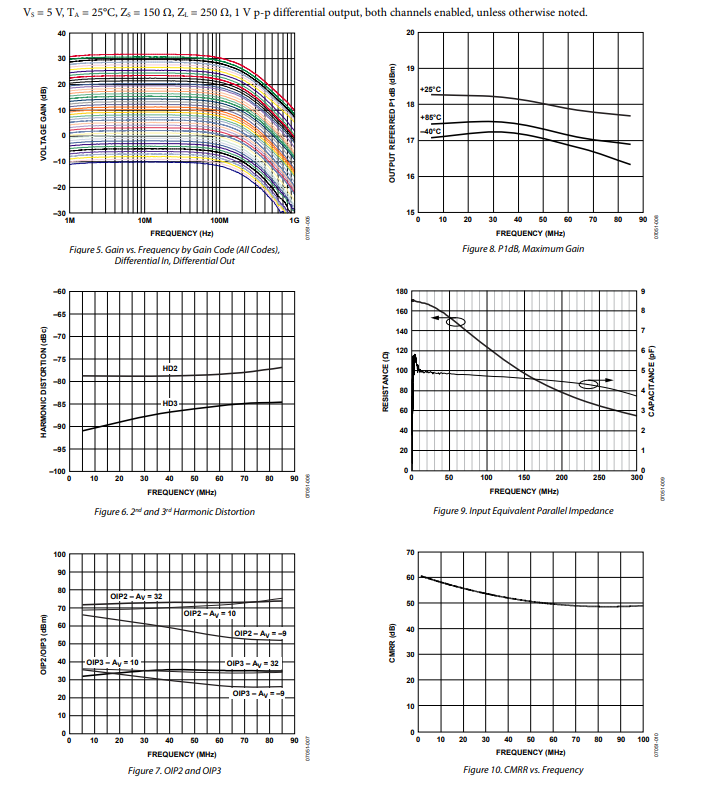

典型性能特征

AD8372是一款雙路差分可變增益放大器。每個放大器由一個150Ω的數字控制6dB衰減器、一個1dB微調器以及一個固定增益跨導放大器組成。

每個放大器的差分輸出由一對集電極開路輸出晶體管組成。其偏置電壓為+5V,采用高價值電感。33μH電感器(如Coilcraft 1812LS - 333XL )是該組件的理想選擇。應在差分輸出兩端連接一個250Ω的電阻,以提供電流 - 電壓轉換,并作為無源濾波的源阻抗,用于AD8372之后的電路。

AD8372的增益基于250Ω的差分負載,根據以下公式隨負載電阻變化:

- 電壓增益:Gain = RL(負載電阻)/250

- 功率增益:Gain = 10log(RL/250)

增益對負載的依賴性源于集電極開路輸出級,該級由外部電感偏置。電感的串聯扼流圈和電阻決定了放大器的低頻極點。高頻極點由寄生電容以及與輸出電阻并聯的電容決定。每側總輸出電流為106mA,其中組合輸出電流為70mA,電源引腳電流約為36mA。該電路有一個接地外部電阻(Rext),用于設置跨導級的輸出阻抗。為實現最佳失真效果,建議每側的Rext值為106mA。使Rext值約為2.0kΩ。每個輸出端的參考引腳使用2.4V參考電壓,并且在輸入端使用0.1μF電容對該共模電壓進行去耦。通過設置ENB引腳的電平可使器件功耗小于2.6mA。

AD8372的最大增益時噪聲系數為7.8dB,隨著增益降低而增加。噪聲系數的增加量等于增益的減小量。

在輸出端測量的增益線性度為一階,與測量的相位無關。

布局設計應考慮通過在扼流圈下方鋪設接地層來盡量減少輸出電容,并通過走線均衡來實現相位平衡。

單端和差分信號

AD8372設計用于施加差分信號作為輸入,并利用器件的差分輸出驅動來實現出色的信號失真性能。信號失真性能的改善主要歸因于使用差分信號技術來消除器件中的各種失真分量。此外,所有特性均采用差分信號路徑進行表征。若將該器件的輸入或輸出用作單端信號,會顯著降低AD8372的整體性能。

無源濾波技術

AD8372具有100Ω的差分輸入阻抗。為實現最佳性能,差分輸出負載應為250Ω。在設計AD8372的無源濾波器時,必須考慮這些阻抗。

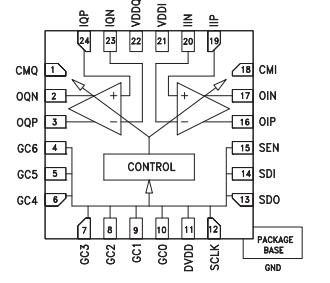

數字增益控制

數字增益控制接口由以下引腳組成:SDI、SDO、CLK和LATCH。當LATCH引腳為低電平時,該接口處于活動狀態。增益字從AD8372的SDI引腳寫入,并讀回到SDO引腳。寫入或讀取模式下的第一個時鐘輸入數據引腳決定接口是寫入模式還是讀取模式。該位是一個無關位,而其余六位對編程增益起作用。在讀取模式下,SDO引腳輸出6位增益字,從最低有效位(LSB)到最高有效位(MSB)。增益可在 - 9dB至32dB之間以1dB為步長進行編程。圖2和圖3給出了增益定時的詳細信息,表2給出了增益碼。

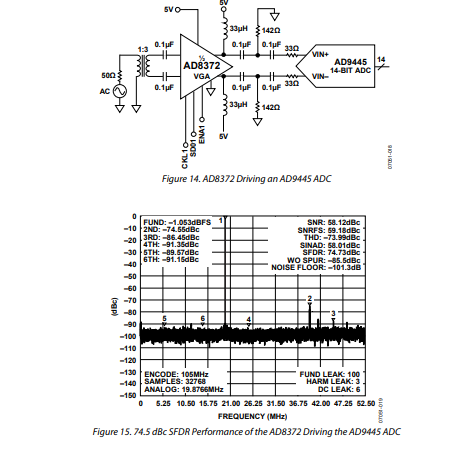

驅動模數轉換器

AD8372旨在驅動高速、高動態范圍的模數轉換器(ADC)。圖14所示的電路代表了AD8372雙路可變增益放大器(VGA)驅動AD9445 14位、125MSPS ADC的簡化端到端示意圖。AD8372的輸入進行交流耦合,使用1:3阻抗變壓器,該變壓器還將150Ω輸入電阻與50Ω源匹配。集電極開路輸出通過33μH電感器偏置,并與ADC的142Ω負載電阻交流耦合,在2kΩ輸入電阻處并聯,從而為增益精度提供250Ω負載。

ADC通過142Ω電阻進行交流耦合,以消除AD9445共模電壓的直流影響。在33Ω電阻上串聯連接可改善AD8372與ADC輸入采樣的隔離,并滿足AD9445對2kΩ差分負載和2V p-p信號(VREF = 1V時為滿量程輸出)的要求。該電路提供可變增益、隔離以及與AD9445的源匹配。使用此電路,在85MHz時,AD8372增益為32dB(最大增益)時,可實現74.5dBc的無雜散動態范圍(SFDR)性能(見圖15)。

-

放大器

+關注

關注

145文章

14100瀏覽量

216267 -

增益放大器

+關注

關注

2文章

152瀏覽量

29475

發布評論請先 登錄

通用雙通道數字控制可變增益放大器AD8372電子資料

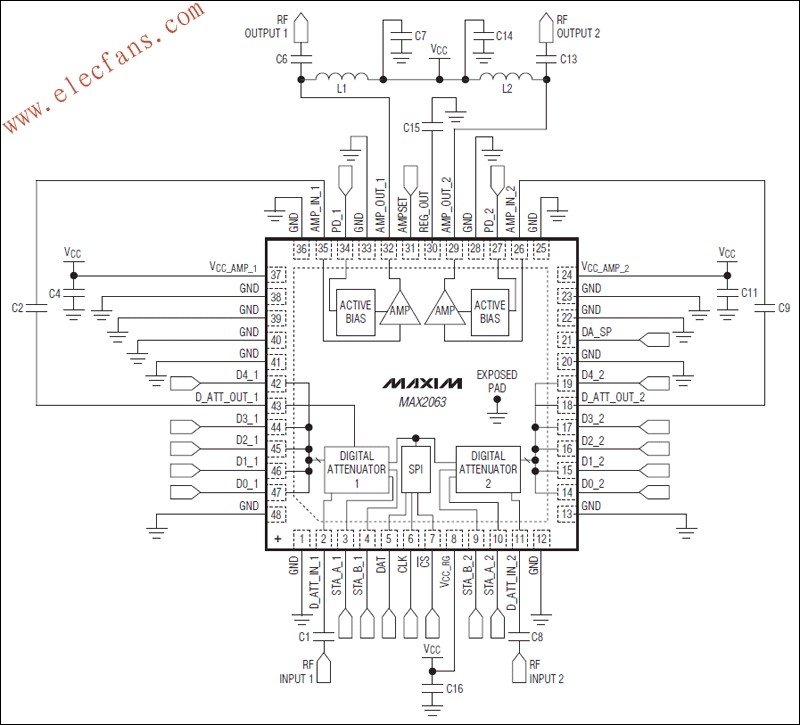

MAX2063雙通道數字調節可變增益放大器(VGA)

AD8372 41dB增益范圍、1 dB步長、可編程雙通道VGA

AD8372:41 db range,1 dB蒸發器,程序雙VGA數據Sheet

LTC5556 1.5GHz至7GHz雙路可編程增益下變頻混頻器技術手冊

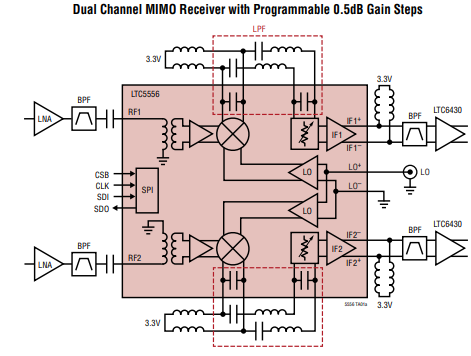

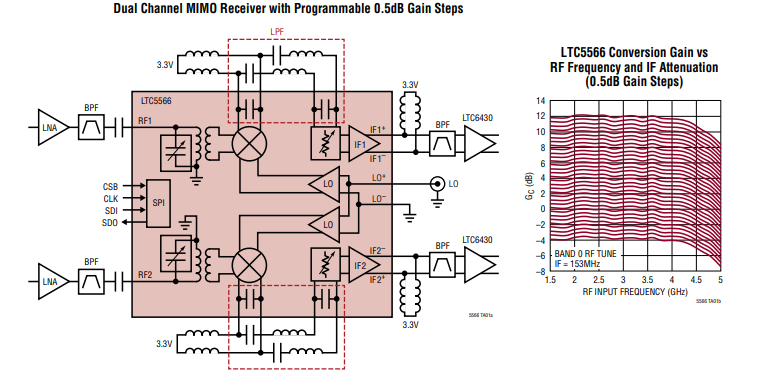

LTC5566 300MHz至6GHz雙通道可編程增益下變頻混頻器技術手冊

AD600/AD602雙通道、低噪聲、寬帶可變增益放大器(增益范圍0dB至+40dB)技術手冊

AD8372 41dB增益范圍、1 dB步長、可編程雙通道VGA技術手冊

AD8372 41dB增益范圍、1 dB步長、可編程雙通道VGA技術手冊

評論