在集成電路設(shè)計(jì)中,寄生參數(shù)是決定芯片性能的關(guān)鍵因素之一,尤其是在先進(jìn)工藝節(jié)點(diǎn)下,其影響愈發(fā)顯著,甚至可能成為影響芯片成敗的決定性因素。模擬設(shè)計(jì)的后仿真流程耗時(shí)且復(fù)雜,目前版圖寄生參數(shù)調(diào)試方法尚缺乏智能化支持。例如,設(shè)計(jì)人員往往需要投入大量時(shí)間進(jìn)行仿真,并通過人工Trace檢查關(guān)鍵路徑上的耦合電容。然而,對(duì)于包含數(shù)十GB寄生R/C參數(shù)的文件,人工檢查顯得力不從心。在檢查并修改版圖后,設(shè)計(jì)人員還需進(jìn)行寄生參數(shù)提取和后仿真。這一調(diào)試驗(yàn)證流程需要反復(fù)循環(huán),不僅對(duì)經(jīng)驗(yàn)有極高要求,而且后仿真環(huán)節(jié)耗時(shí)巨大,導(dǎo)致整體效率極低。那么,是否存在一個(gè)能夠滿足預(yù)期的寄生參數(shù)分析工具,并提供強(qiáng)大的Debug交互功能,以輔助進(jìn)行快速優(yōu)化和迭代IC設(shè)計(jì)呢?

1解決方案

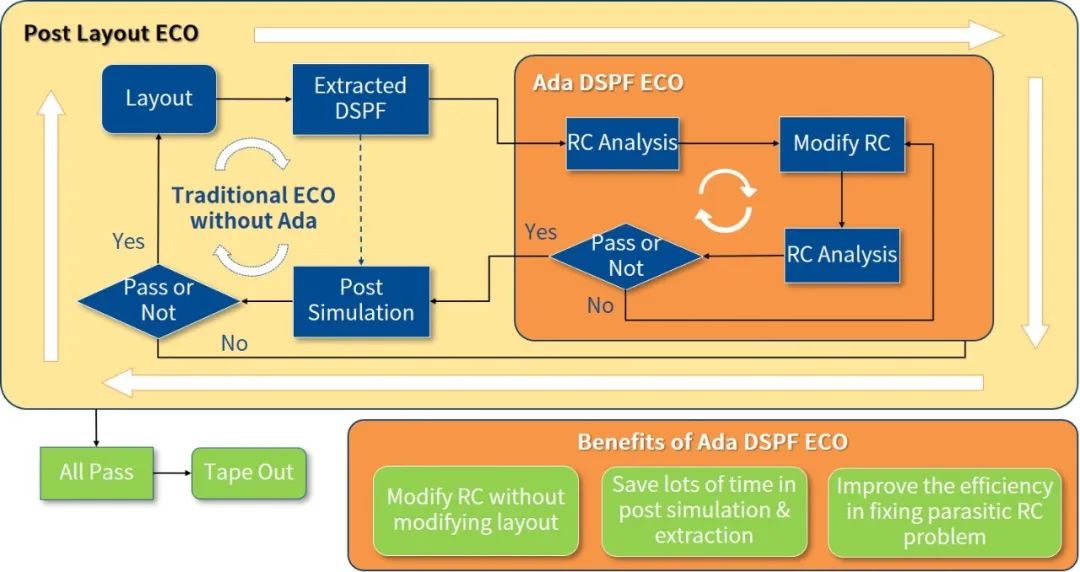

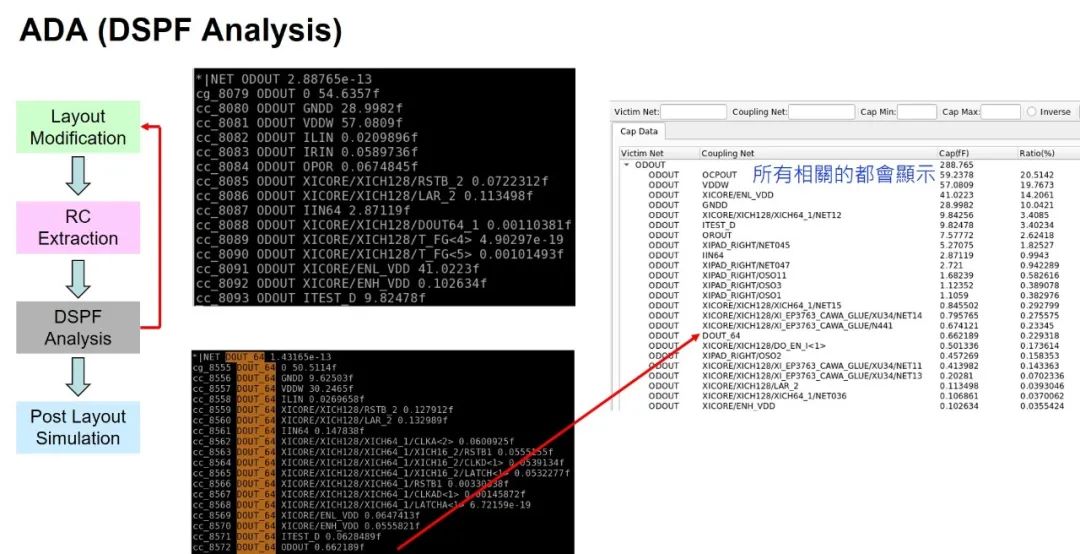

華大九天推出的版圖寄生參數(shù)分析工具Empyrean ADA(Analog Debug and Analysis,簡(jiǎn)稱“ADA”),徹底革新了調(diào)試流程。該工具無需反復(fù)修改版圖和進(jìn)行后仿真提取,結(jié)合寄生R/C分析功能,可以在進(jìn)行DSPF ECO動(dòng)作后直接檢查并確認(rèn)修改效果,然后導(dǎo)出DSPF(Detailed Standard Parasitic Format,詳細(xì)標(biāo)準(zhǔn)寄生格式)文件以供后仿使用。這一功能幫助設(shè)計(jì)師在無需迭代版圖的情況下迅速定位問題,顯著節(jié)省了后仿真以及修改版圖所需的時(shí)間,在確保設(shè)計(jì)正確性的前提下實(shí)現(xiàn)設(shè)計(jì)的快速收斂。 ADA為用戶提供完整寄生參數(shù)分析功能,包括寄生R/C分析、寄生R/C對(duì)比、分段統(tǒng)計(jì)耦合電容分析(Cross-talk)、原理圖(Schematic)設(shè)計(jì)的端到端電阻分析、版圖設(shè)計(jì)基于DSPF的點(diǎn)到點(diǎn)電阻分析等。此外,ADA還支持分析結(jié)果與原理圖和版圖View工具間的交互反標(biāo),方便用戶進(jìn)行Debug。

2創(chuàng)新的DSPF ECO流程

臺(tái)灣Ekepower公司在其時(shí)鐘生成電路設(shè)計(jì)流程中引入了ADA工具,顯著提升了設(shè)計(jì)效率與質(zhì)量。在時(shí)鐘信號(hào)產(chǎn)生電路中,電壓域分配以及各電壓域內(nèi)敏感信號(hào)與噪聲信號(hào)之間的耦合電容(Coupling Capacitance)對(duì)時(shí)鐘抖動(dòng)(Clock Jitter)的影響極為關(guān)鍵。因此,公司借助ADA工具深入分析敏感信號(hào)與噪聲信號(hào)之間的耦合情況,并將分析結(jié)果反饋至版圖設(shè)計(jì)階段,針對(duì)具體的走線進(jìn)行優(yōu)化調(diào)整,從而有效改善了時(shí)鐘抖動(dòng)問題。

相較于傳統(tǒng)的設(shè)計(jì)流程——即依據(jù)后仿真結(jié)果人工檢查寄生效應(yīng)對(duì)手動(dòng)修改版圖后再進(jìn)行后仿真,Ekepower公司的這一創(chuàng)新方法不僅大幅提高了設(shè)計(jì)效率,還顯著增強(qiáng)了設(shè)計(jì)的準(zhǔn)確性和可靠性。

3便捷的寄生R/C Compare分析

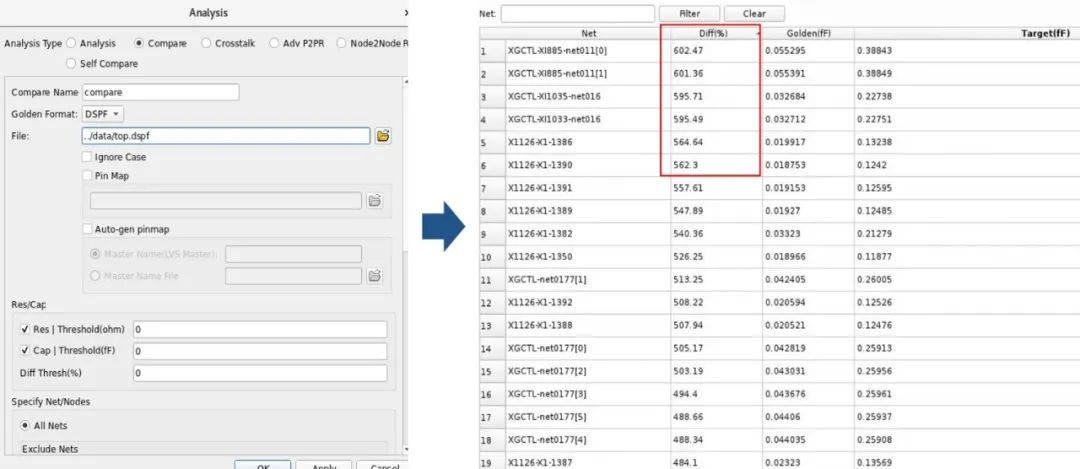

國(guó)內(nèi)一家平臺(tái)型芯片設(shè)計(jì)公司,近期在其SRAM設(shè)計(jì)團(tuán)隊(duì)中遇到了一個(gè)棘手的難題。在進(jìn)行后仿真時(shí),團(tuán)隊(duì)發(fā)現(xiàn)了一個(gè)異常現(xiàn)象:在使用相同電路和版圖設(shè)計(jì)的情況下,使用兩個(gè)不同版本的第三方工具中提取的DSPF文件進(jìn)行仿真后,結(jié)果出現(xiàn)了顯著差異。更令人困惑的是,尺寸較小的晶體管反而表現(xiàn)出更大的噪聲,這與常規(guī)的物理規(guī)律相悖。由于DSPF文件體積龐大,問題的定位變得異常困難。盡管團(tuán)隊(duì)與第三方工具的應(yīng)用工程師進(jìn)行了多次調(diào)試,但問題的根源仍然難以查明。

通過利用ADA工具的寄生R/C Compare分析功能,設(shè)計(jì)團(tuán)隊(duì)快速識(shí)別了兩個(gè)版本DSPF文件之間的寄生參數(shù)差異,并借助ADA的ECO功能,針對(duì)存在顯著差異的部分進(jìn)行了精準(zhǔn)修改,隨后進(jìn)行了后仿真驗(yàn)證。這一流程幫助團(tuán)隊(duì)追溯到了后仿真差異的根本原因,成功解決了長(zhǎng)期困擾客戶的后仿真問題。經(jīng)調(diào)查發(fā)現(xiàn),問題根源在于第三方寄生提取工具在版本更新時(shí)引入了一個(gè)Bug,這一結(jié)論已得到客戶以及第三方的共同確認(rèn)。

4先進(jìn)的P2P電阻評(píng)估

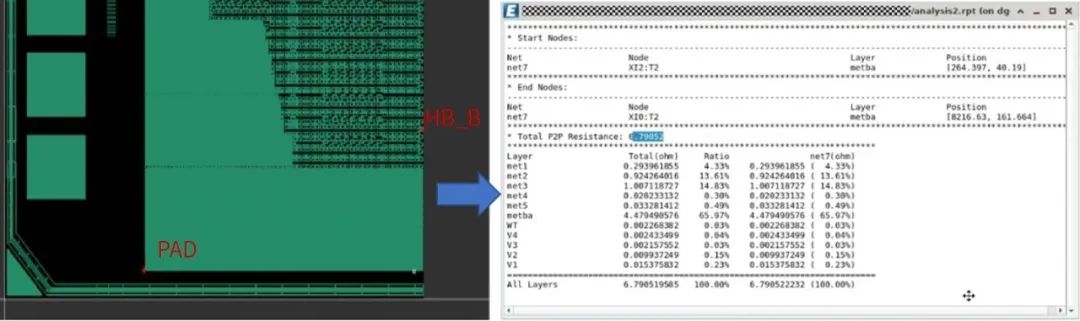

國(guó)內(nèi)一家頂尖芯片設(shè)計(jì)公司的后端工程師近期面臨一項(xiàng)關(guān)鍵任務(wù):評(píng)估頂層電源和地線金屬的電阻,為前端仿真提供精確數(shù)據(jù)。然而,現(xiàn)有的傳統(tǒng)EDA工具在電阻計(jì)算方面存在諸多局限性:計(jì)算結(jié)果不夠精確,且配置過程繁瑣復(fù)雜。若采用腳本計(jì)算方式,工程師需要根據(jù)項(xiàng)目需求手動(dòng)調(diào)整腳本,并借助Perc等工具進(jìn)行檢查,這一流程不僅耗時(shí)耗力,還極大地降低了整體工作效率。 為攻克這一難題,他們引入了ADA工具。借助該工具,工程師僅需在版圖上點(diǎn)選兩點(diǎn),并基于已提取的DSPF文件進(jìn)行P2PR(Point-to-Point Resistance,點(diǎn)到點(diǎn)電阻)分析,即可精準(zhǔn)定位用戶在版圖上點(diǎn)選位置對(duì)應(yīng)的節(jié)點(diǎn)(node),并提供精確的電阻值分析。此外,ADA工具還支持Port/Sub-node和Instance之間的集總電阻以及分層電阻展示,幫助用戶清晰查看各層金屬的電阻分布情況。這種高效、精準(zhǔn)的電阻評(píng)估方法,不僅顯著提升了工作效率,相比傳統(tǒng)方式效率提升數(shù)倍,還為前端仿真提供了更可靠的數(shù)據(jù)支持。

5高效多樣的篩選定位功能

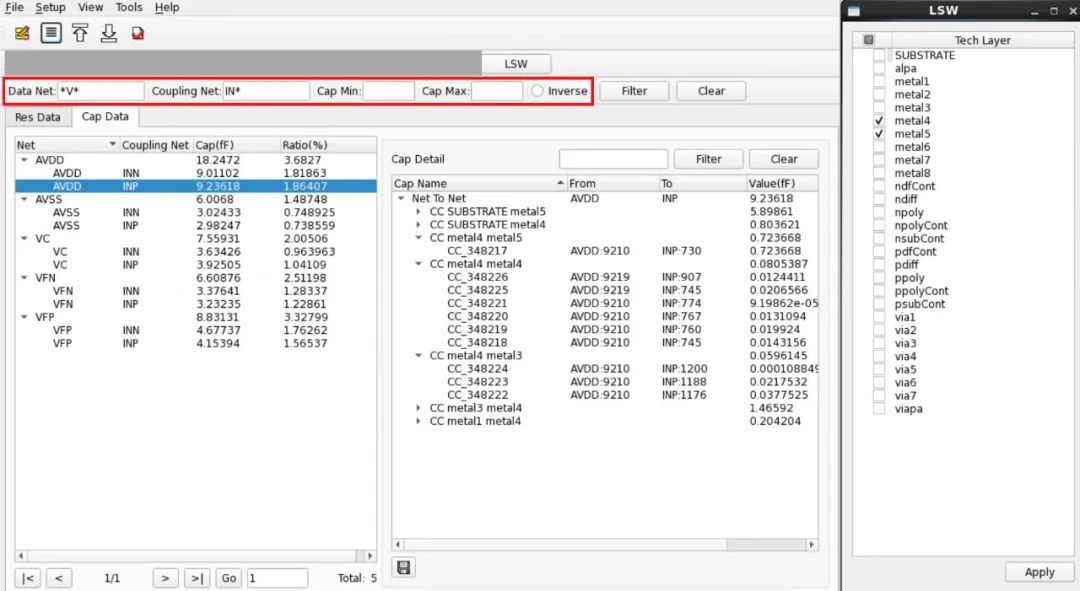

國(guó)內(nèi)一家頂尖芯片設(shè)計(jì)公司的前后端工程師近期遇到了一個(gè)棘手問題:在提取環(huán)節(jié)或修改版圖定位仿真問題時(shí),他們難以直觀地看到提取的問題以及修改后的效果。為解決這一難題,他們引入了ADA工具的LSW(Layer Selection Window,層次篩選)功能和結(jié)果過濾功能。通過這些功能,工程師可以高效地篩選出需要關(guān)注的層次,并剔除不應(yīng)被提取的layer,從而精準(zhǔn)地計(jì)算出P2PR點(diǎn)到點(diǎn)電阻的真實(shí)值。對(duì)于電容部分,ADA能夠快速定位用戶關(guān)注的較大走線金屬間的耦合電容,幫助工程師直觀評(píng)估如何優(yōu)化走線以降低耦合電容。這一改進(jìn)顯著提升了工程師在版圖優(yōu)化和仿真驗(yàn)證中的效率與準(zhǔn)確性。

6結(jié)語

華大九天推出的Empyrean ADA工具是一款專為模擬/模擬數(shù)字混合信號(hào)(AMS)設(shè)計(jì)的先進(jìn)版圖寄生參數(shù)分析工具。它能夠高效、精準(zhǔn)地分析模擬/混合信號(hào)設(shè)計(jì)中的寄生效應(yīng),助力模擬IC設(shè)計(jì)人員快速定位并解決由寄生R/C引起的各類問題。ADA工具與華大九天的模擬電路設(shè)計(jì)全流程EDA工具系統(tǒng)無縫集成,為模擬IC前端及后端設(shè)計(jì)人員提供了一個(gè)高效、優(yōu)質(zhì)且一站式的完整EDA解決方案,顯著提升了設(shè)計(jì)效率和質(zhì)量。

北京華大九天科技股份有限公司(簡(jiǎn)稱“華大九天”)成立于2009年,一直聚焦于EDA工具的開發(fā)、銷售及相關(guān)服務(wù)業(yè)務(wù),致力于成為全流程、全領(lǐng)域、全球領(lǐng)先的EDA提供商。

華大九天主要產(chǎn)品包括全定制設(shè)計(jì)平臺(tái)EDA工具系統(tǒng)、數(shù)字電路設(shè)計(jì)EDA工具、晶圓制造EDA工具和先進(jìn)封裝設(shè)計(jì)EDA工具等軟件及相關(guān)技術(shù)服務(wù)。其中,全定制設(shè)計(jì)平臺(tái)EDA工具系統(tǒng)包括模擬電路設(shè)計(jì)全流程EDA工具系統(tǒng)、存儲(chǔ)電路設(shè)計(jì)全流程EDA工具系統(tǒng)、射頻電路設(shè)計(jì)全流程EDA工具系統(tǒng)和平板顯示電路設(shè)計(jì)全流程EDA工具系統(tǒng);技術(shù)服務(wù)主要包括基礎(chǔ) IP、晶圓制造工程服務(wù)及其他相關(guān)服務(wù)。產(chǎn)品和服務(wù)主要應(yīng)用于集成電路設(shè)計(jì)、制造及封裝領(lǐng)域。

華大九天總部位于北京,在南京、成都、深圳、上海、香港、廣州、北京亦莊、西安和天津等地設(shè)有全資子公司,在武漢、廈門、蘇州等地設(shè)有分支機(jī)構(gòu)。

-

芯片

+關(guān)注

關(guān)注

459文章

52169瀏覽量

436098 -

集成電路

+關(guān)注

關(guān)注

5419文章

11947瀏覽量

367125 -

IC設(shè)計(jì)

+關(guān)注

關(guān)注

38文章

1346瀏覽量

105241 -

華大九天

+關(guān)注

關(guān)注

5文章

89瀏覽量

13248

原文標(biāo)題:Empyrean ADA:新一代版圖寄生參數(shù)分析工具

文章出處:【微信號(hào):華大九天,微信公眾號(hào):華大九天】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

華大九天Empyrean Polas工具解決功率設(shè)計(jì)難題

韋爾股份采用華大九天Empyrean Polas?保障芯片設(shè)計(jì)可靠性

華大九天版圖寄生參數(shù)分析工具Empyrean ADA介紹

華大九天版圖寄生參數(shù)分析工具Empyrean ADA介紹

評(píng)論