概述

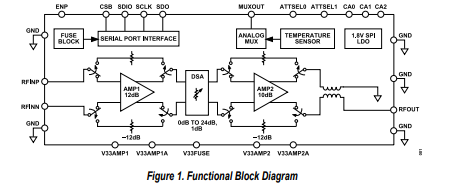

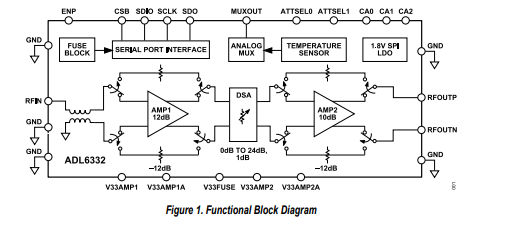

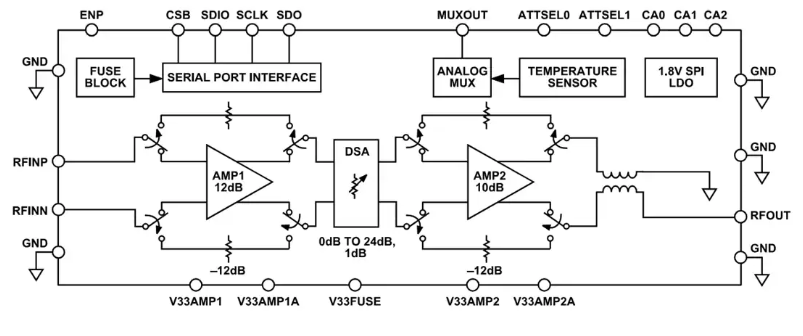

ADL6331 發射可變增益放大器(TxVGA)提供從 RF 數模轉換器(RF DAC)到單端功率放大器(PA)信號鏈的接口。每個 ADL6331 IC 均由一個平衡-不平衡轉換器、兩個帶旁路衰減器的差分 RF 放大器和一個數字步進衰減器(DSA)組成,以在 24 端子、4.0 mm x 4.0 mm LGA 封裝中提供合適的發射器性能。

串行端口接口(SPI)控制可用于配置 RF 信號路徑或優化電源電流與性能。

集成式 RF 巴倫用于提供 0.38 GHz 至 8.0 GHz(ADL6331-A)或 1.0 GHz 至 12.0 GHz(ADL6331-B)范圍內的單端輸出,且具有良好的阻抗匹配。

數據表:*附件:ADL6331 0.38GHz至12GHz TxVGA技術手冊.pdf

應用

特性

- 寬帶 TxVGA 將 RF-DAC 與波束合成和 PA 連接

- 工作頻率范圍:0.38 GHz 至 12 GHz,2 種產品型號

- ADL6331-A:0.38 GHz 至 8 GHz

- ADL6331-B:1.0 GHz 至 12 GHz

- 優化 RF-DAC 的共模抑制、偶次諧波和互調

- 50 Ω 差分輸入和 50 Ω 單端輸出

- 集成寬帶射頻輸出平衡器

- 增益控制范圍為 70 dB,步長為 1 dB

- RF DSA 范圍:24.0 dB,步長為 1.0 dB

- 每個放大器旁路損耗為 12 dB

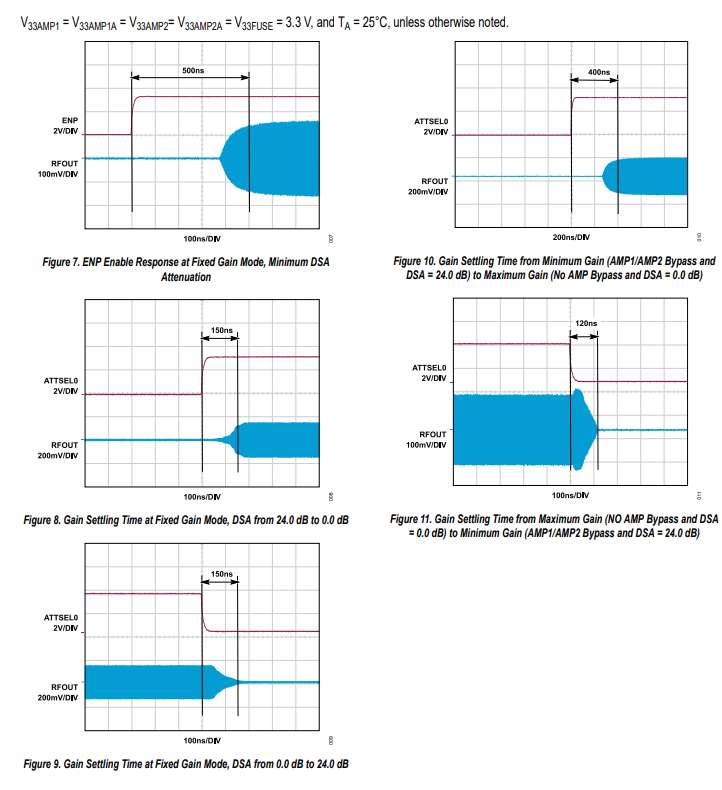

- 多個預定義衰減值和旁路放大器級之間的異步切換。

- 4 GHz 時的功率增益:15.1 dB (ADL6331-A), 15.4 dB (ADL6331-B)

- 4 GHz 時的噪聲指數:7.5 dB (ADL6331-A), 7.5 dB (ADL6331-B)

- 4GHz 時的 OIP3:31.0 dBm (ADL6331-A),31.0 dBm(ADL6331-B)

- 4GHz 時的 OIP2:58 dBm (ADL6331-A), 56 dBm (ADL6331-B)

- 4GHz 時的 OP1dB:12.4 dBm (ADL6331-A), 12.0 dBm (ADL6331-B)

- 通過 3/4 線 SPI 完全可編程

- 3.3 V(單電源)

- 24 引腳、4.0 mm x 4.0 mm LGA

邏輯圖

SPI時序圖

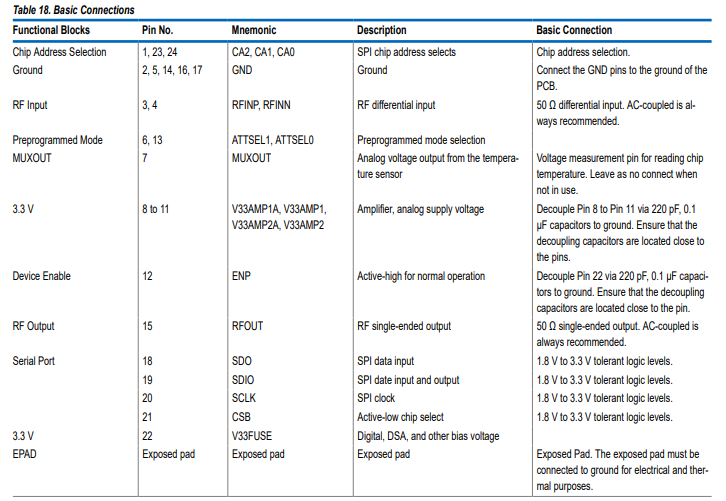

引腳配置描述

典型性能特征

串行端口接口(SPI)

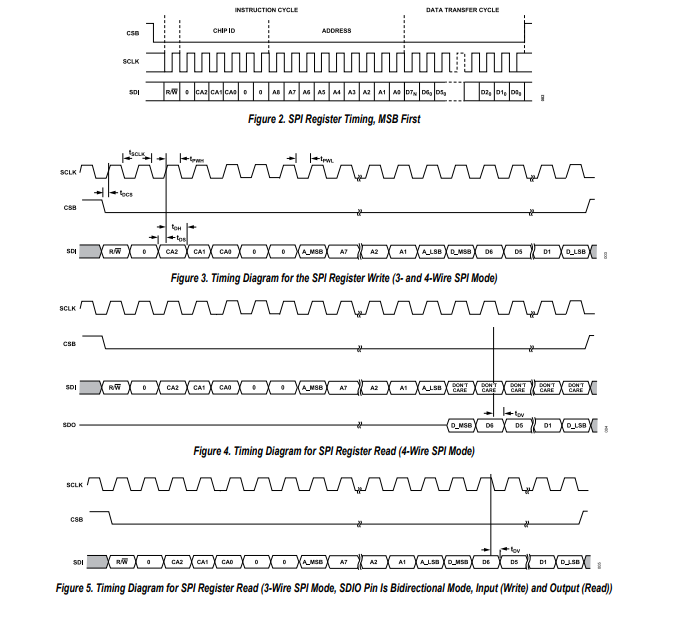

ADL6331的SPI允許用戶通過三線或四線SPI模式為特定功能或操作配置設備。該串行端口接口由四條控制線路組成:SCLK、SDIO、SDO和CSB。對于四線SPI模式,SCLK、SDIO和SDO被使用;三線SPI模式則是SPI模式的默認狀態。要啟用四線SPI模式,必須將SDOACTIVE[3]和SDOACTIVE[4]在寄存器0x000中設置為1。SPI中的定時要求列于表3中。

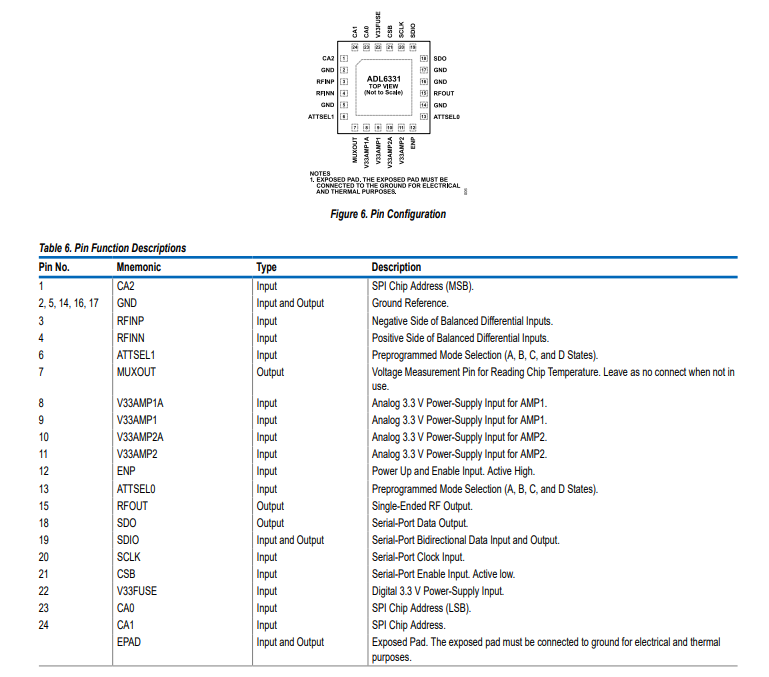

ADL6331協議由一個讀/寫操作、四個芯片地址位(最高有效位始終為0 )、九個寄存器地址位以及八個數據位組成。地址和數據字節均先傳輸最高有效位,最后傳輸最低有效位。為正確尋址設備,芯片地址前綴位必須與外部配置的芯片地址引腳CA2、CA1和CA0匹配。

ADL6331寫入SPI的輸入邏輯電平為1.8 V或3.3 V。在回讀周期中,通過設置SPI_3P3_CTRL位(寄存器0x121,位4 ),SDO可配置為1.8 V(默認 )或3.3 V回讀輸出電平。

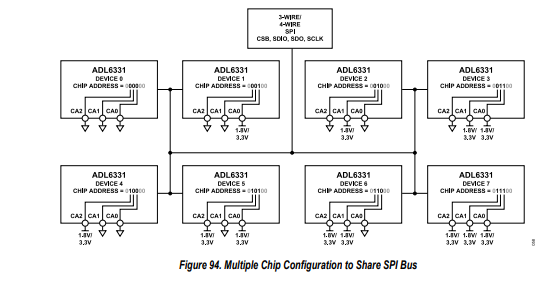

配置多個芯片共享SPI總線

最多可以使用同一條三線或四線SPI總線,通過單個CSB引腳尋址八個ADL6331設備。對于此功能,ADL6331的芯片選擇引腳(CA2、CA1和CA0 )用于標識帶有SPI寫芯片地址前綴的芯片(SPI接口端口如圖2所示 )。

ADL6331協議會忽略芯片地址最高有效位與芯片地址引腳設置不相等的地址寫入,只有當芯片地址前綴位的高四位與芯片地址引腳設置相等時,芯片才會接受地址。唯一的例外是軟件復位地址0x000。共享總線上的所有ADL6331芯片都會接受來自SPI主機控制器的0x000寄存器軟件復位。

圖94展示了如何配置芯片地址引腳CA2、CA1和CA0以及相關的芯片地址前綴位。

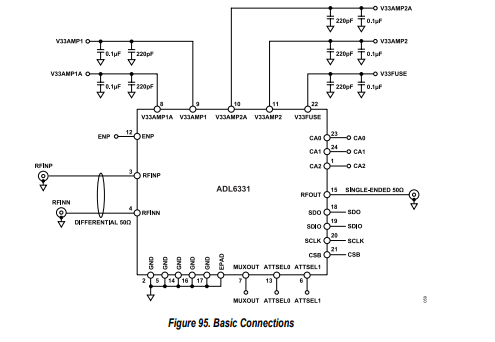

基本連接

應用信息

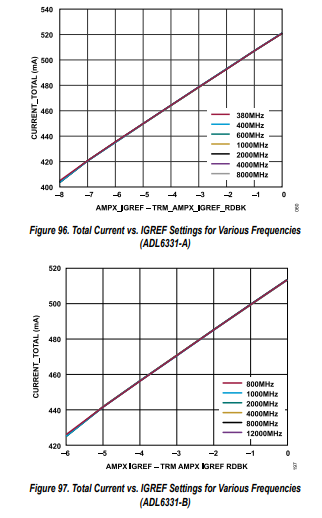

電流消耗優化

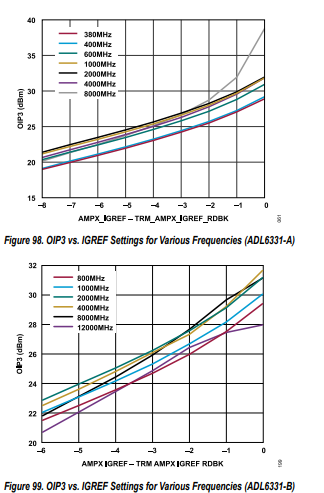

當寄存器0x104、寄存器0x105和寄存器0x106(適用于AMP1 )以及寄存器0x111、寄存器0x112和寄存器0x113(適用于AMP2 )中的最高有效位(MSB)都設置為0時,這六個寄存器可供用戶使用。如果需要降低電流消耗,可根據需要設置AMP1的IGREF(在寄存器0x104中 )和AMP2的IGREF(在寄存器0x111中 )。工廠調校的IGREF(分別在寄存器0x140和寄存器0x143中,適用于AMP1和AMP2 )可實現最佳的OIP3性能,如圖98和圖99所示。

不建議將IGREF設置增加到高于AMP1和AMP2的回讀值,這樣做可能會影響器件的長期可靠性。

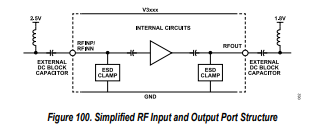

交流耦合

靜電放電(ESD)鉗位電路緊鄰輸入端口和輸出端口(見圖100 )。當施加的直流電壓大于或等于1.0 V(這是常見情況 )時,存在硅控制整流器(SCR)觸發的風險,即使是單個直流電壓尖峰也可能導致SCR觸發。帶有直流偏置的部件始終建議使用隔直電容進行交流耦合。

-

RF

+關注

關注

65文章

3171瀏覽量

168514 -

數模轉換器

+關注

關注

14文章

1054瀏覽量

83978 -

可變增益放大器

+關注

關注

1文章

40瀏覽量

45856

發布評論請先 登錄

LMX2595在8GH,12GHz, 24GHz都會產生雜散,為什么?

電源技巧#8:設計12GHz,超低相位噪聲(0.09 ps rms抖動)鎖相環

安捷倫1169A 12GHz探頭放大器套件特性參數

ADL6331:0.38千赫至12千赫TxVGA初步數據表 ADI

ADL6332:0.38千兆赫至12千兆赫RxVGA初步數據表 ADI

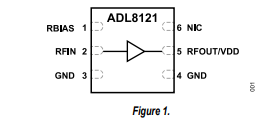

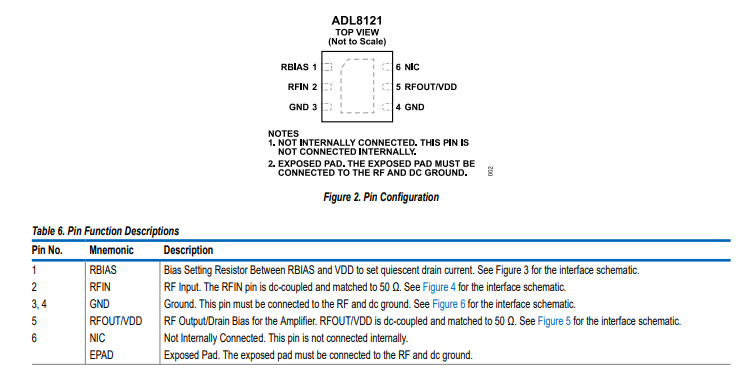

ADL8121 GaAs、pHEMT、MMIC、低噪聲放大器,0.025GHz至12GHz技術手冊

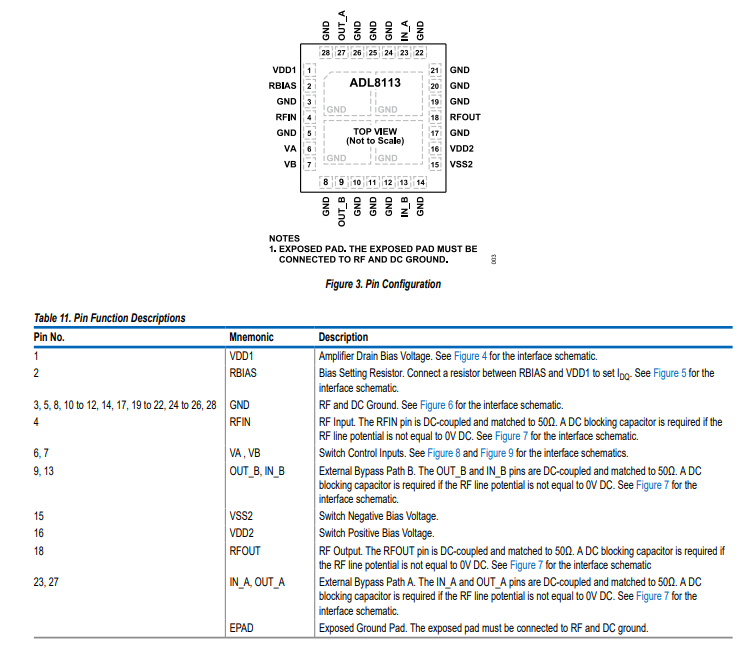

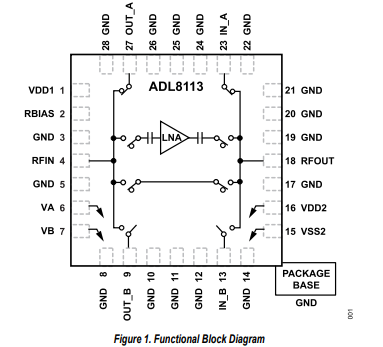

ADL8113 10MHz至12GHz低噪聲放大器,帶10MHz至14GHz旁路開關技術手冊

ADL6332 0.38GHz至15GHz RxVGA技術手冊

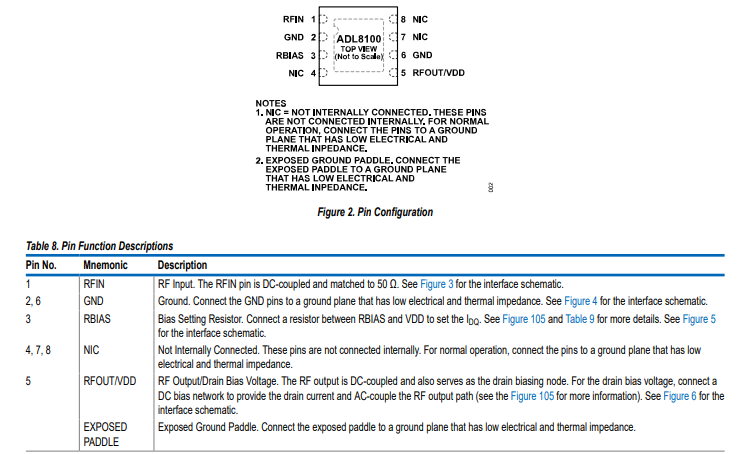

ADL8100 GaAs、pHEMT、MMIC、低噪聲放大器,0.01 GHz至20 GHz技術手冊

ADL8121 GaAs、pHEMT、MMIC、低噪聲放大器,0.025 GHz至12 GHz技術手冊

ADL8113 10MHz至12GHz低噪聲放大器,帶有10MHz至 14GHz旁路開關技術手冊

Analog Devices Inc. ADL6331發射可變增益放大器 (TxVGA)數據手冊

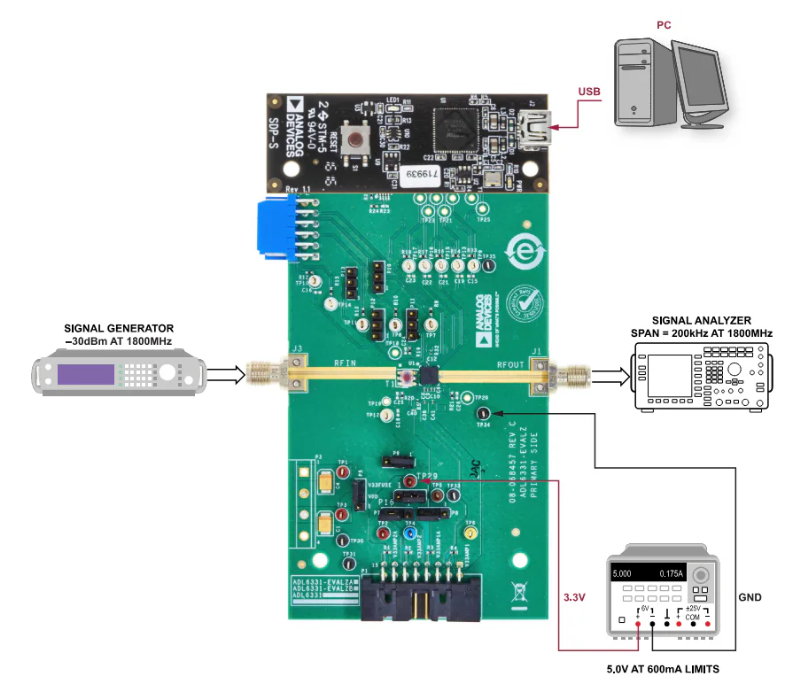

Analog Devices Inc. ADL6331-EVALZA 評估板數據手冊

ADL6331 0.38GHz至12GHz TxVGA技術手冊

ADL6331 0.38GHz至12GHz TxVGA技術手冊

評論