一、eMMC技術(shù)深度解析

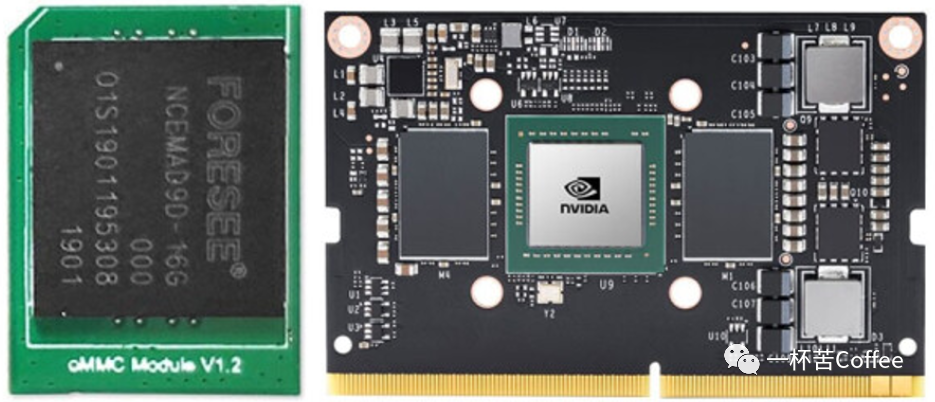

eMMC(Embedded Multi Media Card)是一種專為嵌入式系統(tǒng)量身打造的非易失性存儲(chǔ)解決方案。它巧妙地將NAND閃存、主控芯片以及接口協(xié)議集成于一個(gè)緊湊的BGA(Ball Grid Array)封裝之中。eMMC的設(shè)計(jì)初衷在于簡化系統(tǒng)設(shè)計(jì)流程,提升數(shù)據(jù)傳輸?shù)男剩档驮O(shè)備的功耗,同時(shí)滿足移動(dòng)設(shè)備對(duì)于存儲(chǔ)容量與性能日益增長的嚴(yán)苛要求。這一存儲(chǔ)標(biāo)準(zhǔn)由JEDEC(固態(tài)技術(shù)協(xié)會(huì))精心制定,其最新版本eMMC 5.1更是將傳輸速率推向了400MB/s的高速境界。憑借這些卓越特性,eMMC在智能手機(jī)、平板電腦、工控系統(tǒng)、電力儲(chǔ)能、車載系統(tǒng)以及物聯(lián)網(wǎng)設(shè)備等多個(gè)領(lǐng)域大放異彩,成為眾多設(shè)備制造商的首選存儲(chǔ)方案。

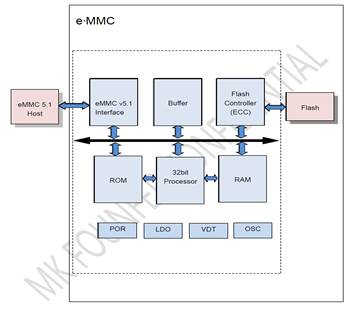

- 內(nèi)部架構(gòu)與工作原理

(1)核心組件

○NAND閃存陣列:存儲(chǔ)數(shù)據(jù)核心,采用pSLC/SLC/MLC/TLC等制程,提供不同容量與性能選擇。

○主控芯片:管理閃存讀寫、壞塊管理、磨損均衡(ECC糾錯(cuò)、GC垃圾回收)、協(xié)議轉(zhuǎn)換(將外部命令轉(zhuǎn)換為閃存操作指令)。

○接口邏輯:兼容MMC/SD協(xié)議,支持HS400、HS200等高速模式,通過并行數(shù)據(jù)線(DAT0~DAT7)實(shí)現(xiàn)數(shù)據(jù)并行傳輸。

(2)關(guān)鍵技術(shù)

○壞塊管理:出廠時(shí)通過掃描標(biāo)記不可用塊,運(yùn)行時(shí)動(dòng)態(tài)監(jiān)測(cè)新增壞塊并更新映射表,確保數(shù)據(jù)不寫入失效區(qū)域,通過映射表記錄壞塊位置,避免數(shù)據(jù)寫入失效區(qū)域,延長閃存壽命。

○磨損均衡算法:分為動(dòng)態(tài)均衡(如基于空閑塊選擇)和靜態(tài)均衡(如數(shù)據(jù)遷移),通過算法優(yōu)化延長閃存整體壽命避免特定區(qū)塊頻繁擦寫導(dǎo)致壽命提前耗盡。

○ECC糾錯(cuò)機(jī)制:采用BCH/LDPC算法,自動(dòng)糾正數(shù)據(jù)讀寫過程中的比特錯(cuò)誤。

○B(yǎng)CH:適用于SLC/MLC,糾錯(cuò)能力強(qiáng)但開銷高。

○LDPC:適用于TLC/QLC,糾錯(cuò)效率更高,支持更大容量糾錯(cuò)碼。

○數(shù)據(jù)讀寫流程:

1.主機(jī)發(fā)送讀寫命令至eMMC主控。

2.主控解析命令并執(zhí)行地址映射,將邏輯地址轉(zhuǎn)換為物理地址。

3.通過ECC生成校驗(yàn)碼,并寫入/讀取閃存數(shù)據(jù)。

4.返回?cái)?shù)據(jù)及狀態(tài)信息至主機(jī)。

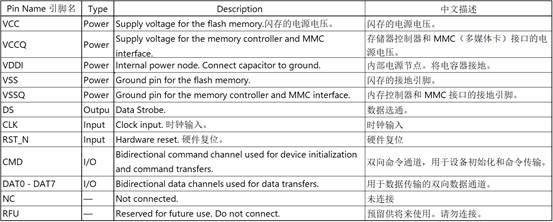

(3)通信協(xié)議-引腳介紹

eMMC采用基于命令/響應(yīng)的異步通信機(jī)制,通過以下信號(hào)線實(shí)現(xiàn)數(shù)據(jù)傳輸:

○CLK:時(shí)鐘信號(hào),決定數(shù)據(jù)傳輸速率(最高支持200MHz)。

○CMD:命令信號(hào)線,用于發(fā)送指令(如讀/寫、初始化、配置等)。

○DAT[0:7]:數(shù)據(jù)信號(hào)線,支持并行傳輸,提升帶寬。

○RST_N:復(fù)位信號(hào),低電平有效。

eMMC框圖

- eMMC版本演進(jìn)與性能對(duì)比

| 版本 | 發(fā)布年份 | 最大速率 | 關(guān)鍵特性 |

| eMMC 4.3 | 2009 | 52MB/s | 支持HS200模式,滿足早期移動(dòng)設(shè)備需求。 |

| eMMC 4.5 | 2011 | 200MB/s | 引入HS400高速模式,支持LPDDR接口。 |

| eMMC 5.0 | 2013 | 400MB/s | 增強(qiáng)功耗管理,支持硬件加密(eMMC Security)。 |

| eMMC 5.1 | 2016 | 400MB/s | 優(yōu)化隨機(jī)讀寫性能,提升溫度適應(yīng)性。 |

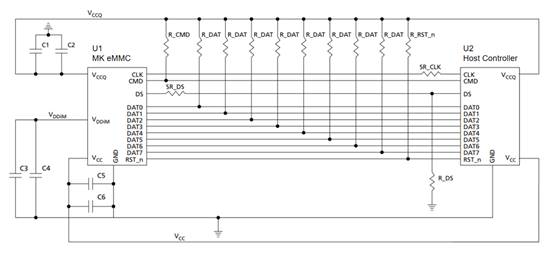

二、eMMC硬件電路設(shè)計(jì)詳解

(一)電路設(shè)計(jì)基礎(chǔ)

1.典型應(yīng)用電路

eMMC電路設(shè)計(jì)需關(guān)注電源、信號(hào)連接及保護(hù),以下為典型電路示意:

eMMC典型應(yīng)用電路示意圖,包含VCC、VCCQ、VDDi、CLK、CMD、D[0:7]、RST_N等信號(hào),標(biāo)注濾波電容、上拉電阻等。

2.電源設(shè)計(jì)

○VCC(供電電源):通常為3.3V或1.8V,需通過LC濾波電路(如10uF+0.1uF電容并聯(lián))抑制高頻噪聲。

○VCCQ(IO電源):與VCC相同或獨(dú)立,需確保電平匹配以避免邏輯沖突。

○VDDi(內(nèi)部核心電源):用于主控芯片供電,需單獨(dú)濾波(如2.2uF電容),并避免與IO電源共線。

3.信號(hào)線處理

○CLK信號(hào):需50Ω阻抗匹配,避免反射導(dǎo)致時(shí)序錯(cuò)誤。

○數(shù)據(jù)線(D0~D7):采用并行傳輸,需等長布線(誤差<50mil),并預(yù)留上拉電阻(10KΩ)以增強(qiáng)信號(hào)驅(qū)動(dòng)能力。

○CMD信號(hào):需上拉至VCCQ,確保空閑狀態(tài)為高電平。

(二)關(guān)鍵設(shè)計(jì)要素

1.濾波與去耦電容布局

○電源引腳附近放置多個(gè)不同容值電容(0.1uF~10uF),形成“金字塔”濾波結(jié)構(gòu),吸收不同頻段噪聲。

○VCC與VCCQ通過0Ω電阻隔離,確保電平一致性。

○電容盡量靠近芯片引腳,縮短走線長度,減少寄生電感。

○采用PMIC(電源管理芯片)為eMMC提供獨(dú)立3.3V供電,減少系統(tǒng)電源干擾。

2.PCB布線規(guī)則

○分層設(shè)計(jì):推薦使用4層及以上PCB,信號(hào)層與地層相鄰,降低信號(hào)輻射。

○信號(hào)隔離:eMMC信號(hào)與其他高速信號(hào)(如USB、射頻)保持間距(≥3W),數(shù)據(jù)線組間添加地線隔離,避免串?dāng)_。

○CLK走線:采用蛇形走線補(bǔ)償長度差異,確保與數(shù)據(jù)線同步到達(dá)。

○熱設(shè)計(jì)考慮:○eMMC芯片下方鋪銅散熱,通過過孔連接至地層,增強(qiáng)散熱效率。

○地平面分割:若存在多個(gè)電源域,需在分割區(qū)通過0Ω電阻或磁珠連接,確保信號(hào)回流路徑最短。

3.ESD與浪涌保護(hù)

○信號(hào)線可添加TVS二極管或ESD保護(hù)芯片,防止靜電或瞬態(tài)高壓損壞接口。

○RST_N信號(hào)線需串聯(lián)限流電阻(如1KΩ)并上拉,避免誤觸發(fā)復(fù)位。

三、eMMC性能優(yōu)化與調(diào)試

1.時(shí)序參數(shù)優(yōu)化

○CLK頻率與數(shù)據(jù)建立/保持時(shí)間:根據(jù)eMMC規(guī)格調(diào)整CLK頻率,確保數(shù)據(jù)在窗口期內(nèi)穩(wěn)定傳輸。

○信號(hào)延遲匹配:通過仿真工具(如HyperLynx)驗(yàn)證CLK與數(shù)據(jù)線延遲差,調(diào)整PCB布線長度。

2.功耗管理

○利用eMMC的Deep Power Down模式(DPD)降低待機(jī)功耗,通過軟件控制進(jìn)入/退出DPD狀態(tài)。

○動(dòng)態(tài)調(diào)整讀寫電壓(如1.8V→1.2V),平衡性能與功耗。

3.調(diào)試工具與測(cè)試方法

○使用示波器抓取CLK、數(shù)據(jù)波形,分析時(shí)序違規(guī)問題。

○通過壓力測(cè)試(如連續(xù)讀寫、高溫老化)驗(yàn)證eMMC可靠性。

-

單片機(jī)

+關(guān)注

關(guān)注

6063文章

44915瀏覽量

646879 -

電路設(shè)計(jì)

+關(guān)注

關(guān)注

6698文章

2518瀏覽量

211157 -

硬件電路設(shè)計(jì)

+關(guān)注

關(guān)注

4文章

33瀏覽量

21646 -

emmc

+關(guān)注

關(guān)注

7文章

228瀏覽量

53718

發(fā)布評(píng)論請(qǐng)先 登錄

怎么成為硬件電路設(shè)計(jì)高手?

硬件電路設(shè)計(jì)之eMMC電路設(shè)計(jì)

eMMC總線協(xié)議解析

PTR5415藍(lán)牙模組性能與場(chǎng)景應(yīng)用深度解析

硬件電路設(shè)計(jì)流程系列

功能安全---AUTOSAR架構(gòu)深度解析 精選資料分享

AUTOSAR架構(gòu)深度解析 精選資料分享

硬件電路設(shè)計(jì)的思路分享

C語言深度解析

硬件電路設(shè)計(jì)流程--原理圖設(shè)計(jì)

硬件電路設(shè)計(jì)的基本流程、作用和注意事項(xiàng)

CPM核心板應(yīng)用之eMMC硬件設(shè)計(jì)指導(dǎo)

硬件電路設(shè)計(jì):深度解析eMMC的性能與應(yīng)用

硬件電路設(shè)計(jì):深度解析eMMC的性能與應(yīng)用

評(píng)論