概述

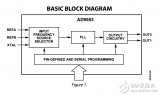

AD9553是一款基于鎖相環(huán)(PLL)的時鐘轉(zhuǎn)換器,針對無源光纖網(wǎng)絡(luò)(PON)和基站的需要而設(shè)計。該器件采用整數(shù)N分頻PLL來支持適用的頻率轉(zhuǎn)換要求。用戶通過REFA和REFB輸入提供最多兩路單端輸入?yún)⒖?a target="_blank">信號或一路差分輸入?yún)⒖夹盘枴T撈骷试S用戶將一個25 MHz晶振連接到XTAL輸入,因而支持保持應(yīng)用。

AD9553是引腳可編程器件,提供從15個可能的輸入頻率到51個可能的輸出頻率對(OUT1和OUT2)的標(biāo)準(zhǔn)輸入/輸出頻率轉(zhuǎn)換矩陣。該器件還有一個三線式SPI接口,用戶可以通過該接口自定義設(shè)置輸入與輸出頻率轉(zhuǎn)換。

雖然AD9553嚴(yán)格按照CMOS工藝制造,但其輸出與LVPECL、LVDS或單端CMOS邏輯電平兼容。

工作溫度范圍為?40°C至+85°C。

數(shù)據(jù)表:*附件:AD9553靈活的時鐘轉(zhuǎn)換器,適合GPON、基站、SONET SDH、T1 E1和以太網(wǎng)應(yīng)用技術(shù)手冊.pdf

應(yīng)用

- 高頻VCXO、OCXO和SAW諧振器的高性價比替代產(chǎn)品

- 極其靈活的頻率轉(zhuǎn)換,適合SONET/SDH、Gb以太網(wǎng)、光纖通道、DRFI/DOCSIS和PON/EPON/GPON

- 無線基礎(chǔ)設(shè)施

- 測試與測量(包括手持式設(shè)備)

特性

- 輸入頻率范圍:8 kHz至710 MHz

- 輸出頻率最高達(dá)810 MHz

- 預(yù)設(shè)的引腳可編程頻率轉(zhuǎn)換比支持常見的有線和無線頻率應(yīng)用,包括xDSL、T1/E1、BITS、SONET和以太網(wǎng)。

- 通過SPI端口設(shè)置任意頻率轉(zhuǎn)換比

- 片內(nèi)VCO

- 接受適合保持應(yīng)用的晶振輸入

- 兩路單端(或一路差分)參考輸入

- 兩路時鐘輸出(可獨立編程為LVDS、LVPECL或CMOS)

- 三線式SPI兼容型編程接口

- 3.3 V單電源

- 極低功耗:<450 mW(大部分條件下)

- 欲了解更多特性,請參考數(shù)據(jù)手冊

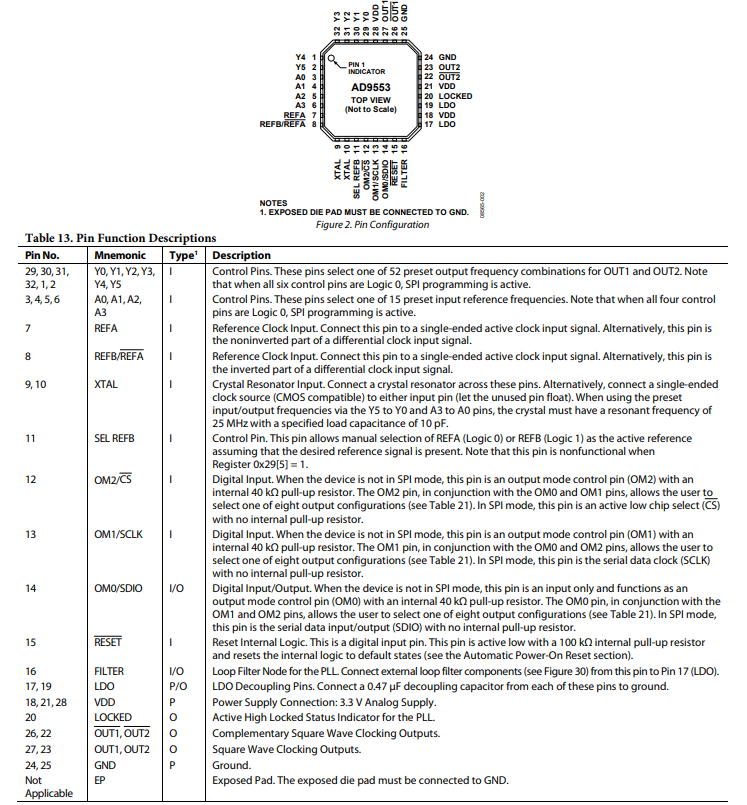

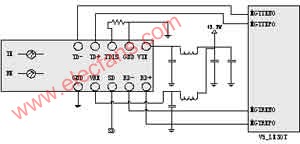

引腳配置描述

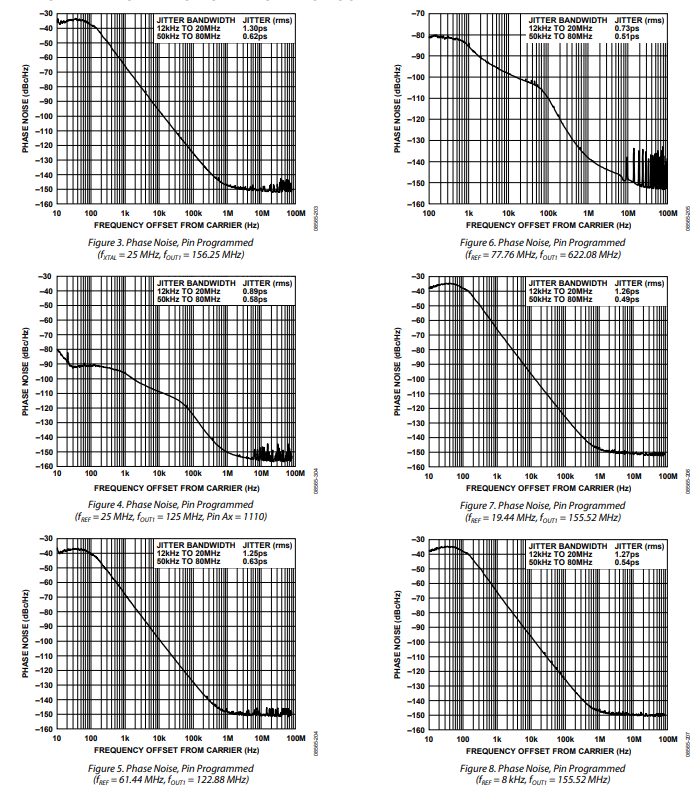

典型性能特征

操作理論

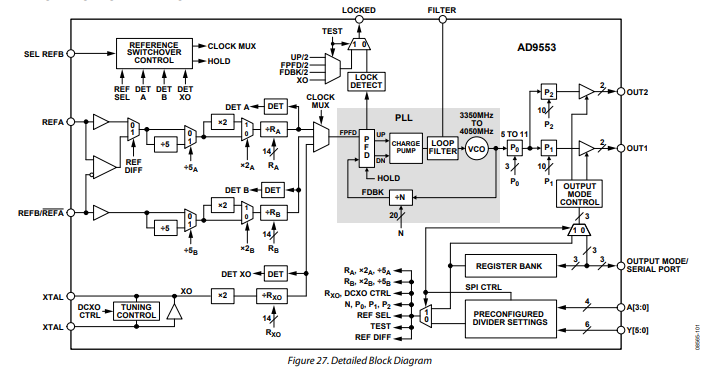

AD9553最多可接收兩個輸入?yún)⒖紩r鐘,即REFA和REFB。兩條輸入時鐘路徑均包含一個可選的5分頻(÷5)預(yù)分頻器和一個14位可編程除法器。此外,用戶可以將器件編程為通過單個時鐘(而非兩個單端輸入時鐘)以差分串行I/O模式運行。在差分操作模式下,REFB路徑為反向。

AD9553還設(shè)有一個專用的XTAL輸入,可直接連接一個可選的25MHz晶體諧振器。這為在輸入?yún)⒖夹盘柺r提供了備用時鐘信號。XTAL時鐘路徑包含一個固定的2倍頻乘法器和一個14位可編程除法器。

AD9553包括一個切換控制模塊,可在參考時鐘出現(xiàn)故障時自動處理從REFA到REFB(或反之)的切換。如果REFA和REFB均失效,該控制模塊會自動進(jìn)入保持模式,通過選擇XTAL時鐘信號(假設(shè)存在晶體諧振器連接到XTAL輸入)來維持時鐘輸出。

一般來說,出現(xiàn)在時鐘乘法器輸入處的時鐘信號(見圖27)以與PLL輸入相同的頻率運行(見圖27)。因此,PLL將時鐘乘法器選擇的信號轉(zhuǎn)換為頻率范圍在3.35GHz至4.05GHz之間的信號,具體取決于反饋分頻器(N)的值。VCO預(yù)分頻器(P_{o})將VCO輸出頻率按整數(shù)因子5至11進(jìn)行降低,從而得到305MHz至810MHz范圍內(nèi)的中間頻率。

10位的**P_{n}和P_{o}除法器可進(jìn)一步降低P_{o}**輸出頻率,以分別在OUT1和OUT2產(chǎn)生最終的輸出時鐘頻率。

因此,從參考輸入到輸出的頻率轉(zhuǎn)換比取決于÷5預(yù)分頻器的選擇;2倍頻乘法器;三個R除法器的值;N除法器;以及P_{n}、**P_{o}和P_{reconfig}**除法器的值。這些參數(shù)通過Ax和Yx引腳的預(yù)配置分頻器設(shè)置自動設(shè)定(見“預(yù)設(shè)頻率”部分)。或者,用戶可以通過串行I/O端口(見“串行控制端口”和“寄存器映射”部分)對這些寄存器進(jìn)行編程,使器件能夠適應(yīng)自定義的頻率轉(zhuǎn)換比。

預(yù)設(shè)頻率

頻率選擇引腳(A3至A0和Y5至Y0)允許用戶根據(jù)引腳邏輯狀態(tài)(見圖27),通過硬件設(shè)置器件的預(yù)設(shè)輸入和輸出頻率。引腳接地或連接到邏輯0或邏輯1,分別進(jìn)行解碼。

要訪問器件的默認(rèn)串行端口或SPI端口,用戶必須將Y5至Y0引腳設(shè)置為000000,將A3至A0引腳設(shè)置為0000。這樣會使引腳12至引腳14用作SPI端口控制引腳,而非輸出模式控制引腳(見“輸出驅(qū)動器模式控制”部分)。請注意,選擇SPI模式時,用戶必須將寄存器0x032的第0位寫為邏輯1,將寄存器0x030和寄存器0x034寫為邏輯0,以設(shè)置OUT1和OUT2模式控制位(見圖31和“輸出驅(qū)動器模式控制”部分)。

-

pll

+關(guān)注

關(guān)注

6文章

881瀏覽量

136041 -

時鐘轉(zhuǎn)換器

+關(guān)注

關(guān)注

0文章

9瀏覽量

5826 -

AD9553

+關(guān)注

關(guān)注

0文章

5瀏覽量

6400

發(fā)布評論請先 登錄

使用Si5315 8 kHz至644.53 MHz時鐘倍頻器的SI5315-EVB評估板

AD模數(shù)轉(zhuǎn)換器ADC0808CCV資料推薦

以太網(wǎng)到多路E1適配電路設(shè)計及FPGA實現(xiàn)

T1/E1 Frame Processor Agilent

DS33R11 以太網(wǎng)映射器,集成了T1/E1/J1收發(fā)器

DS33Z11—以太網(wǎng)LAN到非成幀T1/E1 WAN橋

什么是T1與E1線路

Xilinx FPGA設(shè)計的千兆以太網(wǎng)及E1信號的光纖傳輸方

基于FPGA的以太網(wǎng)與E1協(xié)議轉(zhuǎn)換器的實現(xiàn)

GPON基礎(chǔ)靈活的時鐘轉(zhuǎn)換器SDH和以太網(wǎng)ad9553數(shù)據(jù)表

AD9553 靈活的時鐘轉(zhuǎn)換器,適合GPON、基站、SONET/SDH、T1/E1和以太網(wǎng)應(yīng)用

AD9553:適用于GPON、基站、SONET/SDH、T1/E1和以太網(wǎng)數(shù)據(jù)表的靈活時鐘轉(zhuǎn)換器

T1和E1之間的轉(zhuǎn)換

AD9553靈活的時鐘轉(zhuǎn)換器,適合GPON、基站、SONET/SDH、T1/E1和以太網(wǎng)應(yīng)用技術(shù)手冊

AD9553靈活的時鐘轉(zhuǎn)換器,適合GPON、基站、SONET/SDH、T1/E1和以太網(wǎng)應(yīng)用技術(shù)手冊

評論