概述

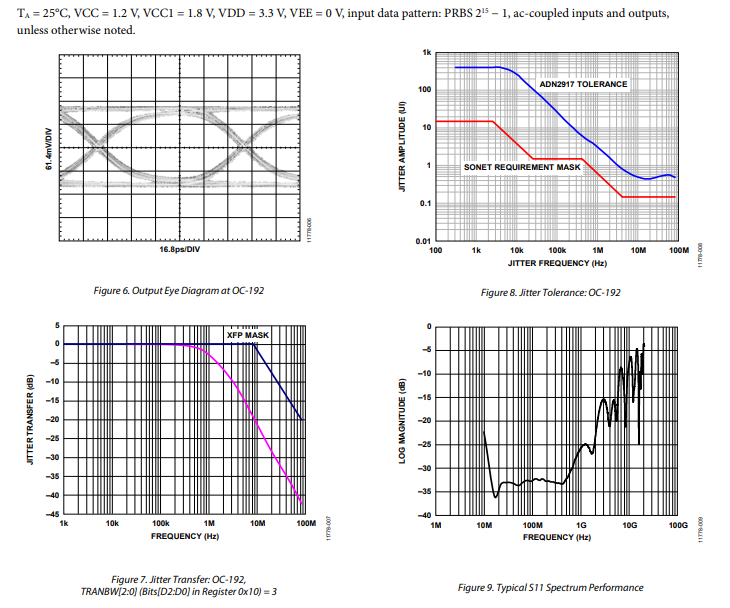

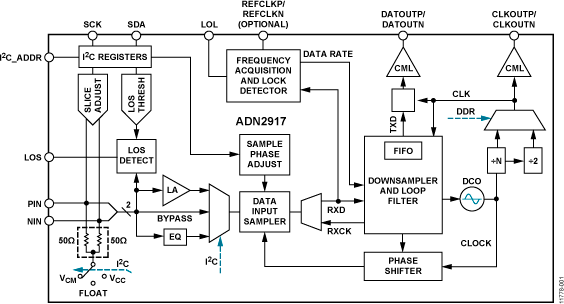

ADN2917可提供下列接收器功能:量化、信號電平檢測、時鐘和數據恢復,適用于從8.5 Gbps到11.3 Gbps的連續數據速率。它可自動鎖定至所有數據速率,而無需外部參考時鐘或編程。ADN2917抖動性能超越全部SONET/SDH抖動要求,包括抖動傳遞、抖動產生和抖動容差。

數據表:*附件:ADN2917連續速率8.5 Gbps至11.3 Gbps時鐘和數據恢復IC,集成限幅放大器 均衡器技術手冊.pdf

ADN2917提供手動或自動限幅調整和手動采樣相位調整。此外,用戶還可選擇在輸入端連接一個限幅放大器或均衡器。均衡器為自適應或可手動設置。

當輸入信號電平降至用戶可編程閾值以下時,接收器前端信號丟失(LOS)檢測電路會予以提示。LOS檢測電路具有遲滯特性,可防止LOS輸出震顫。此外,可通過I2C寄存器讀取輸入信號強度。

ADN2917還支持偽隨機二進制序列(PRBS)生成、位錯誤檢測和輸入數據速率回讀功能。

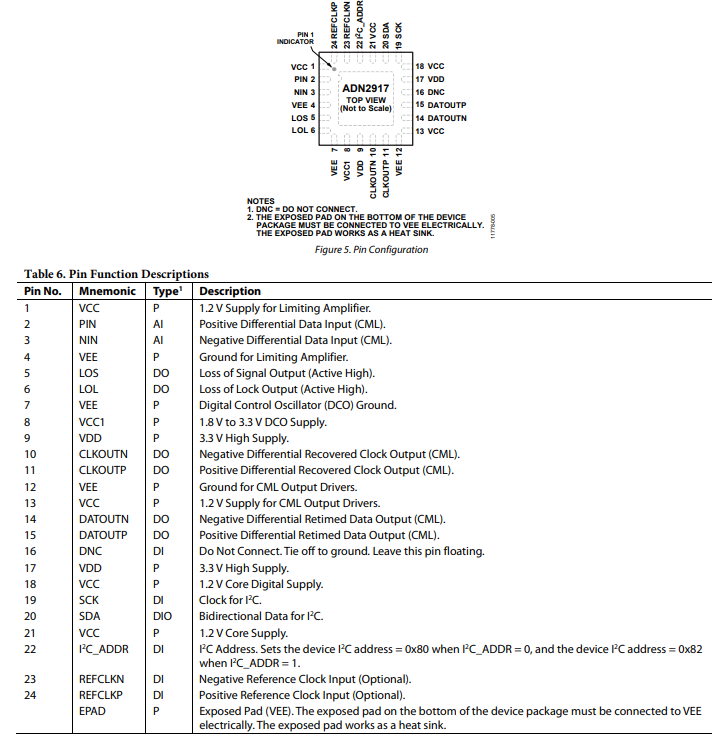

ADN2917采用緊湊型4 mm x 4 mm、24引腳架構芯片級(LFCSP)封裝。除非另有說明,否則所有規格均相對于?40 ℃至+85 ℃環境溫度而言。

應用

- SONET/SDH OC-192、10GFC、10GE及所有相關的FEC

- XFP、線路卡、時鐘、路由器、中繼器、儀器儀表

- 所有速率再生器/中繼器

特性 - 串行數據輸入:8.5 Gbps至11.3 Gbps

- 無需參考時鐘

- 超過SONET/SDH抖動傳遞/產生/容差要求

- 量化器靈敏度:9.2 mV p-p(典型值,限幅放大器模式)

- 可選限幅放大器和均衡器輸入

- 可編程抖動傳遞帶寬,支持G.8251 OTN

- 可編程限幅電平

- 采樣相位調整

- 輸出極性反轉

- 通過I2C可編程LOS閾值

- 通過I2C訪問可選特性

- LOS報警(僅限幅放大器模式)

- LOL指示器

- PRBS發生器/檢測器

- 應用敏感的功耗調整

- 352 mW(8.5 Gbps、均衡器模式、無時鐘輸出)

- 430 mW(11.3 Gbps、均衡器模式、無時鐘輸出)

- 電源:1.2 V、靈活的1.8 V至3.3 V范圍及3.3 V

- 4 mm × 4 mm、24引腳LFCSP封裝

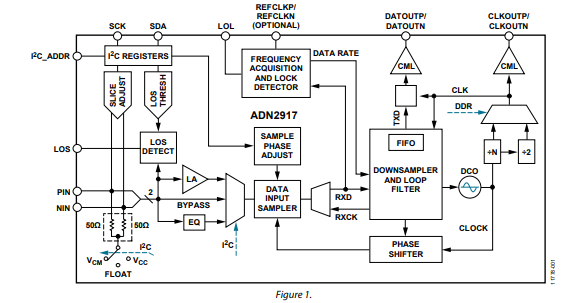

框圖

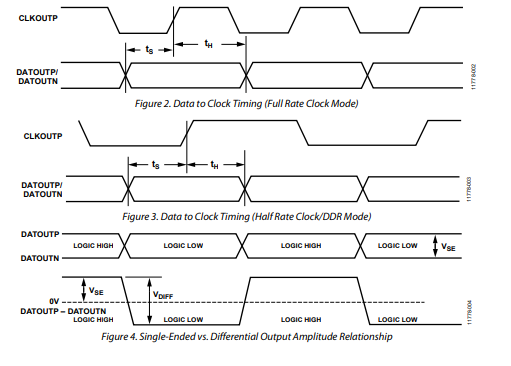

時序圖

引腳配置描述

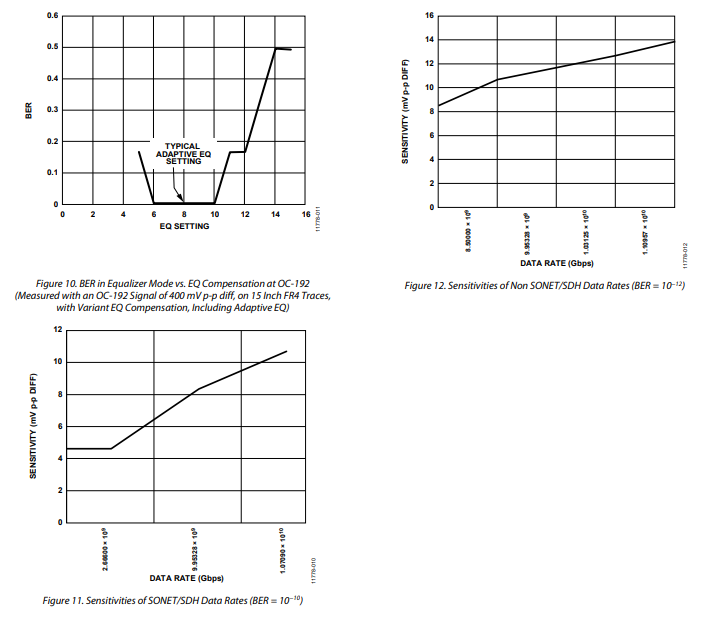

典型性能特征

ADN2917 實現了數據速率在 8.5 Gbps 至 11.3 Gbps 之間的時鐘和數據恢復功能。前端可進行配置,既能放大非歸零(NRZ)輸入波形以實現全比例數字邏輯電平,也能對其進行處理。

為處理高速輸入數據,用戶可選擇以下兩種方式:一是具有高達 10 dB 增益靈敏度的高增益限幅放大器;二是在 5 GHz 時提升高達 10 dB、靈敏度為 600 mV 的高通無源均衡器。

片上的信號丟失(LOS)檢測器與高靈敏度限幅放大器協同工作。LOS 的默認閾值為器件的靈敏度,最大閾值電平為 128 mV 峰峰值。限幅放大器還具備斜率閾值,可由用戶通過 I^{2}C 設置,或根據最佳眼圖張開度進行調整。

當輸入信號因 FR - 4 或印刷電路板(PCB)走線中的其他損傷而受損時,可使用無源均衡器。均衡器的高頻增益可通過 I^{2}C 寄存器進行配置,以替代出廠默認設置。此外,還具備用戶可啟用的自適應功能,該功能可自動調整以實現最寬的眼圖張開度。均衡器可針對 8.5 Gbps 至 11.3 Gbps 之間的任何數據速率進行手動設置。

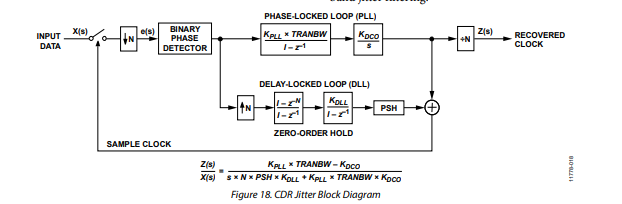

當有信號用于時鐘和數據恢復(CDR)時,ADN2917 采用延遲鎖定環和鎖相環(PLL)電路進行時鐘恢復和數據重定時,使其與來自 NRZ 編碼數據的數據流同步。輸入數據由高速時鐘采樣,數字下采樣器可適應跨越三個數量級的數據速率。下采樣數據被輸入到二進制鑒相器中。

輸入數據的相位由兩條獨立的反饋回路跟蹤。一條高速延遲鎖定環(DLL)路徑通過數字控制振蕩器(DCO)級聯一個數字積分器,以跟蹤抖動的高頻分量。另一條獨立的鎖相環,由數字積分器和 DCO 組成,用于跟蹤抖動的低頻分量。DCO 的初始頻率由第三環路設置,該環路將 DCO 頻率與輸入數據頻率進行比較。此第三環路還確定數字下采樣器的抽取率。

延遲鎖定環(DLL)和鎖相環(PLL)共同跟蹤輸入數據的相位。例如,當時鐘滯后于輸入數據時,鑒相器會將 DCO 驅動到更高頻率,并通過移相器將時鐘相位推進;這兩種操作都能減小時鐘與數據之間的相位誤差。由于環路濾波器是一個積分器,靜態相位誤差會被驅動至零。

從另一個角度來看,該電路中的移相器實現了頻率補償的二階鎖相環所需的零值,且零值位于反饋路徑中,因此在閉環傳遞函數中不會出現。由于該電路在閉環傳遞函數中沒有零值,所以消除了抖動峰值。

延遲鎖定環和鎖相環同時提供寬帶抖動適應和窄帶抖動濾波功能。圖 18 中的簡化框圖顯示,Z(s)/X(s) 是一個二階低通抖動傳遞函數,具有出色的濾波性能。低通頻率極點是通過在 DLL 中對 PLL 的增益進行分頻形成的,其增益在轉換帶寬內接近 N。請注意,該抖動傳遞函數沒有零點,與普通的二階鎖相環不同。這意味著主 PLL 沒有抖動峰值,這種無抖動峰值的特性為信號發生器應用提供了理想的性能,因為在級聯發生器中,抖動峰值可能會導致危險的抖動累積。

誤差傳遞函數 e(s)/X(s) 與帶有二進制鑒相器的普通鎖相環具有相同的高通形式,該傳遞函數可自由優化,以提供出色的寬帶抖動適應功能,因為抖動傳遞函數 Z(s)/X(s) 提供了窄帶抖動濾波功能。

-

均衡器

+關注

關注

9文章

223瀏覽量

30861 -

時鐘

+關注

關注

11文章

1883瀏覽量

132845 -

數據恢復

+關注

關注

10文章

637瀏覽量

18012

發布評論請先 登錄

請問ADN2917采樣信號量化應該怎樣使用

EVALZ-ADN2905/EVALZ-ADN2913/EVALZ-ADN2915/EVALZ-ADN2917用戶指南

ADN2917 連續速率8.5 Gbps 至11.3 Gbps 時鐘和數據恢復IC,集成限幅放大器/均衡器

ADN2917:連續速率8.5 Gbps 至11.3 Gbps 時鐘和數據恢復IC,集成限幅放大器/均衡器

ADN2812:連續速率12.3 Mb/s至2.7 Gb/s時鐘和數據恢復IC,帶集成限幅放大器數據表

ADN2814:連續速率10 Mb/s至675 Mb/s時鐘和數據恢復IC,帶集成限幅放大器數據表

ADN2813:連續速率10 Mb/s至1.25 Gb/s時鐘和數據恢復IC,帶集成限幅放大器數據表

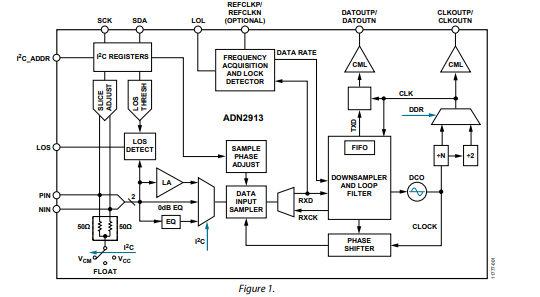

ADN2913:連續速率6.5 Mbps至8.5 Gbps時鐘和數據恢復IC,集成限幅放大器/均衡器數據表

ADN2817/ADN2818:連續速率10 Mbps至2.7 Gbps時鐘和數據恢復IC數據表

ADN2913連續速率6.5 Mbps至8.5 Gbps時鐘和數據恢復IC,集成限幅放大器/均衡器技術手冊

ADN2917連續速率8.5 Gbps至11.3 Gbps時鐘和數據恢復IC,集成限幅放大器/均衡器技術手冊

ADN2917連續速率8.5 Gbps至11.3 Gbps時鐘和數據恢復IC,集成限幅放大器/均衡器技術手冊

評論