概述

AD9578是一款可編程頻率合成器,可用于高性能電信、網(wǎng)絡(luò)、數(shù)據(jù)存儲、串行器/解串器(SERDES)和物理層(PHY)應(yīng)用中的抖動衰減和異步時鐘應(yīng)用。 該器件集成兩個能以超過0.1 ppb的精度提供任何頻率的抖動PLL,每一個均帶有兩個獨立的輸出驅(qū)動器,總共四路可編程輸出,提供極高的靈活性和抖動性能。 每路輸出均獨立可編程,提供高達919 MHz的頻率,且典型rms抖動值低于410 fs(12 kHz至20 MHz),采用緊湊型低成本基頻模式晶體(XTAL),具有穩(wěn)定的供應(yīng)鏈。 AD9578采用整數(shù)頻率合成,可實現(xiàn)低至290 fs的rms抖動。

數(shù)據(jù)表:*附件:AD9578雙通道PLL精密頻率合成器技術(shù)手.pdf

AD9578封裝采用出廠可編程默認上電配置。 上電后,包括輸出頻率在內(nèi)的全部設(shè)置均可通過快速SPI重新配置。

AD9578的架構(gòu)允許其用作數(shù)字控制振蕩器(NCO)。 因此,用戶可以使用快速SPI總線動態(tài)改變頻率。FPGA和其他器件可以利用此功能來實現(xiàn)具有可配置環(huán)路帶寬的數(shù)字PLL,用于抖動衰減應(yīng)用、鎖定至緊湊型穩(wěn)定基準(zhǔn)電壓源的精密可馴時鐘或數(shù)控精密時序應(yīng)用,比如網(wǎng)絡(luò)時序和IEEE 1588應(yīng)用等。 SPI總線工作頻率高達50 MHz,實現(xiàn)快速FPGA環(huán)路的同時讓多器件共享同一個總線。AD9578還可用于多速率精密應(yīng)用中,比如視頻廣播或OTN。 ADI公司提供用于數(shù)字PLL應(yīng)用的HDL FPGA代碼。

應(yīng)用

- 基于FPGA的抖動衰減和低抖動PLL

- 精密可馴時鐘和時鐘頻率合成器

- 多速率時鐘頻率合成器

- 光學(xué): OTN/SDH/SONET

- 視頻廣播: 3G SDI、HD SDI、SDI

- 網(wǎng)絡(luò)與存儲: 以太網(wǎng)/SAS/光纖通道

- 無線基礎(chǔ)設(shè)施: OBSAI/CPRI

- 工業(yè): IEEE 1588

- 數(shù)控振蕩器(NCO)

特性

- 任意輸出頻率的精密頻率合成

- 11.8 MHz至 919 MHz

- 頻率分辨率超過0.1 ppb

- 超低rms抖動(12 kHz至20 MHz)

- 使用整數(shù)頻率合成:<300 fs rms

- 使用小數(shù)頻率合成:<405 fs rms

- 雙基準(zhǔn)電壓輸入支持LVPECL、LVDS、1.8 V LVCMOS、基頻模式AT切割晶體(22 MHz至54 MHz)或基準(zhǔn)電壓源時鐘(20 MHz至60 MHz)

- 數(shù)字(NCO)頻率控制l

- 動態(tài)可牽引輸出頻率實現(xiàn)基于FPGA的PLL(提供HDL)

- 快速串行外設(shè)接口(SPI)總線寫入速度高達100 MHz

- 可即時更改頻率

- 集成雙PLL,采用7 mm × 7 mm緊湊型封裝

- 可代替多個大型時鐘IC、PLL、扇出緩沖器、晶體振蕩器(XO)和壓控晶體振蕩器(VCXO)

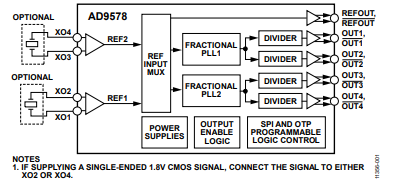

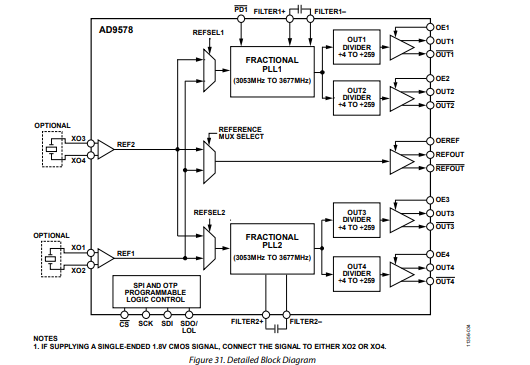

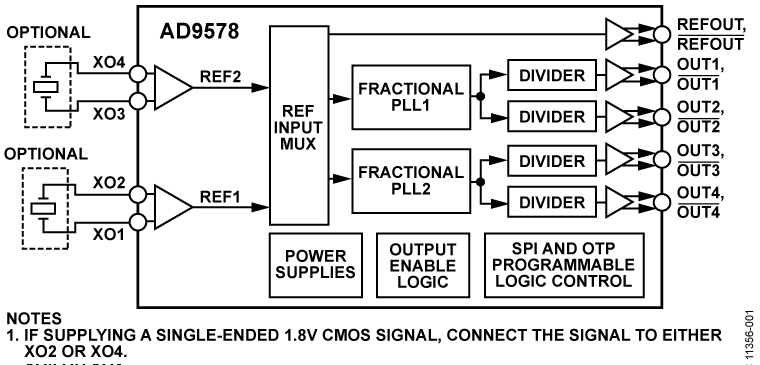

簡化功能框圖

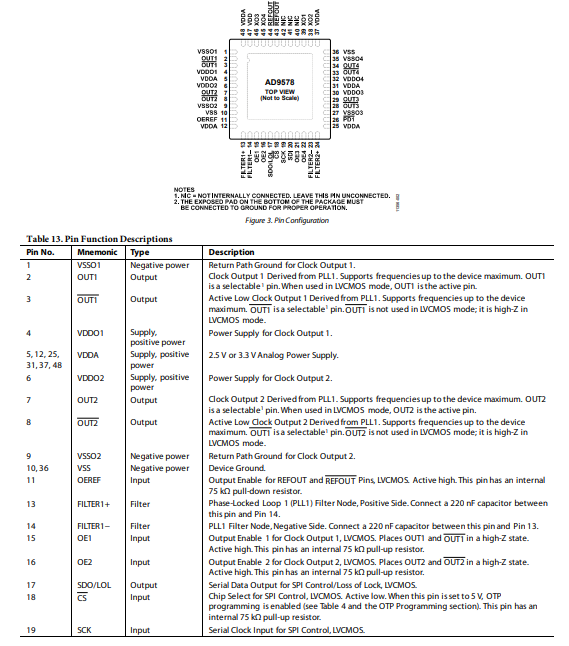

引腳配置描述

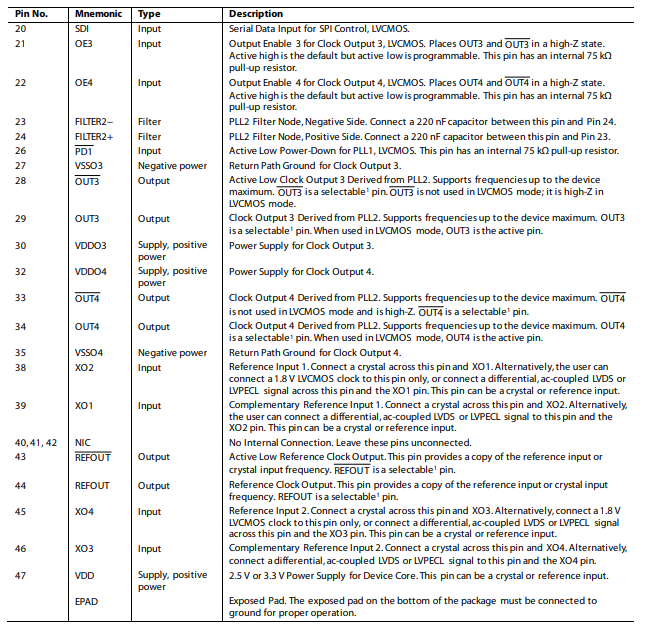

典型性能特征

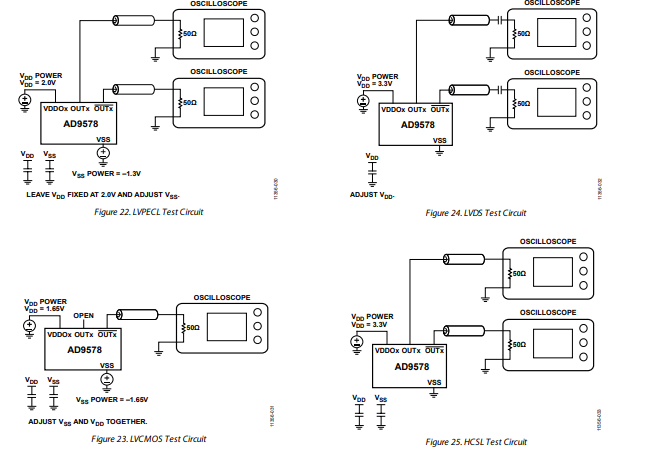

測試設(shè)置和配置電路

操作理論

AD9578 是一款雙合成器,具備四個可編程輸出。兩個鎖相環(huán)(PLL),可采用晶體或外部參考輸入頻率,能產(chǎn)生多達四種獨特的輸出頻率。每個輸出上的輸出格式標(biāo)準(zhǔn)包括低壓互補金屬氧化物半導(dǎo)體(LVCMOS)、低壓差分信號(LVDS)、低壓正射極耦合邏輯(LVPECL)和高速電流模式邏輯(HCSL)。晶體輸入具有低功耗休眠模式,并且 AD9578 提供可編程增益和負載電容。此外,可將內(nèi)部基準(zhǔn)時鐘用作任一或兩個鎖相環(huán)的參考時鐘。晶體或外部參考頻率可按需選用。

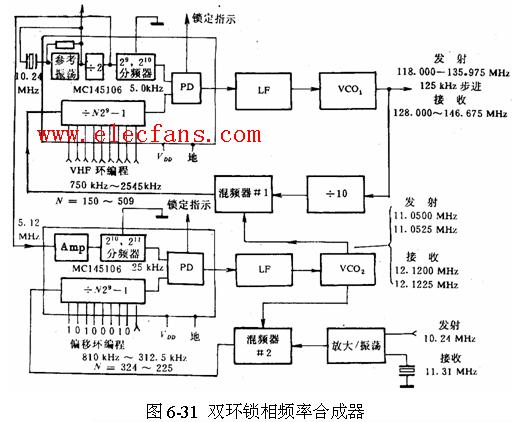

鎖相環(huán)獨立運行,但可共享輸入?yún)⒖迹ㄈ粜枰4嬖谌N操作模式可供選擇:整數(shù)模式、分數(shù)模式和比率模式。整數(shù)模式能提供最低噪聲,并具備類似傳統(tǒng)整數(shù)鎖相環(huán)的整體數(shù)字分頻器。分數(shù)模式采用 8 位整數(shù)部分和 28 位小數(shù)部分,從而實現(xiàn)基于 0.1 ppm 或更佳的頻率分辨率的頻率合成。旋轉(zhuǎn)波振蕩器(RTWO)可在 3053 MHz 至 3677 MHz 的速率下運行,以實現(xiàn)分數(shù)模式,同時允許用戶指定反饋分頻器的比率(以一個整數(shù)除以另一個整數(shù)的形式表示)。每個壓控振蕩器(VCO)上有兩個輸出,頻率范圍為 750.8 MHz 至 259.2 MHz,還包含 4.5 模式下的頻率間隔。任何輸出頻率通過 11.8 MHz 和 919 MHz 的分頻可產(chǎn)生頻率誤差為 0.1 ppb 或更佳的頻率。

該器件具備額外特性,包括低相位噪聲、小頻率步進下輸出頻率的平滑變化,以及通過串行外設(shè)接口(SPI)進行控制。AD9578 可通過 SPI 進行配置,也可通過 SPI 命令進行組合編程,用戶可對其進行全面控制。AD9578 具備默認功率配置,可在開機時自動編程。所有設(shè)置均可在加電后通過 SPI 重新編程。

典型情況下,鎖相環(huán)帶寬設(shè)置為 300 kHz,鎖相環(huán)跟蹤并將參考相位噪聲乘以晶體輸入提供的多個低相位噪聲參考,從而在輸出相位噪聲接近載波時實現(xiàn)低相位噪聲。選擇參考時,確保參考輸入的相位噪聲足夠低,以滿足系統(tǒng)噪聲要求。

-

合成器

+關(guān)注

關(guān)注

0文章

280瀏覽量

26140 -

頻率合成器

+關(guān)注

關(guān)注

5文章

294瀏覽量

32712 -

pll

+關(guān)注

關(guān)注

6文章

881瀏覽量

136041

發(fā)布評論請先 登錄

基于DDS的頻率合成器設(shè)計介紹

如何利用FPGA設(shè)計PLL頻率合成器?

DDS PLL短波頻率合成器設(shè)計

AD9578 雙通道PLL精密頻率合成器

ADF4206/ADF4208:雙射頻PLL頻率合成器數(shù)據(jù)表

pll頻率合成器工作原理與pll頻率合成器的原理圖解釋

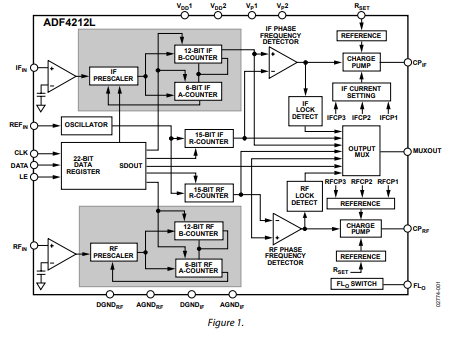

ADF4212L雙通道、低功耗PLL頻率合成器技術(shù)手冊

AD9578雙通道PLL精密頻率合成器技術(shù)手冊

AD9578雙通道PLL精密頻率合成器技術(shù)手冊

評論