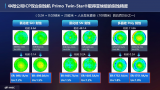

近日,中微半導體設備(上海)股份有限公司(以下簡稱“中微公司”,股票代碼“688012.SH”)宣布通過不斷提升反應臺之間氣體控制的精度,ICP雙反應臺刻蝕機Primo Twin-Star?又取得新的突破,反應臺之間的刻蝕精度已達到0.2A(亞埃級)。這一刻蝕精度在氧化硅、氮化硅和多晶硅等薄膜的刻蝕工藝上,均得到了驗證。該精度約等于硅原子直徑2.5埃的十分之一,是人類頭發絲平均直徑100微米的500萬分之一。這是等離子體刻蝕技術領域的又一次創新突破,彰顯了中微公司在技術研發上的深厚積累,進一步鞏固了公司在高端微觀加工設備市場的領先地位。

在200片硅片的重復性測試中,氧化硅、氮化硅和多晶硅的測試晶圓, 在左右兩個反應臺上各100片的平均刻蝕速度相差,各為每分鐘0.9埃,1.5埃和1.0埃。兩個反應臺之間平均刻蝕速度的差別(≤0.09%),遠小于一個反應臺加工多片晶圓刻蝕速度的差別(≤0.9%)。

自2004年創立之初,中微公司始終堅持為達到設備的最高性能和滿足客戶最嚴要求而發開,致力于為客戶提供高刻蝕性能、高生產效率和節約生產空間的刻蝕設備。2006年,公司研發的第一代雙反應臺電容耦合CCP刻蝕設備Primo D-RIE?在國際先進的邏輯客戶的產線上成功得到核準,隨之取得重復訂單,得到客戶的持續信任與支持。CCP的雙臺機Primo D-RIE?和Primo AD-RIE?的加工精度,兩個反應臺的刻蝕重復性和在生產線上的重復性也早已達到和Primo Twin-Star?相同的水平。

在兩個反應臺各輪流加工1000片的重復性測試中,兩個反應臺的平均刻蝕速度相差,只有每分鐘9埃,小于1.0納米。在海外先進存儲器生產線上,全年加工的12萬片晶圓的全過程中,兩個反應臺在兩個刻蝕應用上刻蝕速度的差別1sigma小于0.7%。

截至目前,Primo D-RIE?以及下一代產品Primo AD-RIE?在邏輯客戶的產線上的量產反應臺已經超過2000臺,并有近600個反應臺在國際最先進的邏輯產線上量產,其中相當一部分機臺已在5納米及更先進的生產線上用于量產。

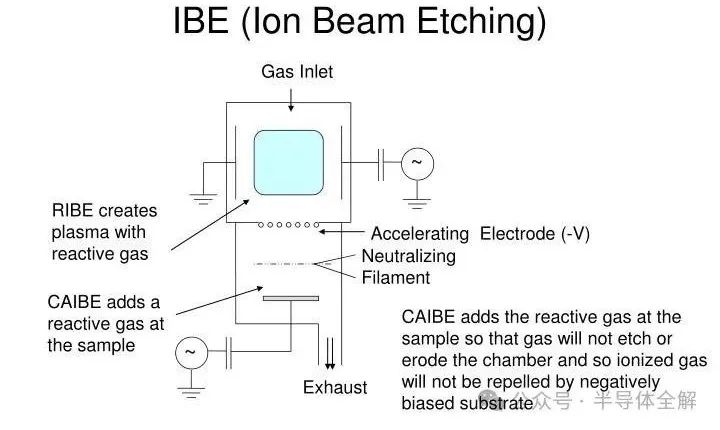

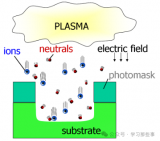

中微公司首創了單反應臺可以分別獨立操作也可以同時操作的雙反應臺刻蝕反應器,是占地面積小、輸出量高和成本低的刻蝕機。CCP和ICP的雙臺機已經證明了可以覆蓋60%以上的刻蝕應用。大量的生產線數據表明,雙反應臺和單反應臺刻蝕機呈現一樣的刻蝕性能、刻蝕穩定性和可靠性。憑借行業首創的可獨立工作的刻蝕設備雙臺機技術,通過超過20年的技術創新與經驗積累,中微公司研發的電感耦合ICP刻蝕設備Primo Twin-Star?首次取得了0.2A的業界首創的刻蝕精度。該產品采用獨創的低電容耦合LCC 3D線圈設計,雙反應臺腔體結構并結合創新的反應腔設計,可最大程度減弱非中心對稱抽氣口效應,可選多區溫控靜電吸盤(ESC)增強了對關鍵尺寸均勻性的控制,與其它同類設備相比,具有低成本、占地小和高產出的優異于特性,可應用于大多數先進邏輯和存儲器的刻蝕制程。

據業績快報顯示,中微公司2024年營業收入約90.65億元,較2023年增加約28.02億元。公司在過去13年保持營業收入年均增長大于35%,近四年營業收入年均增長大于40%的基礎上,2024年營業收入又同比增長約44.73%。其中,刻蝕設備收入約72.77億元,在最近四年收入年均增長超過50%的基礎上,2024年又同比增長約54.73%。中微公司綜合競爭優勢不斷增強,聚焦提高勞動生產率,在2022年達到人均銷售350萬元的基礎上,2024年人均銷售超過了400萬元,各項營運指標已達到國際先進半導體設備企業水平。

此外,中微公司持續加碼創新研發,2024年在研項目廣泛涵蓋六大類設備,積極推進超過二十款新型設備的研發工作,并在半導體薄膜沉積設備領域不斷突破,推出了多款LPCVD薄膜設備和ALD薄膜設備新產品,獲得了重復性訂單。公司新開發的硅和鍺硅外延EPI設備等多款新產品,也會在近期投入市場驗證。

中微公司將繼續瞄準世界科技前沿,將產品開發的十大原則始終貫穿于產品開發、設計和制造的全過程,打造更多具有國際競爭力的技術創新與差異化產品,持續踐行“五個十大”的企業文化,堅持三維發展戰略,實現高速、穩定、健康和安全的高質量發展,盡早在規模和競爭力上成為國際一流的半導體設備公司!

審核編輯 黃宇

-

半導體

+關注

關注

335文章

28563瀏覽量

232293 -

ICP

+關注

關注

0文章

75瀏覽量

13131 -

刻蝕機

+關注

關注

0文章

53瀏覽量

4463

發布評論請先 登錄

半導體刻蝕工藝技術-icp介紹

中微公司推出12英寸晶圓邊緣刻蝕設備Primo Halona

干法刻蝕的概念、碳硅反應離子刻蝕以及ICP的應用

半導體濕法刻蝕殘留物的原理

芯片制造中的濕法刻蝕和干法刻蝕

濕法刻蝕步驟有哪些

一文看懂刻蝕角度與ICP-RIE射頻功率的關系

半導體干法刻蝕技術解析

中微公司ICP雙臺刻蝕機Primo Twin-Star?取得亞埃級刻蝕精度

中微公司ICP雙臺刻蝕機Primo Twin-Star?取得亞埃級刻蝕精度

評論