? AXI接口筆記

第一章問題記錄

第1節接收數據全0或全1

1.1問題現象

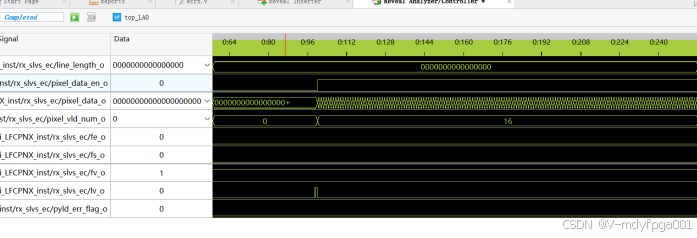

上圖中,pixel_data_o是EC IP核輸出的圖像數據,正確的話會如上圖所示,圖像數據每個時鐘會變化并且值是不固定的。

本次出現的錯誤現象是:pixed_data_o是有輸出的,但輸出全是0或者是全是1,并且在最后一個像素出現pyld_err_flag_o的錯誤指示。

1.2問題原因

經過LATTICE的原廠工程師定位,確定是IP核導致的reveal顯示問題,需要重新安裝EC的IP核。

1.3解決方法

安裝EC的IP核,安裝文件:F:svnmdy_flow_common2_design8_LVDS4_mdySlvdsEclatticesemi.com_slvsec_rx_1.2.0.ipk

安裝過程:

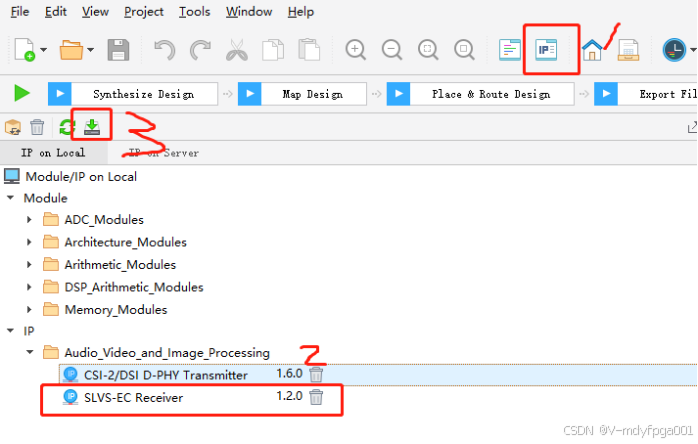

1.3.1.打開LATTICE的軟件radiant

1.3.2.打開圖中1所示的IP Catalog,顯示2是否存在,如果存在就刪除;然后點擊上圖3所示的安裝位置。

1.3.3.選擇安裝文件,接提示要求安裝即可。安裝完成后,在上圖中2的位置將又再出現。

1.3.4.重裝生成IP核。

第2節接收不到任何東西

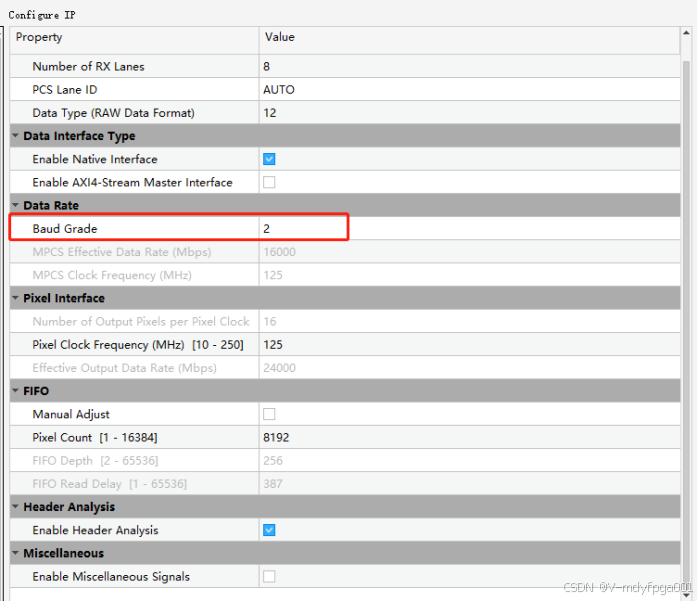

2.1.如果SERDES速率是5G,則BAUD GRADE選用3;如果是2.5G,則選用2;千萬不要搞錯。

2.2.綜合工具要改為:synplify pro。使用LSE將出現不穩定情況,綜合后將出現全部接收不到的情況,不穩定。

2.3.使用serdes IP核,去接收數據,看是否有錯誤提示。注意,本次定位,可以看到信號質量挺好,眼圖也是很好的,但從SERDES上看就是有誤碼。懷疑是頻偏問題導致的,在攝像頭一側,修改了時鐘線,問題解決。

審核編輯 黃宇

?

-

接口

+關注

關注

33文章

8971瀏覽量

153464 -

AXI

+關注

關注

1文章

136瀏覽量

17175

發布評論請先 登錄

RDMA簡介9之AXI 總線協議分析2

RDMA簡介8之AXI 總線協議分析1

NVMe IP之AXI4總線分析

AMD Versal Adaptive SoC Clock Wizard AXI DRP示例

NVMe簡介之AXI總線

NVMe協議簡介之AXI總線

NVMe控制器IP設計之接口轉換

一文詳解AXI DMA技術

一文詳解Video In to AXI4-Stream IP核

ZYNQ基礎---AXI DMA使用

AMBA AXI4接口協議概述

Xilinx NVMe AXI4主機控制器,AXI4接口高性能版本介紹

AXI 接口設計避坑指南:AXI接口筆記

AXI 接口設計避坑指南:AXI接口筆記

評論