一 增量式編碼器原理介紹

增量式編碼器是一種將位移信息轉換成周期性電信號,再將電信號轉換成脈沖計數的裝置。

通常增量式編碼器的接線輸出為兩根電源線,A,B,Z三個脈沖信號。其中可以通過A,B信號的相位關系來判斷編碼器的旋轉方向,可以人為規定若A相在前,B相落后90o 則為正方向,反之為負方向。

旋轉角度的計算也很簡單,

順時針:

θ = ( k + 1 ) ? 360 分 辨 率 heta=(k+1)*frac{360}{分辨率} θ=(k+1)?分辨率360

逆時針:

θ = ( 分 辨 率 ? ( k + 1 ) ) ? 360 分 辨 率 heta=(分辨率-(k+1))*frac{360}{分辨率} θ=(分辨率?(k+1))?分辨率360

每旋轉過一個單位刻度,A,B相都會產生一個脈沖,Z相信號是每轉一圈產生一個周期的高電平。

倍頻: 實際應用中往往會采用兩倍頻或者四倍頻的方式來提高精度,一個周期內 A,B相的信號都會產生四次邊沿跳變,兩倍頻可以在上升沿,下降沿各計數一次;四倍頻則是每個邊沿變化都計數。

兩倍頻計數規則: 在A或B的上升、下降沿都計數。

四倍頻計數規則: 當A為高電平時,B在上升沿則加1,下降沿則減1;A為低電平時,B在下降沿則減1,上升沿則加1;B為高電平時,A在上升沿則減1,下降沿則加1;在B為低電平時,A在上升沿則加1,下降沿則減1。

PUL =(A1 ^ B2) ^ (A2 ^ B1)

二 硬件實現

在查閱資料論文后,發現大部分都是采用的是三個模塊:頂層模塊;倍頻鑒相模塊,以及計數模塊。

其實完全可以綜合為一個模塊同時完成倍頻鑒相計數工作。代碼參考這位大佬

`timescale 1ns / 1ps module bianmaqi2(clk,rst_n ,quadA, quadB, position_out,A,B,DIR,index); input clk,rst_n, quadA, quadB,index; output [15:0] position_out; output A,B,DIR; reg [2:0] quadA_delayed, quadB_delayed; reg A,B,DIR; reg [15:0] position; always @(posedge clk) quadA_delayed <= {quadA_delayed[1:0], quadA}; always @(posedge clk) quadB_delayed <= {quadB_delayed[1:0], quadB}; //輸入緩存打拍 wire count_enable = quadA_delayed[1] ^ quadA_delayed[2] ^ quadB_delayed[1] ^ quadB_delayed[2]; //PUL =(A1^B2)^(A2^B1) wire count_direction = quadA_delayed[1] ^ quadB_delayed[2]; //DIR = C^D C是A1打一拍 D是B1打兩拍 always @(posedge osc or negedge rst_n ) begin if(!rst_n)begin position<=16'd0; A<=0; B<=0; DIR<=0; //復位信號 必須有復位信號來賦初值 否則在testbench中輸出為高阻態 end else if(count_enable) begin if(count_direction) position<=position+1'b1; else position<=position-1'b1; A <= quadA_delayed[2]; B <= quadB_delayed[2]; DIR <= count_direction; end else position<=position; end assign position_out = position; endmodule

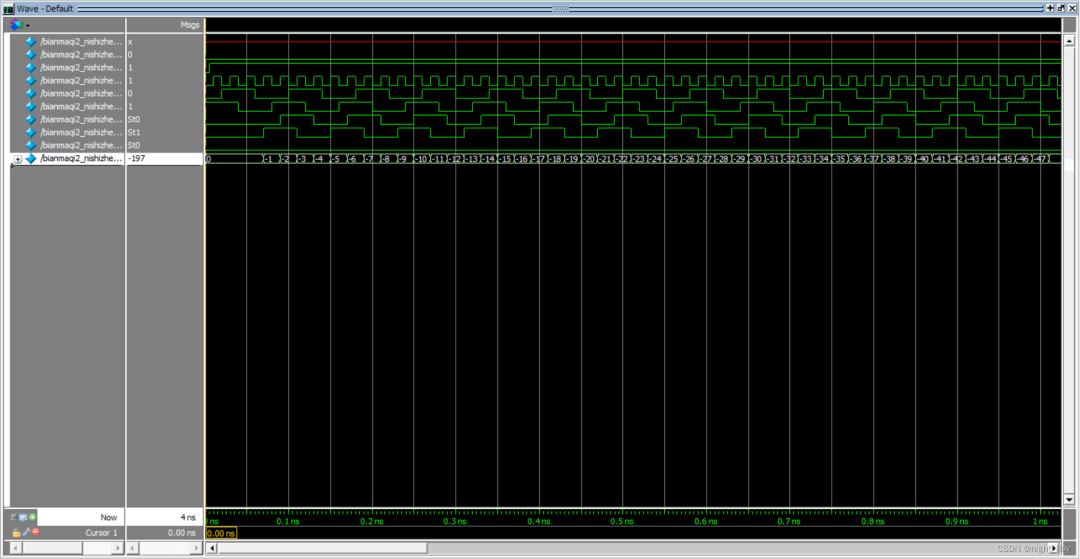

三 測試平臺

分別測試正轉和反轉;

正轉即A比B超前90°;反轉即B比A超前90°。

`timescale 1 ps/ 1 ps module bianmaqi2_tb(); // constants // general purpose registers reg eachvec; // test vector input registers reg index; reg rst_n; reg osc; reg quadA; reg quadB; // wires wire A; wire B; wire DIR; wire [15:0] position_out; // assign statements (if any) bianmaqi2 i1 ( // port map - connection between master ports and signals/registers .A(A), .B(B), .rst_n(rst_n), .DIR(DIR), .index(index), .osc(osc), .position_out(position_out), .quadA(quadA), .quadB(quadB) ); initial begin //initialize inputs rst_n=1'b0; osc=1'b0; quadA =1; quadB =0; index =0; #5 rst_n=1'b1; end initial begin repeat(50)begin #20 quadB=1; #20 quadA=0; #20 quadB=0; #20 quadA=1; end $stop; end always #10 osc =~osc; //產生50MHz時鐘源 endmodule

`timescale 1 ps/ 1 ps

module bianmaqi2_nishizhen_tb();

// constants

// general purpose registers

reg eachvec;

// test vector input registers

reg index;

reg rst_n;

reg osc;

reg quadA;

reg quadB;

// wires

wire A;

wire B;

wire DIR;

wire [15:0] position_out;

// assign statements (if any)

bianmaqi2 i1 (

// port map - connection between master ports and signals/registers

.A(A),

.B(B),

.rst_n(rst_n),

.DIR(DIR),

.index(index),

.osc(osc),

.position_out(position_out),

.quadA(quadA),

.quadB(quadB)

);

initial

begin

//initialize inputs

rst_n=1'b0;

osc=1'b0;

quadA =0;

quadB =1;

index =0;

#5

rst_n=1'b1;

end

initial

begin

repeat(50)begin

#20

quadA=1;

#20

quadB=0;

#20

quadA=0;

#20

quadB=1;

end

$stop;

end

always #10 osc =~osc;

//產生50MHz時鐘源

endmodule

四 總結

fpga設計模塊其實實現很簡單,主要還是Quartus和Modelsim的聯合仿真部分遇到了問題,主要還是testbench的編寫需要強化學習。

-

FPGA

+關注

關注

1643文章

21960瀏覽量

614068 -

電源線

+關注

關注

1文章

377瀏覽量

22466 -

電信號

+關注

關注

1文章

842瀏覽量

20987 -

增量式編碼器

+關注

關注

2文章

39瀏覽量

12875

原文標題:FPGA接口實現----增量式編碼器

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

增量式旋轉編碼器設計

基于FPGA增量式編碼器的接口設計

M30增量式編碼器介紹

STM32-增量式旋轉編碼器測量

增量式編碼器原理介紹

增量式編碼器原理介紹

評論