以下文章來源于學習那些事,作者小陳婆婆

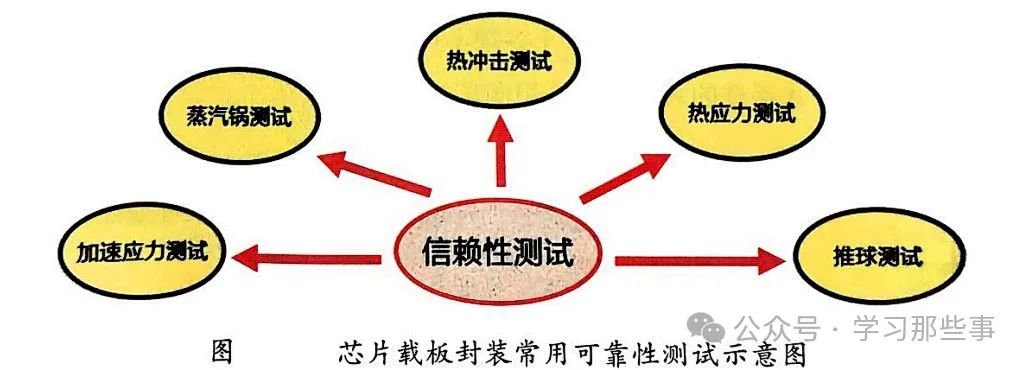

可靠性測試

可靠性,作為衡量芯片封裝組件在特定使用環境下及一定時間內損壞概率的指標,直接反映了組件的質量狀況,本文分述如下

可靠性測試概述

芯片封裝成品六項可靠性測試

1可靠性測試概述

可靠性測試的意義

可靠性測試旨在評估產品在特定狀態下的壽命影響,確認產品質量是否穩定,并據此進行必要的修正。與功能測試不同,可靠性測試更注重預測產品在長期使用中的表現,從而幫助客戶以最快、最經濟的方式評估芯片的狀況。

可靠性測試的條件與項目

可靠性測試的條件通常與電壓、濕度和溫度等環境參數有關。不同的可靠性測試項目針對的是不同功能的元器件需求。

常用的可靠性測試項目歸類及闡述如下:

溫度循環測試:評估芯片封裝組件在溫度變化下的適應性和穩定性。

濕度測試:檢測組件在潮濕環境下的耐腐蝕性和絕緣性能。

電壓應力測試:驗證組件在電壓波動或過載情況下的穩定性和可靠性。

機械強度測試:評估組件在受力情況下的耐久性和抗損壞能力。

其他專項測試:如熱沖擊測試、鹽霧測試等,針對特定應用場景下的可靠性需求。

進行可靠性測試時,封裝廠通常會參照以下國際組織的標準和規范:

國際電工委員會(IEC)

美國軍規(Mil-std)

國際電子工業聯接協會(IPC)

半導體工業標準組織(JEDEC)

日本工業標準協會(JIS)

2芯片封裝成品六項可靠性測試

在芯片封裝領域,封裝廠為確保產品質量,通常會執行一系列可靠性測試。以下是六項常見的可靠性測試項目,每項測試都有其特定的內容與目的:

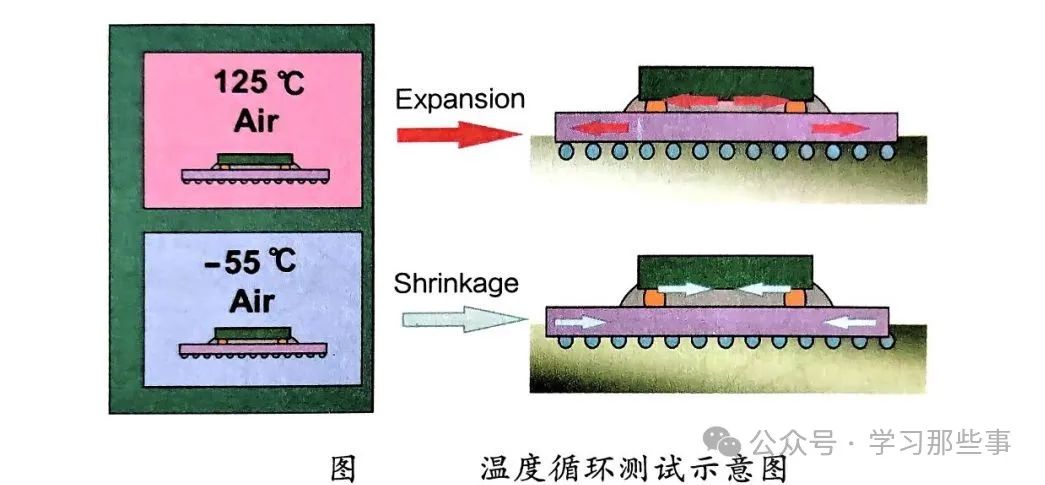

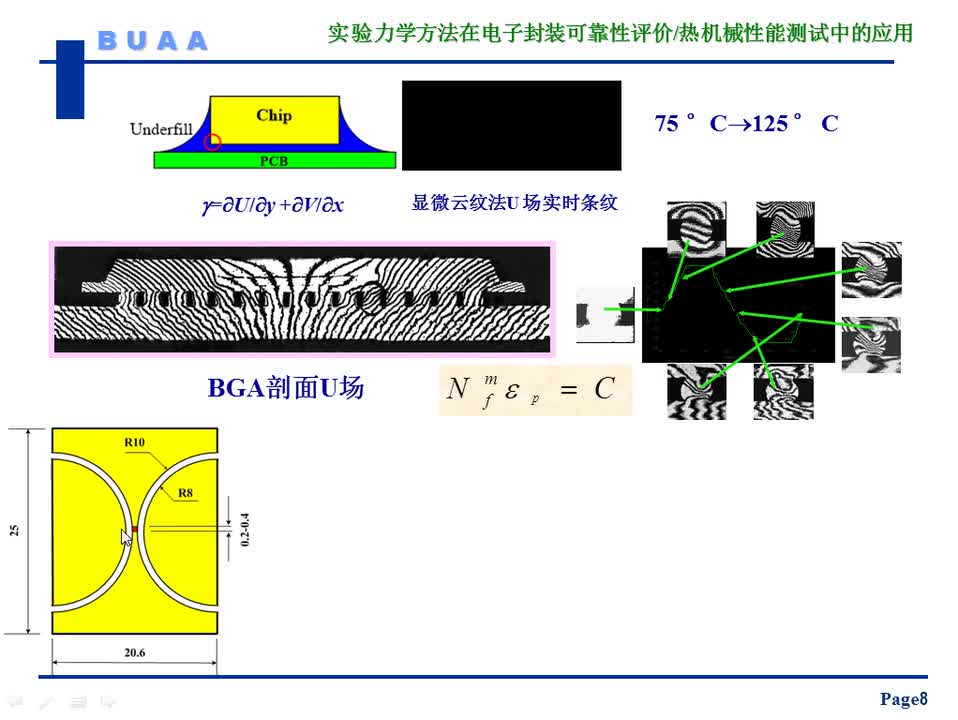

1. 溫度循環測試(Temperature Cycling Test, TCT)

測試內容與目的:通過將封裝體暴露在高低溫氣體轉換的環境中,評估封裝體抵抗溫度差異化的能力。該測試旨在檢驗芯片產品中不同熱膨脹系數的金屬間接口的接觸良率。

測試條件:常見的測試條件為-65℃至150℃之間往復循環1000次,但具體條件可能因封裝廠而異。

失效機制:電路的短路和斷路、材料的破壞及結構機械變形。

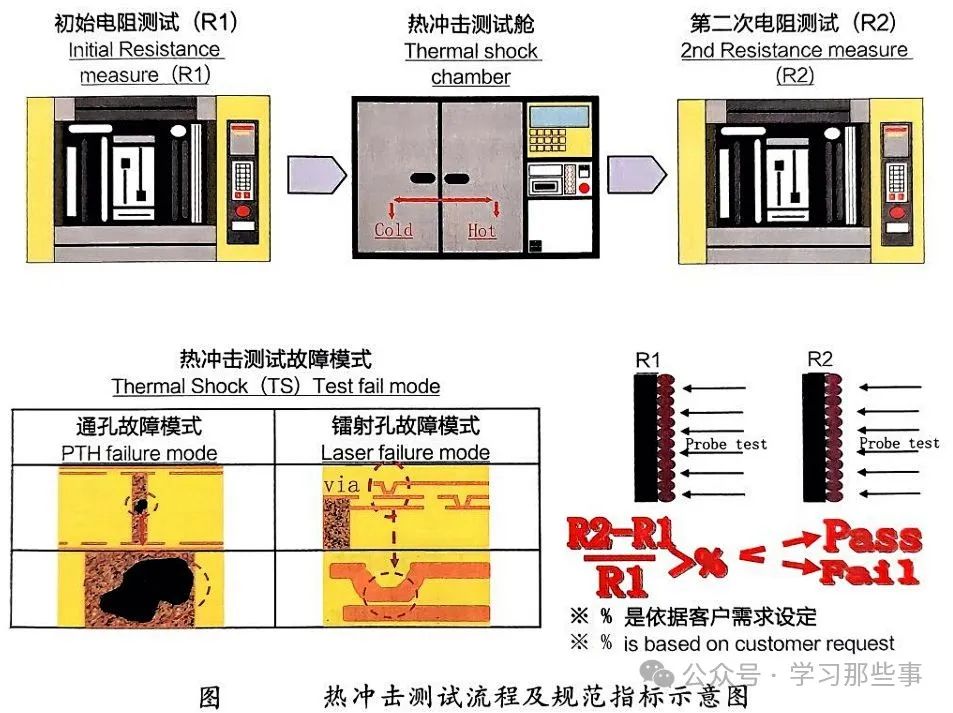

2. 熱沖擊測試(Thermal Shock Test, TST)

測試內容與目的:與溫度循環測試類似,但通過將封裝體暴露于高低溫液體的轉換環境中來測試其抗熱沖擊的能力。該測試同樣旨在評估金屬間接口的接觸良率。

測試條件:常見的測試條件與溫度循環測試相似,但使用的是液體介質。

失效機制:與溫度循環測試相似,包括電路的短路和斷路、材料的破壞及結構機械變形。

區別:TCT偏重于芯片封裝的測試,而TST偏重于晶圓的測試。

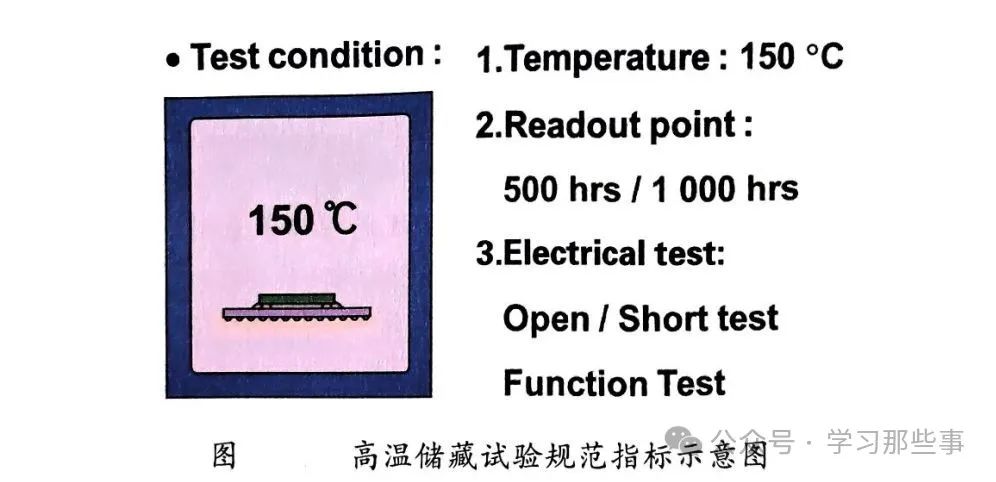

3. 高溫儲藏試驗(High Temperature Storage Test, HTST)

測試內容與目的:通過將封裝體長時間暴露于高溫環境中,測試其在長期高溫狀況下的性能穩定性。該測試旨在評估封裝體中物質活性增強、物質遷移擴散對電路性能的影響。

測試條件:通常將封裝體置于150℃的高溫氮氣爐中,持續500小時或1000小時。

失效機制:電路的短路和斷路、材料的破壞及結構機械變形。

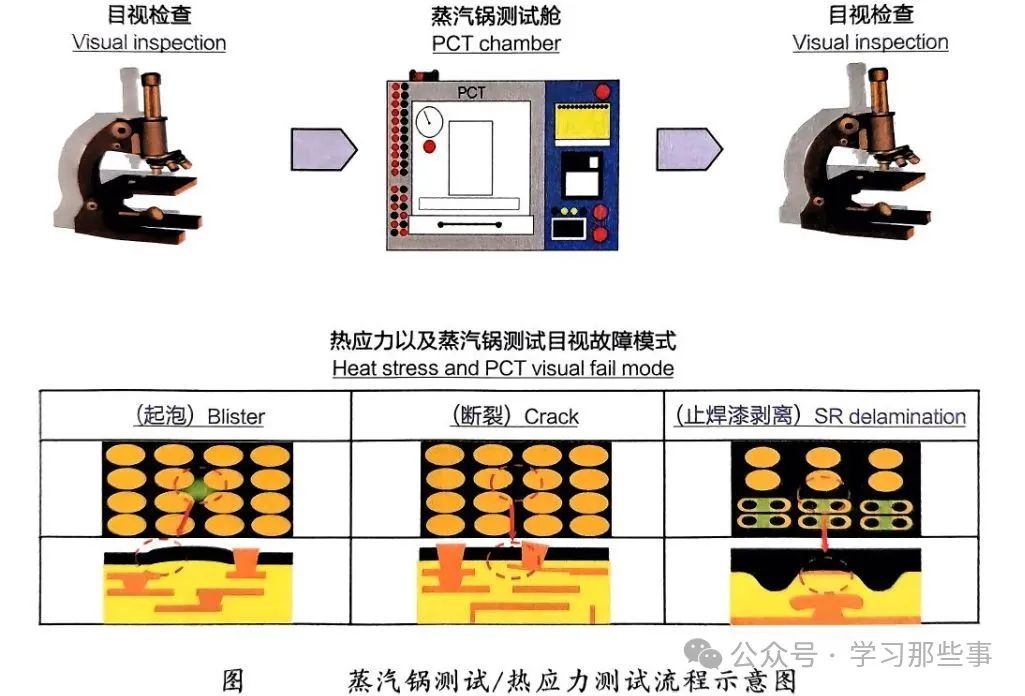

4. 蒸汽鍋試(Pressure Cooker Test, PCT)

測試內容與目的:主要測試封裝產品抵抗環境濕度的能力,并通過增加壓強來縮短測試時間。該測試旨在評估芯片產品在高溫、高濕、高壓條件下的濕度抵抗能力。

測試條件:通常將封裝體置于130℃、85%相對濕度的環境中,并施加2個標準大氣壓的壓力。

失效機制:化學金屬腐蝕、封裝塑封異常。

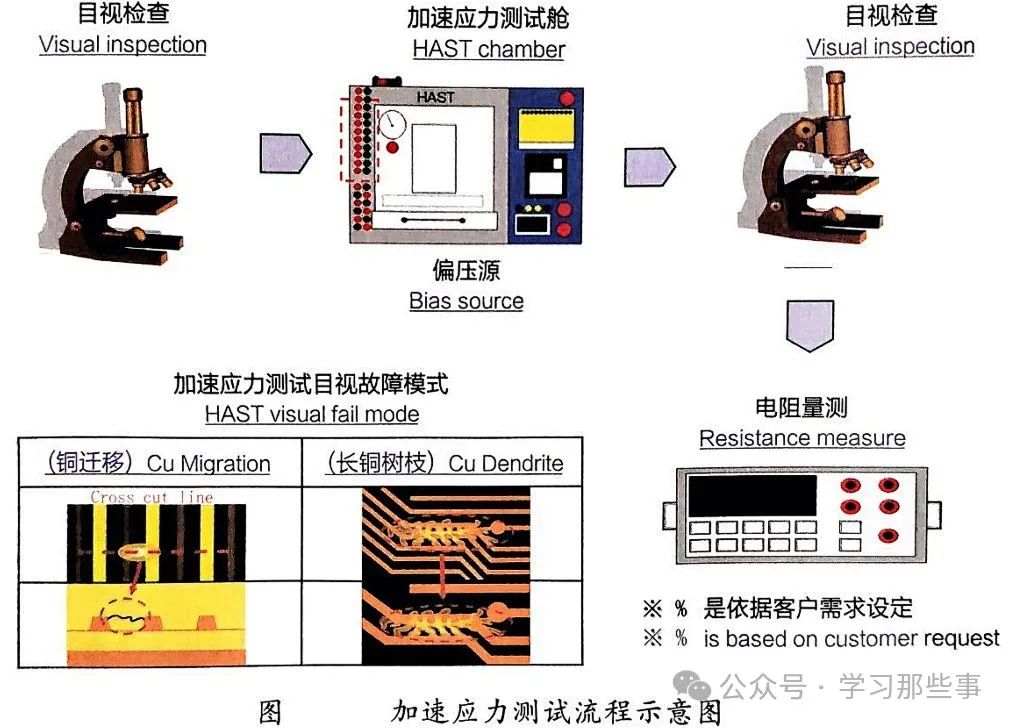

5. 加速應力測試(High Accelerated Temperature and Humidity Stress Test, HAST)

測試內容與目的:在高溫高濕以及偏壓的環境下測試封裝體的抗濕度能力。該測試旨在加速芯片產品的失能過程,以評估其在極端條件下的性能穩定性。

測試條件:通常將封裝體置于130℃、85%相對濕度的環境中,并施加1.1伏特的偏壓和2.3個標準大氣壓的壓力。

失效機制:線路腐蝕、封裝塑封異常。

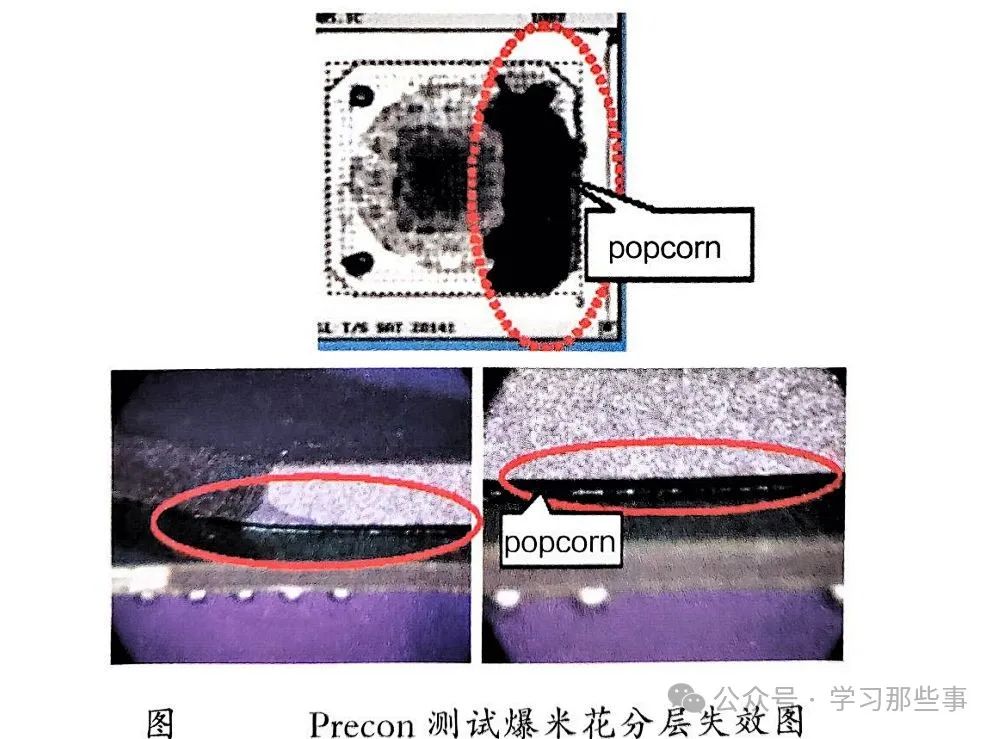

6. Precon測試(Precondition Test)

測試內容與目的:模擬芯片封裝完成后運輸到下游組裝廠裝配成最終產品的過程中可能經歷的環境變化。該測試旨在了解電子元器件的吸濕狀況,并評估其在后續加工過程中的性能穩定性。

測試條件:測試前確認封裝電器成品性能無問題,然后進行溫度循環測試(如TCT)、吸濕測試和后段焊錫加工過程的模擬。

失效機制:爆米花效應、分層失效等問題,這些問題通常是由于封裝體在吸濕后遭遇高溫導致內部水分急速膨脹所致。

為突破傳統載板生產工藝的瓶頸,引入了類載板制造方法,為硬質載板的生產帶來了升級機會,并拓寬了封裝廠新材料供應商的選擇范圍。通過以上措施,可以確保電子產品在長期使用中的穩定性和性能,提高客戶滿意度,并推動芯片封裝行業的持續發展。

-

半導體

+關注

關注

335文章

28613瀏覽量

232834 -

芯片封裝

+關注

關注

11文章

574瀏覽量

31256 -

可靠性測試

+關注

關注

1文章

111瀏覽量

14452

原文標題:一文了解芯片可靠性測試

文章出處:【微信號:芯長征科技,微信公眾號:芯長征科技】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

提供半導體工藝可靠性測試-WLR晶圓可靠性測試

芯片封裝可靠性測試詳解

芯片封裝可靠性測試詳解

評論