Hello,大家好,我們來分享下先進封裝中TSV需要的相關(guān)設(shè)備。

TSV 生產(chǎn)流程涉及到深孔刻蝕、PVD、CVD、銅填充、微凸點及電鍍、清洗、減薄、鍵合等二十余種設(shè)備,其中深孔刻蝕、氣相沉積、銅填充、清洗、CMP去除多余的金屬、晶圓減薄、晶圓鍵合等工序涉及的設(shè)備最為關(guān)鍵。

1)深孔刻蝕設(shè)備

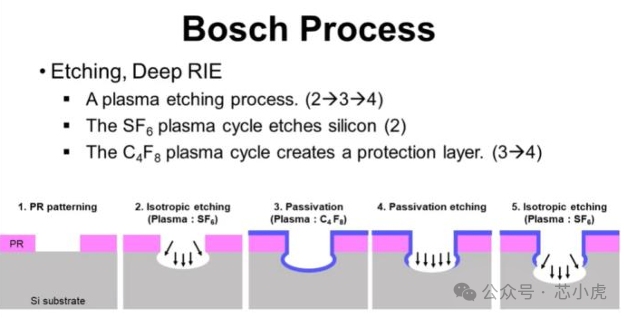

深孔刻蝕是TSV的關(guān)鍵工藝,目前首選技術(shù)是基于Bosch工藝的干法刻蝕。深反應等離子刻蝕設(shè)備是感應耦合高密度等離子體干法刻蝕機(InductivelyCoupled Plasma Etcher),采用半導體刻蝕機的成熟技術(shù),獨特設(shè)計的雙等離子體源實現(xiàn)了對腔室內(nèi)等離子體密度的均勻控制,滿足硅高深寬比刻蝕工藝的要求。具有穩(wěn)定可靠的工藝性能、寬闊的工藝窗口和良好的工藝兼容性,用于晶片的高深寬比刻蝕。

2)氣相沉積設(shè)備

氣相沉積設(shè)備主要用于薄膜電路表面的高低頻低應力氧化硅等薄膜淀積。設(shè)備具有低溫TEOS工藝沉積氧化硅薄膜,應力易調(diào)控,適用于薄膜電路制造中保護膜層的沉積。設(shè)備應具有預真空室、基片傳送模塊以及工藝模塊等,傳片及工藝過程自動化。絕緣層做好后,通過物理氣相沉積法(PVD)沉積金屬擴散阻擋層和種子層,為后續(xù)的銅填充做好準備。后續(xù)的電鍍銅填充要求TSV側(cè)壁和底部具有連續(xù)的阻擋層和種子層。種子層的連續(xù)性和均勻性被認為是 TSV 銅填充最重要的影響因素。根據(jù)硅通孔的形狀、深寬比及沉積方法不同,種子層的特點也各有不同,種子層沉積的厚度、均勻性和粘合強度是極為重要的指標。

3)銅填充設(shè)備

深孔金屬化電鍍設(shè)備用于新一代高頻組件高深寬比通孔填孔電鍍銅工藝,解決高深寬比微孔內(nèi)的金屬化問題,提高互聯(lián)孔的可靠性。TSV填孔鍍銅工序是整個TSV工藝里最核心、難度最大的工藝,對設(shè)備的要求比較高,成熟的用于TSV填孔鍍銅的設(shè)備價格昂貴。

4)減薄拋光設(shè)備

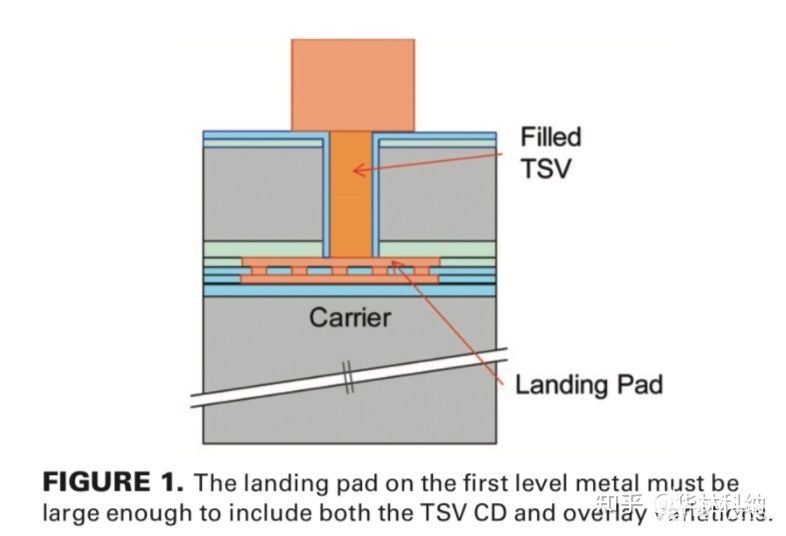

一旦完成了銅填充,則需要對晶圓進行減薄拋光。TSV要求晶圓減薄至50μm甚至更薄,要使硅孔底部的銅暴露出來,為下一步的互連做準備。目前晶圓減薄可以通過機械研磨、化學機械拋光、濕法及干法化學處理等不同的加工工序來實現(xiàn),但晶圓很難容忍減薄過程中的磨削對晶圓的損傷及內(nèi)在應力,其剛性也難以使晶圓保持原有的平整狀態(tài),同時后續(xù)工藝的晶圓傳遞、搬送也遇到了很大的問題。目前業(yè)界的多采用一體機的思路,將晶圓的磨削、拋光、貼片等工序集合在一臺設(shè)備內(nèi)。

5)清洗設(shè)備

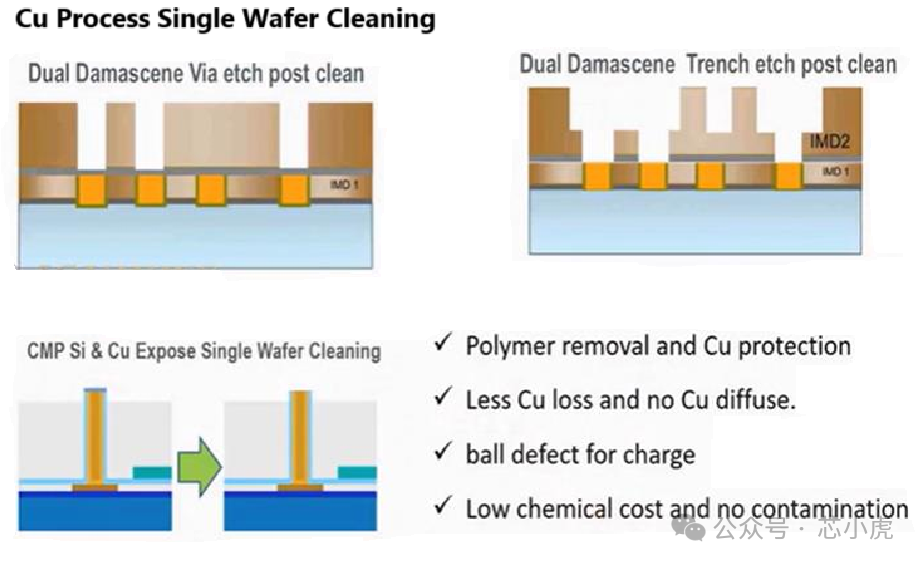

TSV 的濕法清洗不同于晶圓級封裝等先進封裝,其中有幾個關(guān)鍵工序需用到清洗:

①TSV刻蝕后清洗:有比較重的硅的殘留、側(cè)壁的polymer比較重,清洗的時候不能破壞底部的二氧化硅;

②TSV長完liner后要把底部的二氧化硅打開后清洗,清洗底部的同時不能破壞側(cè)壁長好的liner的二氧化硅;

③大馬士革正面制程刻蝕后的清洗包括Via刻蝕后和Trench刻蝕后;

④露銅過程前后的清洗。

6)檢測量測設(shè)備

在后段封裝工藝中,芯片倒裝(Flip-chip)、圓片級封裝(Wafer-level Packaging)和硅通孔(Through-silicon Via,TSV)等先進工藝要求對凸點(Bump)、通孔(TSV)、銅柱(Copper pillar)等的缺損/異物殘留及其形狀、間距、高度的一致性,以及重布線層(Re-distribution layer,RDL)進行無接觸定量檢查和測量,以保證集成電路芯片生產(chǎn)線快速進入量產(chǎn)階段并獲取穩(wěn)定的高成品率和高經(jīng)濟效益。

-

工藝

+關(guān)注

關(guān)注

4文章

668瀏覽量

29244 -

TSV

+關(guān)注

關(guān)注

4文章

120瀏覽量

81832 -

先進封裝

+關(guān)注

關(guān)注

2文章

460瀏覽量

501

原文標題:半導體先進封裝中TSV工藝需要的設(shè)備有哪些?

文章出處:【微信號:深圳市賽姆烯金科技有限公司,微信公眾號:深圳市賽姆烯金科技有限公司】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

用于3D封裝的穿硅通過最后光刻的覆蓋性能(上)

硅通孔封裝工藝流程與技術(shù)

先進封裝之TSV及TGV技術(shù)初探

先進封裝關(guān)鍵技術(shù)之TSV框架研究

簡單介紹硅通孔(TSV)封裝工藝

硅通孔(TSV)電鍍

什么是TSV封裝?TSV封裝有哪些應用領(lǐng)域?

TSV關(guān)鍵工藝設(shè)備及特點

TSV的工藝流程和關(guān)鍵技術(shù)綜述

先進封裝中的TSV/硅通孔技術(shù)介紹

TSV以及博世工藝介紹

先進封裝中TSV工藝需要的相關(guān)設(shè)備

先進封裝中TSV工藝需要的相關(guān)設(shè)備

評論