前言

control_interface.v文件里已經(jīng)寫了非常詳盡的代碼備注。本文繼續(xù)對該文件代碼進行講解,并給出SignalTap波形輔助讀者理解。

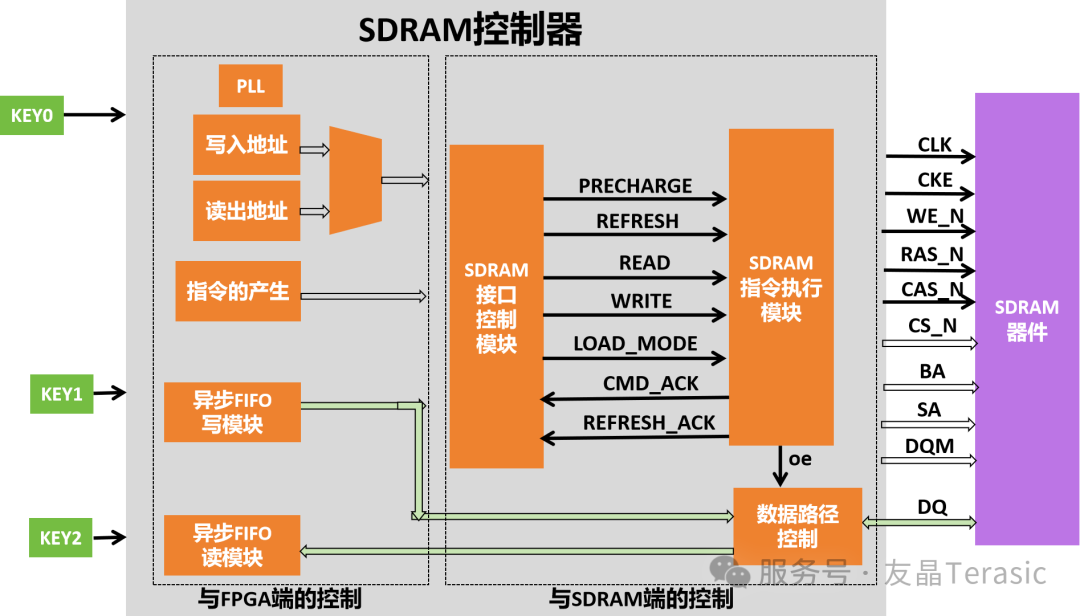

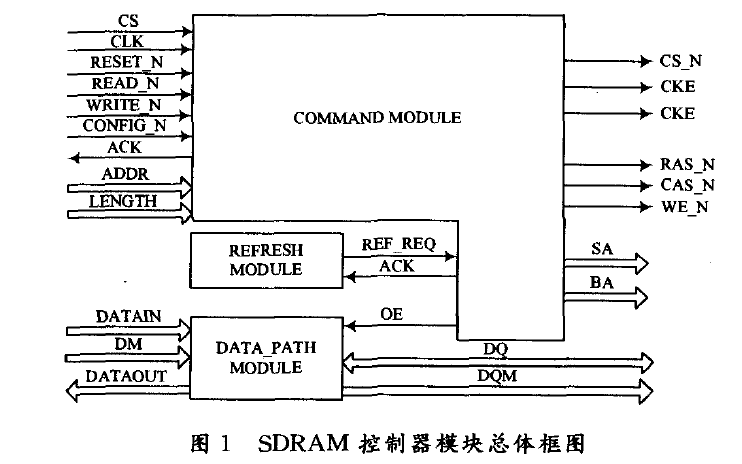

下圖是本案例的功能框圖。

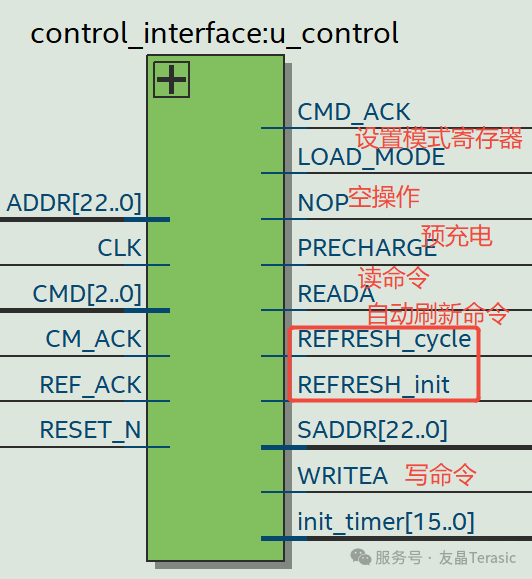

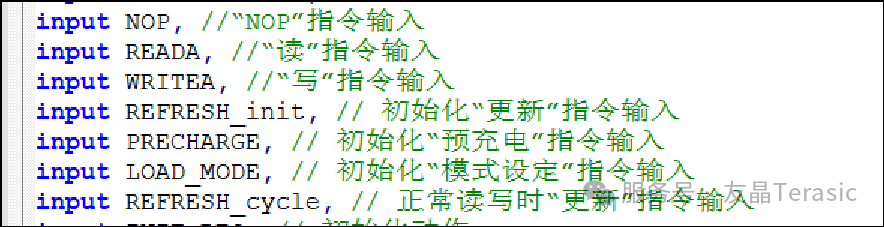

control_interface.v文件對應(yīng)圖中SDRAM接口控制模塊,該模塊主要控制SDRAM命令的產(chǎn)生,包括空操作命令、預(yù)充電命令、自動刷新命令、加載模式寄存器命令和讀寫命令等。如下是該模塊的RTL視圖:

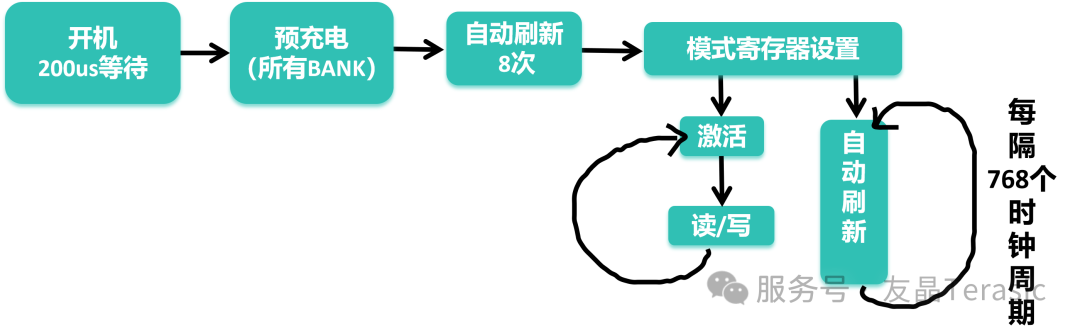

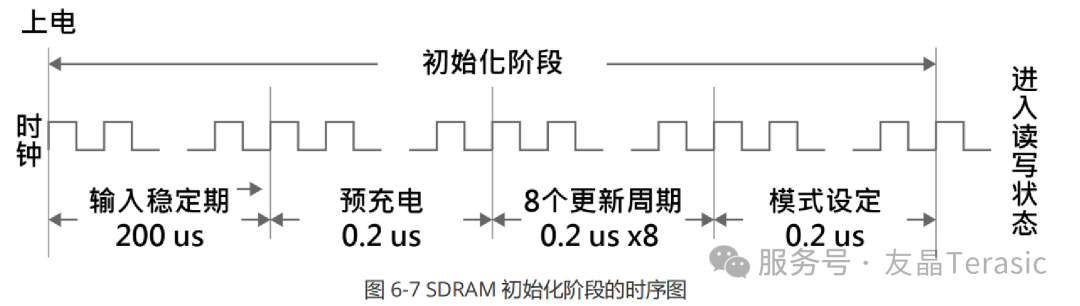

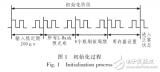

根據(jù)IS42R16320D 的時序圖可知該SDRAM上電后約經(jīng)過 200us 才進入穩(wěn)定期,在這段時間不可以對 SDRAM 做任何的操作(除了發(fā)送NOP命令), 200us 之后要對所有的區(qū)塊進行預(yù)充電,接著再給SDRAM發(fā)送 8次自動刷新命令,最后才進行SDRAM模式寄存器的設(shè)定。完成了初始化過程之后,SDRAM 才能進行正常的讀寫操作。整個過程可簡化為下圖所示:

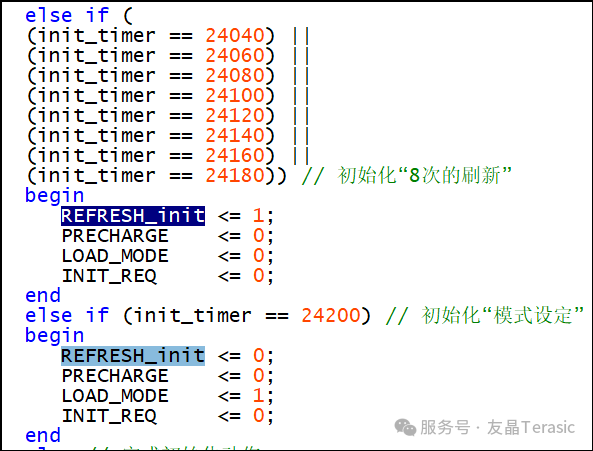

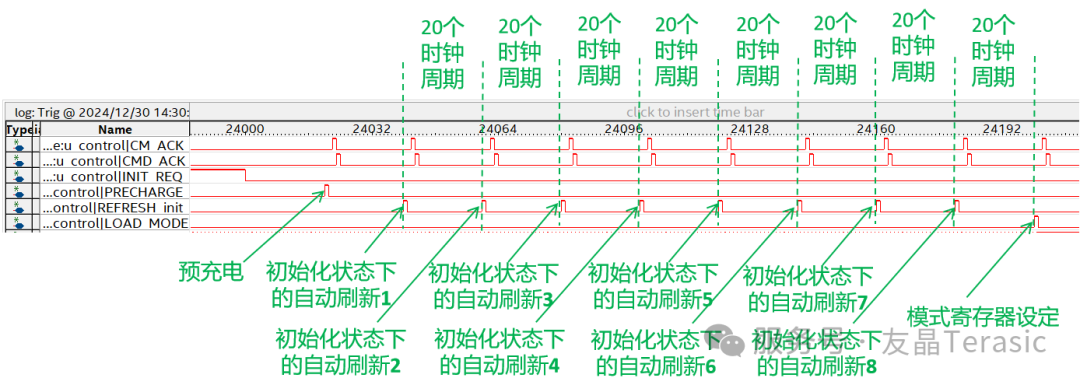

control_interface.v模塊工作時鐘100MHz,由Sdram_Control.v的PLL模塊提供。以100MHz時鐘周期計算,200us需要經(jīng)歷20000個周期。另外,參考IS42R16320D的datasheet或者參考02-SDRAM控制器的設(shè)計——解讀IS42R16320D的數(shù)據(jù)手冊可知預(yù)充電最少要2個時鐘周期,自動刷新命令完成需要至少8個時鐘周期,模式寄存器的設(shè)定至少也要2個時鐘周期。為了保險起見,將預(yù)充電、自動刷新和模式寄存器設(shè)定等操作的等待周期都設(shè)定為20個時鐘周期(也就是0.2us)。

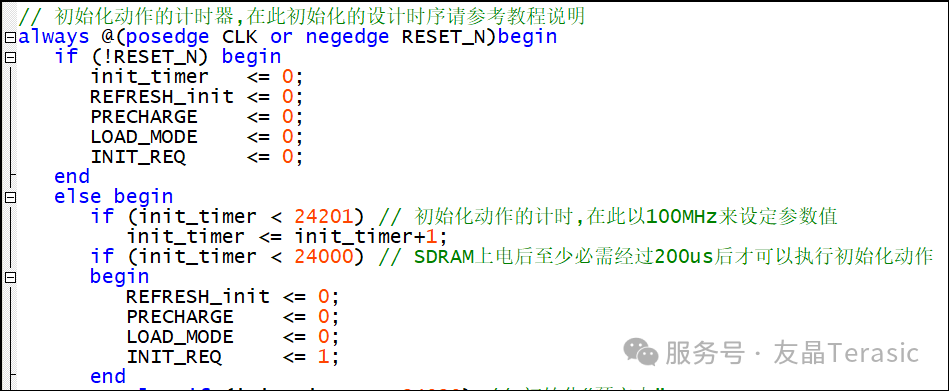

代碼里面首先設(shè)計兩個計數(shù)器,第一個計數(shù)器是初始化動作的計時器。為了保險起見,初始化先等待24000個時鐘周期:

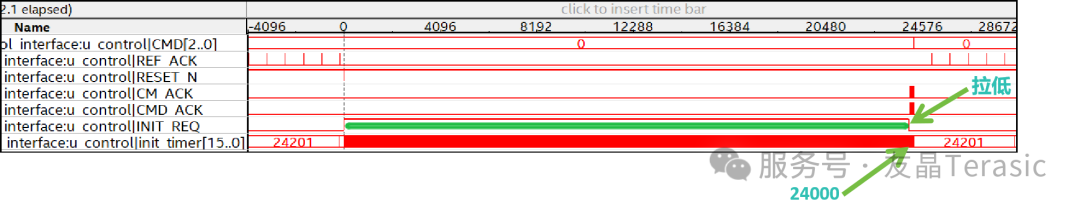

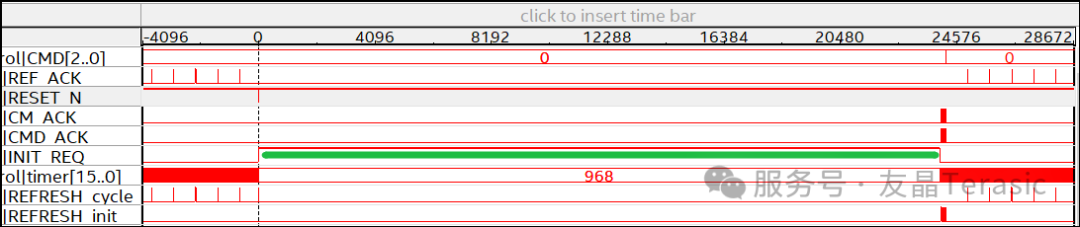

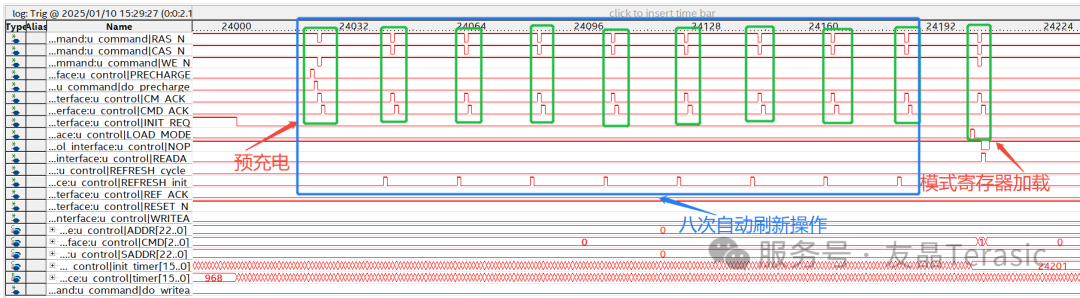

從SignalTap波形圖可以看到INIT_REQ在init_timer從0計數(shù)到24000以后拉低了。INIT_REQ拉高(綠色部分)指示了SDRAM開機后的輸入穩(wěn)定期。

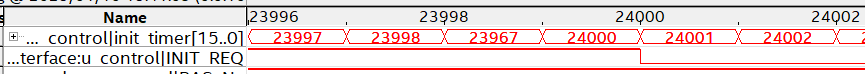

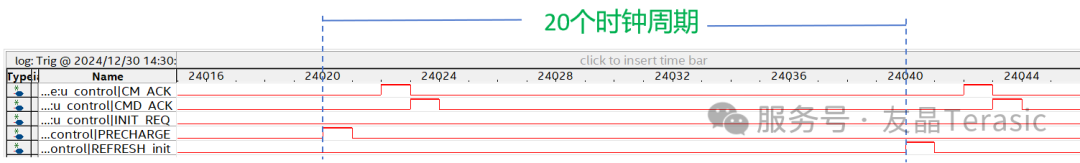

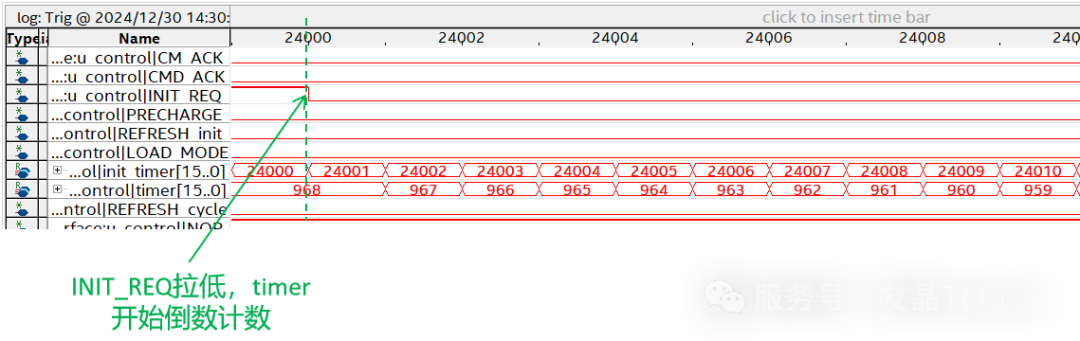

把INIT_REQ和init_timer局部放大如下:

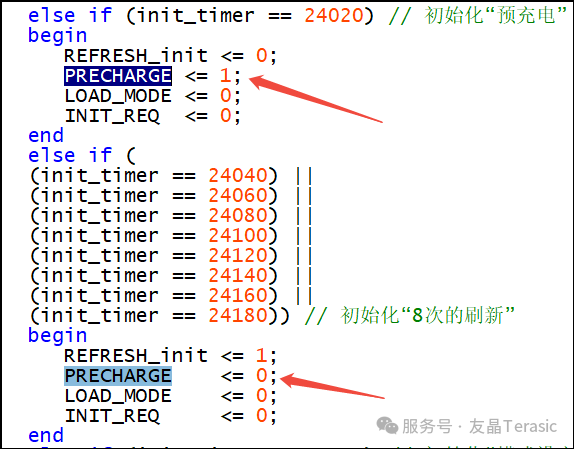

代碼里面實現(xiàn)預(yù)充電操作等待20個時鐘周期:

代碼里面實現(xiàn)每次自動刷新都等待20個時鐘周期(總共8次):

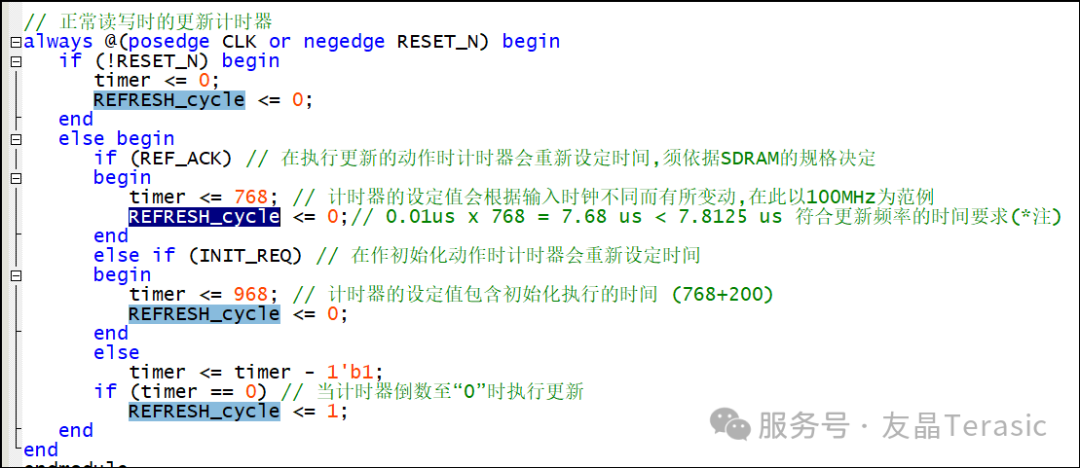

第二個計數(shù)器是正常讀寫時的自動刷新間隔計時器,因為SDRAM必須要不斷進行刷新才能保留數(shù)據(jù) ,由IS42R16320D數(shù)據(jù)手冊可知每一行刷新的循環(huán)周期最多為64ms。DE10-Standard開發(fā)板上的SDRAM有13位的行地址,共有8192行,而每一次的刷新命令只能對一行有效,所以在最長 64ms / 8192 = 7.8125us 的時間間隔內(nèi),就必須發(fā)一次刷新的命令。在工作時鐘100M下,這里刷新周期設(shè)置為768。

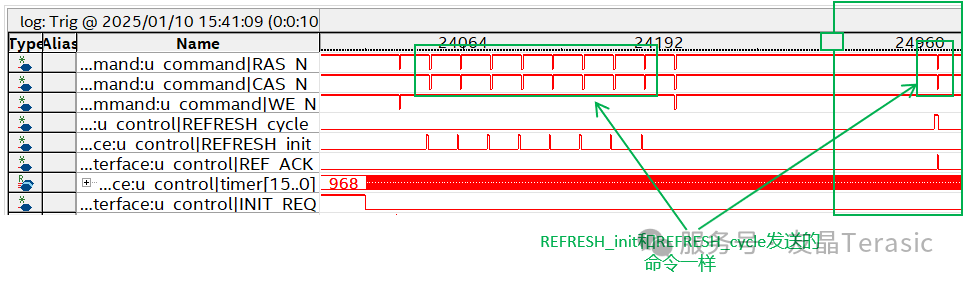

從SignalTap波形圖可以看到timer的值在輸入穩(wěn)定等待期(INIT_REQ為高)一直是968:

INIT_REQ拉低以后timer開始倒數(shù)計數(shù):

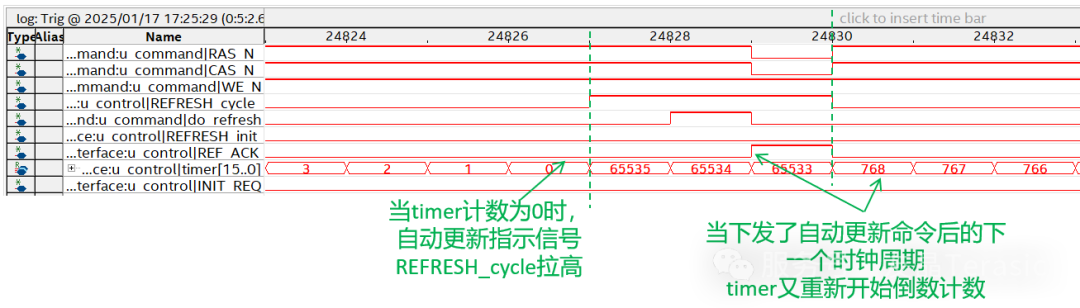

初始化操作結(jié)束后timer的計數(shù)周期就變成了768:

可能讀者疑惑這里為什么中間有三個周期timer的值是65535、65534、65533,而不是馬上變?yōu)?68呢?

其實可以結(jié)合這個圖看:

1. timer 為0;

2. timer為0 的下個時鐘周期REFRESH_cycle為1,timer值繼續(xù)減一,為65535;

3. 繼而下個時鐘周期 do_refresh 為1,timer值繼續(xù)減一,為65534;

4. 繼而下個時鐘周期 REF_ACK 為1,timer值繼續(xù)減一,為65533;

5. 繼而在下個時鐘周期的時候 timer 賦值為768。

注意本文件當(dāng)中REFRESH_init和REFRESH_cycle都是指示自動刷新操作的命令,都會控制SDRAM控制器去發(fā)送RASCASWE組合是001的命令,它們只是指示的是不同狀態(tài)下的自動刷新。

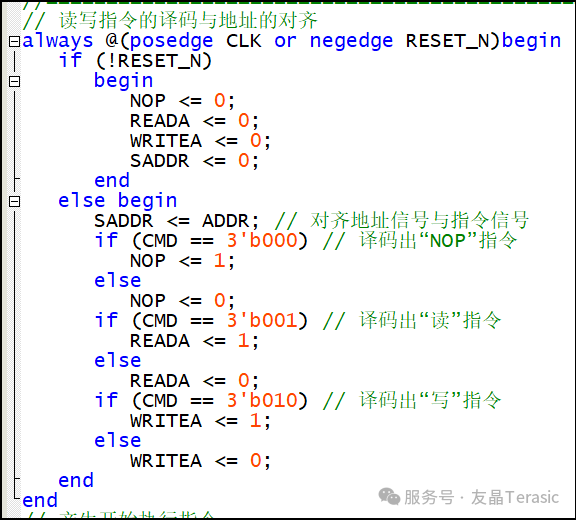

讀寫指令譯碼的代碼部分如下,當(dāng)CMD值為000時,對應(yīng)NOP指令,當(dāng)CMD值為001對應(yīng)讀指令,當(dāng)CMD值為010時對應(yīng)寫指令:

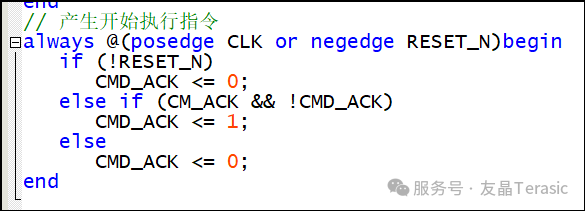

再來看CM_ACK和CMD_ACK信號。大家可能會疑惑為什么要弄CM_ACK和CMD_ACK這兩個變量呢?

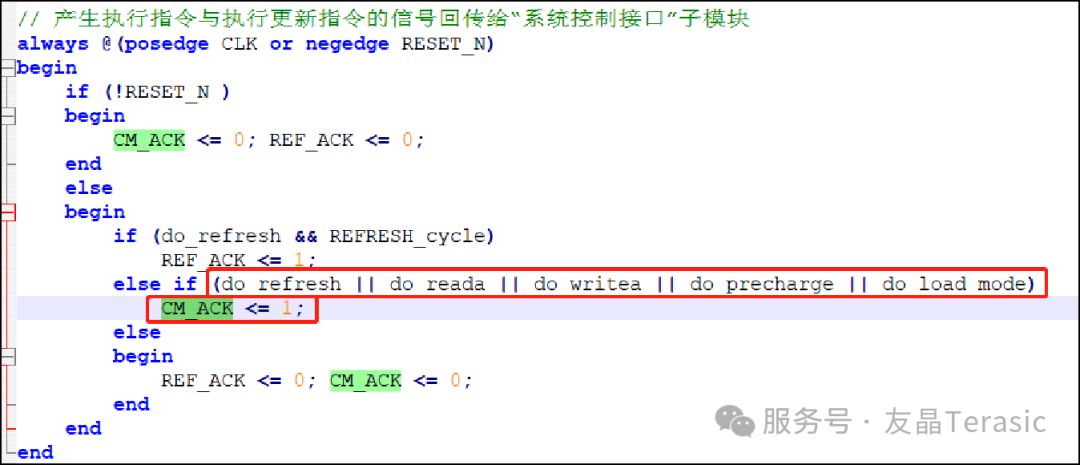

首先看輸入信號CM_ACK。由command.v文件可知當(dāng)do_refresh || do_reada || do_writea || do_precharge || do_load_mode有效時,CM_ACK=1:

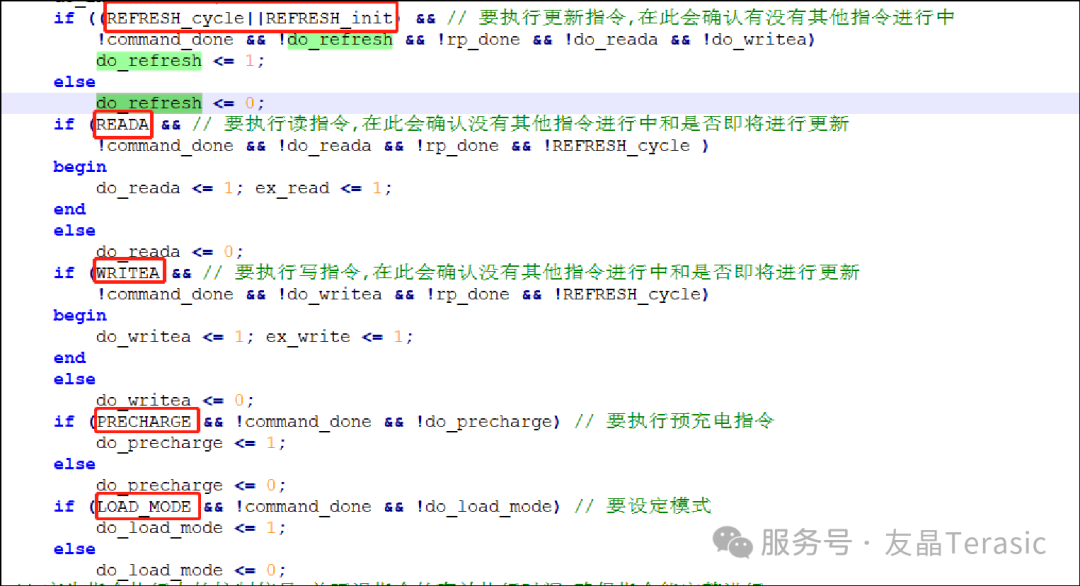

而只有接收到WRITEA、READA、PRECHARGE、LOAD_MODE等命令時do_refresh 、 do_reada 、 do_writea 、do_precharge 、 do_load_mode這些信號會拉高:

所以CM_ACK信號用于接收指令。它主要指示預(yù)充電指令、初始化狀態(tài)下的自動更新命令、加載模式寄存器指令和讀寫指令的接收。

因為接收指令不一定會執(zhí)行,CMD_ACK用于判斷接收到的指令是否執(zhí)行。所以當(dāng)CM_ACK有效(接收到了指令),CMD_ACK無效(無效說明當(dāng)前沒有別的指令在執(zhí)行)時,才令CMD_ACK有效。

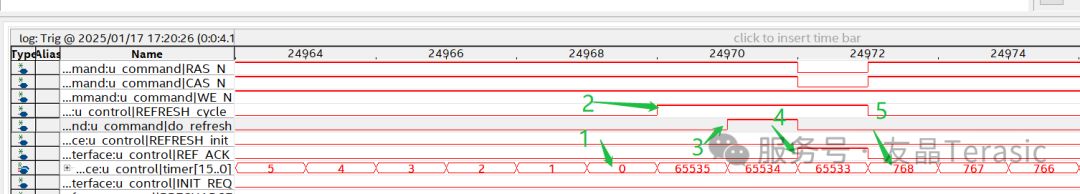

CM_ACK與CMD_ACK信號波形參考下圖:

PS:本文的波形圖來自文件~sdramcontroloutput_filesinterface.stp

-

控制器

+關(guān)注

關(guān)注

114文章

16960瀏覽量

182873 -

SDRAM

+關(guān)注

關(guān)注

7文章

441瀏覽量

56018 -

接口

+關(guān)注

關(guān)注

33文章

8933瀏覽量

153189 -

代碼

+關(guān)注

關(guān)注

30文章

4886瀏覽量

70244

原文標(biāo)題:04-SDRAM控制器的設(shè)計——control_interface.v代碼解析

文章出處:【微信號:友晶FPGA,微信公眾號:友晶FPGA】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

SDRAM控制器的設(shè)計——Sdram_Control.v代碼解析(異步FIFO讀寫模塊、讀寫SDRAM過程)

【開源騷客】《輕松設(shè)計SDRAM控制器》第八講—命令解析模塊講解

SDRAM控制器參考設(shè)計,Lattice提供的VHDL源代碼

使用Verilog實現(xiàn)基于FPGA的SDRAM控制器

SDRAM控制器簡易化設(shè)計

DDR SDRAM控制器參考設(shè)計VHDL代碼

SDRAM控制器的設(shè)計

FPGA讀寫SDRAM的實例和SDRAM的相關(guān)文章及一些SDRAM控制器設(shè)計論文

如何使用FPGA設(shè)計SDRAM控制器

基于SDRAM控制器軟核的Verilog設(shè)計

PIC32系列參考手冊之DDR SDRAM控制器

SDRAM控制器設(shè)計之command.v代碼解析

SDRAM控制器設(shè)計之control_interface.v代碼解析

SDRAM控制器設(shè)計之control_interface.v代碼解析

評論