【編者按】

IEEE國際電子器件會議 (IEDM) 是全球領先的微電子器件制造和材料技術論壇,展現最前沿的半導體和電子器件技術、設計、制造、物理材料領域的技術突破。IEDM會議議題涉及納米級CMOS晶體管技術、先進存儲、顯示、傳感、MEMS、新型量子和納米級器件、光電子、能量采集器件、高速器件以及工藝技術和設備建模和仿真等領域。

2024 IEDM會議的焦點主要有三個:邏輯器件的先進工藝技術包括TSMC N2節點、CFET技術突破、三星2D材料、英特爾硅溝道擴展技術;存儲技術包括存算一體、Meta 3D堆疊內存實現;先進封裝技術包括英特爾EMIB-T 2.5D技術和臺積電SoIC 3D混合鍵合技術。

本文編譯自SemiAnalysis對IEDM 2024會議的總結,分為三部分連載,歡迎感興趣的朋友關注和分享。

【內容目錄】

1.TSMC N2

2.CFET

3.Memory

4.Meta 3D Stacked Memory

5.Intel EMIB-T

6.TSMC SoIC

7.Nvidia System Co-Optimization Of GPUs

8.2D Materials

9.Intel 6nm Gate Length

10.Expert Panel: Breakthroughs Needed

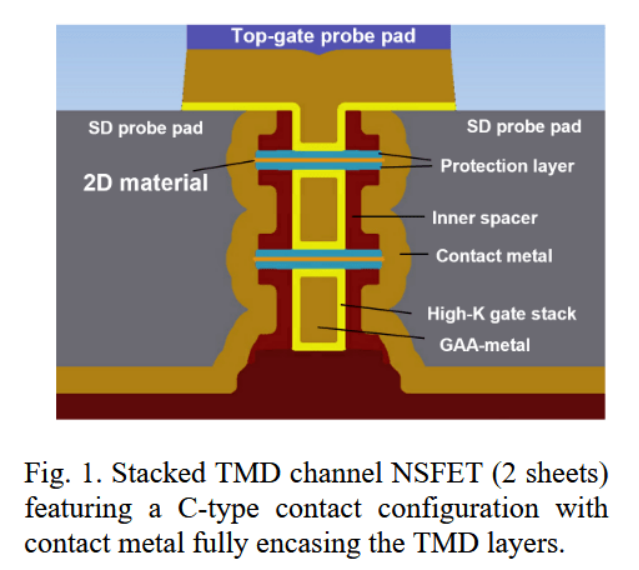

2D材料有望替代硅基晶體管溝道,溝道負責在晶體管源極和漏極之間傳導電流,其導電性由接觸或環繞溝道的柵極控制。在硅基器件中,當溝道長度(通常稱為柵極長度或Lg)縮小至約10納米以下時,由于漏電流過高會導致晶體管效率低下且難以關斷,因此被認為不具備實用價值。而2D材料構成的溝道具有更優的操控性,且不易產生硅基器件常見的漏電流機制。鑒于尖端器件的柵極長度已進入10-20納米區間,2D材料已被納入2030年代多個技術路線圖,但目前距商業化應用仍有距離。英特爾的一篇論文將主要挑戰歸納為三類:

1. 材料生長

2. 摻雜與接觸成型

3. 全環繞柵極(GAA)堆疊/高K金屬柵極集成

其中摻雜與接觸成型涉及在晶體管有源區形成源漏極的摻雜工藝,以及構建與上層金屬互連的低阻接觸。GAA堆疊則需要在2D溝道周圍沉積多層材料以形成晶體管控制柵極。繼去年實現2D溝道材料集成(N型器件采用MoS?,P型器件采用WSe?)后,在摻雜、接觸和柵極成型方面取得進展:

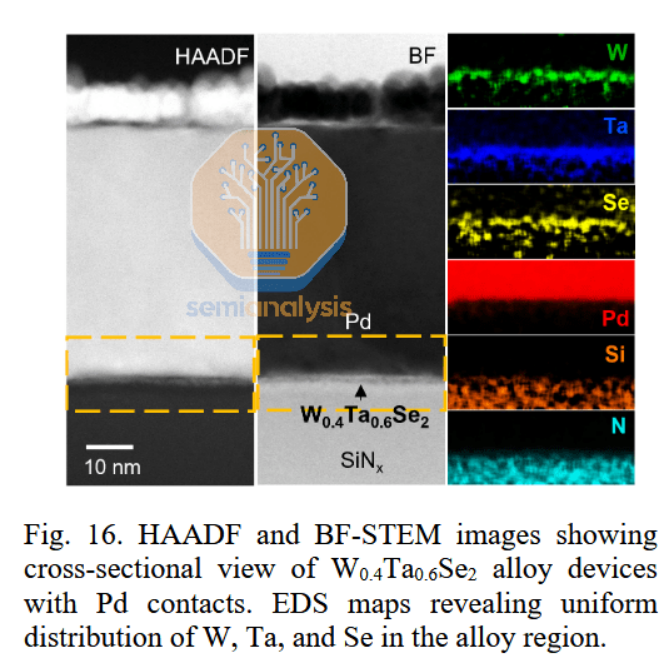

臺積電成功演示了P型器件接觸工藝,該突破填補了關鍵技術空白,此前僅有N型晶體管接觸工藝得到驗證。接觸結構負責建立金屬互連層與晶體管源極、漏極或柵極的電氣連接,其核心性能指標在于接觸電阻,這對數十納米尺度的現代器件尤為關鍵。技術難點源于源漏極由半導體材料(本例中為WSe?)構成,本征電阻較高。若直接將互連金屬沉積在源漏極表面,界面處會形成高阻態肖特基勢壘,且金屬與硅的粘附性通常較差。

硅基器件的常規解決方案是硅化工藝:通過沉積與退火在硅源漏區表面形成高導電性硅化物(如NiSi),再于硅化物上構建金屬互連,實現從有源區到電路互連的低阻連接。由于不含硅元素,傳統硅化工藝無法適用與2D材料。優選方案是采用退化摻雜——向2D材料晶格引入特定雜質,使其從半導體態轉變為導體態。但WSe?的摻雜工藝面臨嚴峻挑戰,晶格結構易遭破壞,且難以實現摻雜劑均勻分布。臺積電在大會上的展示表明,他們的研究團隊已經成功攻克了這一難題,2D材料接觸方案的突破取得了重大進展。

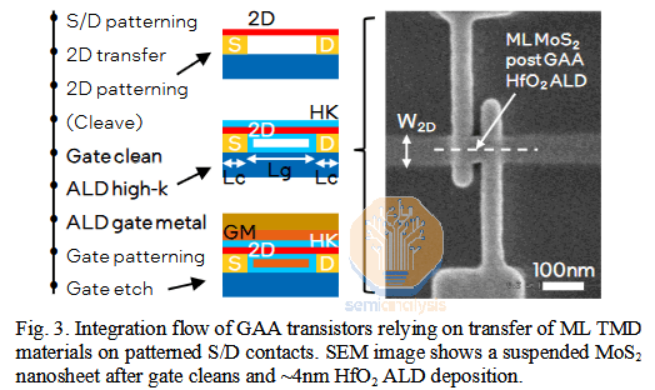

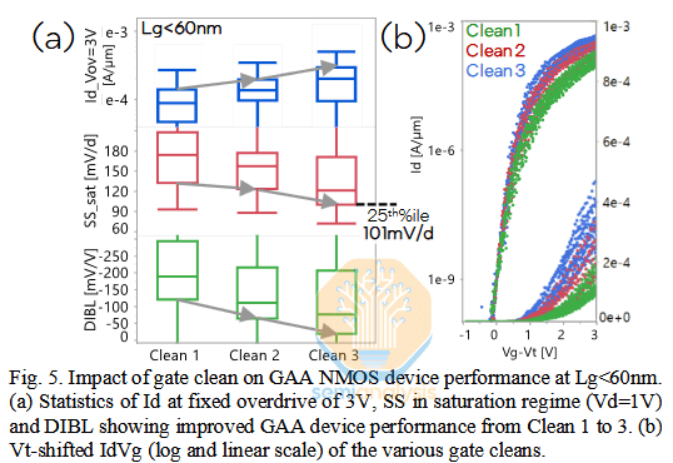

柵極氧化物質量是2D材料商業化的另一關鍵挑戰。如臺積電N2工藝論文所述,柵極氧化物質量直接決定晶體管控制能力。若無法實現有效控制,邏輯制程將失去可行性。英特爾展示了高質量柵極氧化物的制備工藝,成功制造出具有優異控制特性的晶體管器件。其DIBL(漏致勢壘降低)和亞閾值擺幅(SS)指標表現優異(分別對應低漏電流和陡峭的開關特性),同時具備高飽和漏電流,充分證明其靜電控制能力。該突破主要源于工藝優化,特別是預清洗與氧化物沉積環節的改進。

盡管在摻雜、接觸和柵極成型方面取得突破,2D材料生長技術仍進展緩慢。我們在去年綜述中指出:“生長工藝是2D材料的根本性難題。”目前多數研究采用轉移技術:先在藍寶石襯底上生長材料,再機械轉移至硅晶圓。這種實驗室手段難以滿足量產需求,直接在12英寸硅晶圓上進行外延生長才是最具商業化潛力的技術路徑。

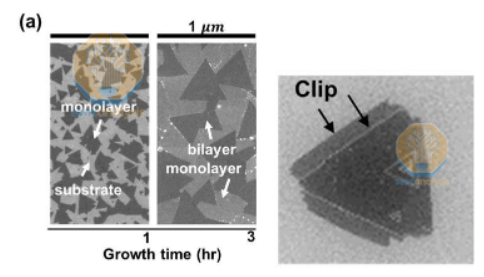

該領域最新進展陷入停滯。三星曾在8英寸測試平臺上演示晶圓級生長,但材料附著性欠佳。其解決方案是在各晶體邊緣制作“固定夾”以承受后續工藝應力,成功制備出功能性晶體管(采用頂/底柵結構而非GAA架構)。然而該工藝不具備可擴展性:演示器件的溝道長度達500納米(超出需求兩個數量級),且固定夾結構會抵消短溝道帶來的尺寸優勢。真正需要突破的是無需輔助結構即可在整片晶圓上生長高質量材料。

臺積電展示了完整二維FET反相器——將N型與P型晶體管連接構成基礎邏輯單元。該研究側重集成探索,器件采用平面結構而非GAA架構,且尺寸較需求大1-2個數量級。實驗發現若干重要現象:

首先嘗試采用WSe?制備同質N/P型晶體管。主流方案采用異質集成(NMOS使用MoS?溝道),若能用單一材料實現雙極器件將顯著降低成本。但臺積電發現WSe? NFET性能嚴重劣于PFET,無法匹配應用需求。

其次,標準濕法工藝會影響既有PFET性能。在PFET有源區進行圖形化時采用常規濕法工藝(光刻膠、蝕刻等)——這些本應對底層器件無影響的成熟工藝,卻導致閾值電壓(晶體管開啟電壓)顯著偏移。這種非直觀現象預示:隨著2D材料集成復雜度提升,可能涌現更多意外挑戰。

二維FET的閾值電壓易受標準濕法工藝影響。

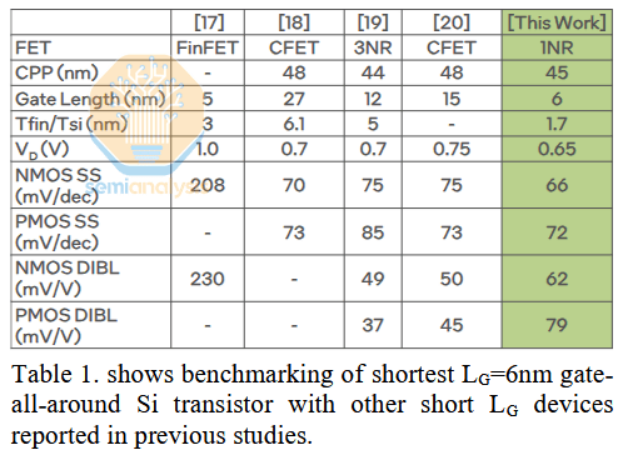

實現量產仍需長期努力。當前尖端技術僅能在較短溝道下制備單個優質晶體管,距離單晶圓集成數十億晶體管、年產能十萬片以上的目標相差約15個數量級。更糟糕的是,硅基器件理論最小柵長10納米的傳統認知已被打破。英特爾成功演示單納米帶GAA晶體管,柵長僅6納米。

傳統認為10納米以下將面臨量子隧穿等根本性障礙:在極端尺度下,載流子穿越柵極勢壘的概率不可忽略,導致漏電流激增。漏電嚴重的晶體管將造成芯片能效低下與可靠性問題。但英特爾的實驗證明量子隧穿效應可被有效抑制,雖然器件性能尚未完美,但已展現足夠優化空間——亞閾值擺幅接近室溫理論極限60 mV/dec,DIBL指標約為臺積電N2工藝的兩倍,雖需改進但已屬研發突破。

需注意:此前5納米柵長FinFET器件性能極差(DIBL與SS值過高),而本次6納米GAA器件性能顯著提升。

英特爾的突破可能延后2D材料的路線圖定位。若無技術必要性,芯片制造商不會輕易轉向復雜的新材料體系。

盡管計算設備持續進步,但現有發展模式不可持續。若無底層器件革新,計算需求與能耗的指數增長將難以為繼。斯坦福大學Tom Lee教授推演顯示:按當前增速,2050年AI計算能耗將超過地球接收的太陽光子總量,百年后更需捕獲太陽全部輻射能量——這凸顯技術變革的緊迫性。IEDM專家小組強調:半導體器件需要革命性突破,而非寄望于戴森球等科幻方案。論壇閉幕時,學界發出行動倡議:器件技術的漸進式改良已不足夠。Lee教授指出,在各類“AI指數”中,能源終將成為關鍵制約因素。“我們無法用線性武器戰勝指數級敵人。”

-

工藝

+關注

關注

4文章

669瀏覽量

29248 -

2D

+關注

關注

0文章

67瀏覽量

15437

原文標題:IEDM 2024先進工藝焦點(三):2D材料技術的進展與挑戰

文章出處:【微信號:深圳市賽姆烯金科技有限公司,微信公眾號:深圳市賽姆烯金科技有限公司】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

HT 可視化監控頁面的 2D 與 3D 連線效果

TechWiz LCD 2D應用:半透反射式顯示模式仿真

億源通科技OFC 2025展示2D光纖陣列,助力OCS技術創新

STM8/STM32 products有2D marking和沒有2D marking的工藝有差別嗎?

先進制程面臨哪些挑戰

英特爾代工在IEDM 2024展示多項技術突破

英特爾IEDM 2024大曬封裝、晶體管、互連等領域技術突破

IEDM 2024先進工藝探討(三):2D材料技術的進展及所遇挑戰

IEDM 2024先進工藝探討(三):2D材料技術的進展及所遇挑戰

評論