摘要

我們介紹了一種具有高增益(>40dB)和高飽和功率(>21 dBm)的半導體光學放大器(SOA)芯片,其驅動電流適中(1.3A)。本文提出了一個用于優化新型雙段SOA概念的設計模型。該模型的預測結果與制造的芯片上的測量結果非常一致。以增益和飽和輸出功率乘積作為性能指標,它展示了迄今為止最佳報道。然而,由于噪聲系數略有下降,我們引入了一種先進的設計,使得能夠優化噪聲系數。

I. 引言

為了滿足光通信系統對更大容量的日益增長的需求,城域網和長途網系統正在考慮將光帶寬擴展到L波段和S波段。因此,半導體光放大器(SOA)非常具有吸引力,因為它們可以被設計成在不同的帶寬下工作,并具有可變的增益。此外,與摻鉺光纖放大器(EDFA)相比,SOA的封裝尺寸更小,并且可以以相對較低的成本提供更低的功耗。然而,在波分復用(WDM)長途系統的在線放大中,需要較高的輸出功率水平。因此,需要SOA具有較高的飽和功率水平,以避免增益飽和狀態下出現的信噪比降低。到目前為止,所報道的基于磷化銦(InP)的設計雖然具有較大的輸出功率(>20dBm),但卻以犧牲增益(

為了緩解單一SOA結構中的權衡問題,文獻[9],[10]提出了一種具有可變限制因子的SOA。然而,目前尚未報道實驗結果和理論驗證。最近,我們介紹了一種由兩個部分組成的新型SOA設計,旨在以適中的偏置電流滿足大增益(>35 dB)和高飽和輸出功率要求(>22 dBm)。這是通過優化一個部分以滿足高增益要求,而另一個部分滿足高飽和輸出功率要求來實現的。特別是,通過在芯片的一部分上引入上包層錐度來獲得大增益。然而,這導致噪聲系數略有下降。

本文首先揭示了基于增益和飽和輸出功率關鍵因素的SOA設計和優化的模型。接下來,我們通過測量制造芯片的性能指標(增益、噪聲系數和飽和功率),并將其與最先進的SOA進行比較,來展示該模型的驗證結果。最后,我們介紹了一種先進的SOA設計,該設計實現了更小的噪聲系數,同時不影響大增益和高飽和輸出功率水平。

II. 雙段SOA設計與模型

A. 緩解增益與飽和輸出功率之間的權衡

如已報道所示,增益與飽和輸出功率之間的權衡是由于它們隨光學限制因子(Г)的變化趨勢相反所導致的。實際上,如近似方程(1)和(2)所述,SOA的小信號增益(G0)隨限制因子的增加而指數增長,而飽和光功率(Psat)——即放大器增益為其小信號增益G0一半時的輸出光功率——與限制因子成反比:

其中(Г)表示有源區域的光學限制,(gmat)表示材料增益,(α)表示每厘米的傳播損耗,(L)表示芯片長度;這里忽略了傳播損耗、空間燒孔效應和放大的自發輻射。

其中,(A)表示有源區域的橫截面積,(a1)表示材料的微分增益,(τc)表示與非受激復合相關的載流子壽命。

因此,通過在單個芯片上結合兩個區域——一個具有大限制因子,另一個具有小限制因子——可以同時實現大增益和高飽和輸出功率,而只需適中的偏置電流和芯片長度。

然而,為了根據方程(2)和最后一個區域的參數預測放大器的飽和輸出功率,必須仔細選擇這兩個區域的長度。

請注意,飽和輸出功率還與微分增益a1成反比(見方程(2))。因此,通過減小SOA的體積,也可以實現更高的飽和輸出功率。

B. 雙區SOA設計描述

該SOA(半導體光放大器)設計基于InP材料,并在有源區域采用了InGaAsP多量子阱(MQW)結構。它包含了5個厚度均勻的量子阱,每個量子阱的厚度為11nm。

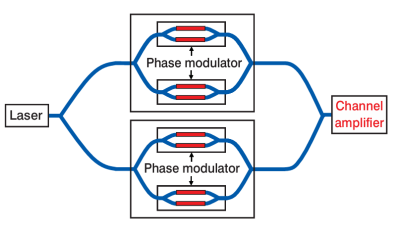

為了將增益帶寬覆蓋到C波段和L波段(1525-1625nm),光致發光峰值波長被設定在1640nm。SOA被優化為使用橫向電場(TE)極化信號進行操作,因為通過采用極化分集方案的SOA模塊封裝可以實現極化不敏感性。該方案涉及使用兩個單極化SOA,它們以并行架構排列,每個SOA負責處理一種光極化。此外,這種模塊方案還能使Psat(飽和輸出功率)提高3dB。

我們的雙區SOA由一個旨在通過在有源區域實現大光學限制來獲得足夠增益的區段,以及另一個旨在通過低光學限制來獲得大Psat的區段組成。

通過在有源層和SOA堆疊的n型摻雜InP之間插入一個厚的下包層或平板層,可以實現具有大Psat的區段的小光學限制。實際上,當下包層的折射率大于n型摻雜InP的折射率時,光學模式會從有源區域被拉下,導致量子阱中的光學限制因子變小。

此后,該區段被稱為標準區段或STD區段。同樣地,僅包含標準區段的SOA被稱為STD SOA。

而通過在有源層和SOA堆疊的p型摻雜InP之間插入一個額外的上包層(UC)層,可以實現具有大增益的區段的大光學限制。當上包層的折射率大于p型摻雜InP層的折射率時,光學模式會被拉上,并且來自平板的牽引力因此減小,從而在量子阱中產生大的限制因子。

此后,該區段被稱為UC(上包層)區段。

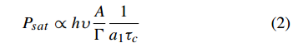

SOA的制造過程包括在InP襯底上外延生長下包層(n型摻雜)的InGaAsP平板、有源區域(InGaAsP多量子阱)和p型摻雜的上包層。然后,對于UC區段和標準(STD)區段,上包層被選擇性蝕刻。在兩個區段之間,上包層被部分蝕刻以在器件的兩個區段之間的界面上形成錐度,如圖2所示。波導以相對于解理方向7°的傾斜角度蝕刻到平板中,以減少光反饋。之后,在波導的側面外延再生長一層InP絕緣層,然后再生長一層p型摻雜層。這被稱為半絕緣掩埋異質結構(SIBH)工藝,它通過將波導掩埋在絕緣且導熱的材料中來實現良好的散熱和圓形模式。

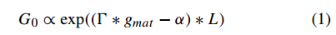

對于大增益(>25dB),應大幅減少耦合的向后光反射,以避免產生大于0.2dB的較大紋波,這種紋波會導致信號失真。因此,應實現低輸出端面反射率。這取決于抗反射(AR)涂層的質量以及波導設計——傾斜角度和寬度。

因此,對于7°傾斜的波導和典型的AR涂層系數4×10-3處的直徑)的變化,以確定STD區段的條紋寬度。結果如圖1所示。對于FWHM發散小于20°(光模式半徑大于4μm)的情況,在高達40dB的增益下,紋波小于0.2dB。考慮到制造公差,輸出STD區段的條紋寬度設置為5μm,導致Г約為3.1%。

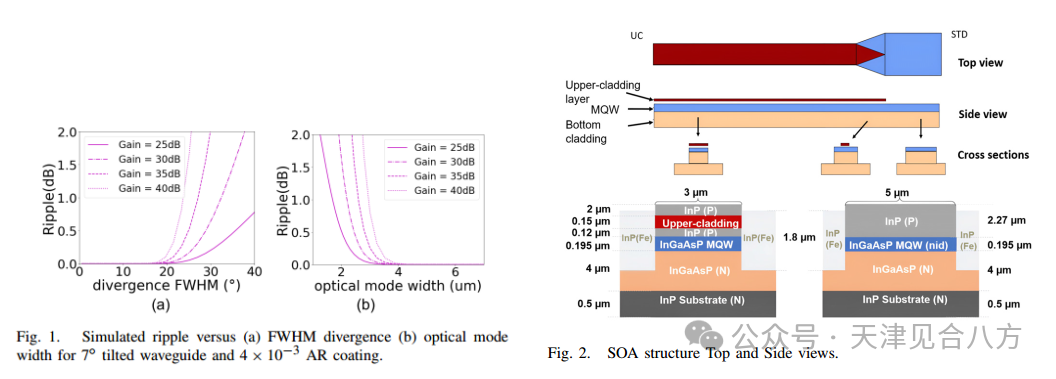

此外,為了確保基模在UC區段波導中傳播,UC區段的條紋寬度被設定為3μm,這略小于STD區段的條紋寬度,導致Г約為5.4%。因此,設計了一個錐度,以確保兩個區段之間的模式傳播能夠平滑且無損地過渡。SOA的俯視圖、側視圖以及橫截面圖如圖2所示。這三個橫截面分別對應UC區段、過渡錐度和STD區段。UC區段和STD區段的模擬光模式分別如圖3(a)和(b)所示。

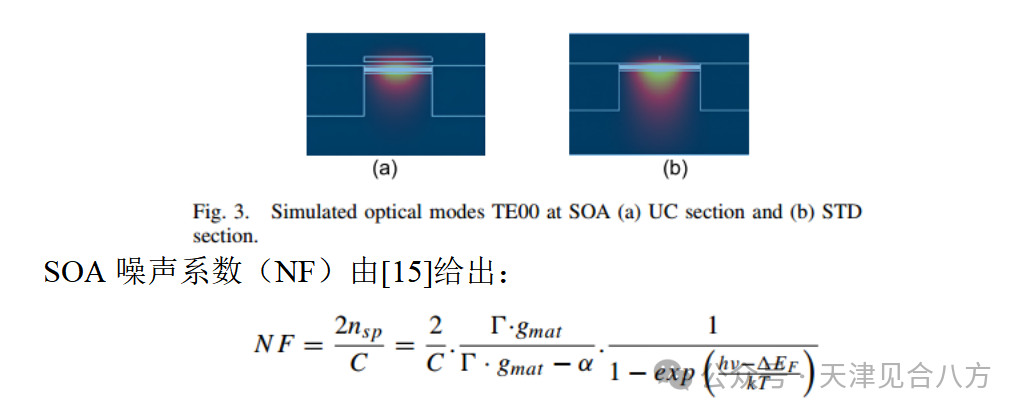

利用這個公式,我們可以比較UC-SOA(超緊湊半導體光放大器)和STD-SOA(標準半導體光放大器)的噪聲系數(NF)。第一項取決于耦合效率C。通過測量,我們發現UC-SOA和STD-SOA的耦合效率相似,分別為85%和80%。第二項被稱為損耗項,它取決于波長和載流子密度。盡管UC區段和STD區段的限制因子和傳播損耗不同,但它們的值幾乎總是以大致相同的比例變化。根據我們的計算,在整個C波段和L波段波長范圍內,它們之間的差異不超過0.1dB。最后一項是反轉因子項,與波長和ΔEF(準費米能級差)有關。ΔEF受載流子密度影響,對應于吸收和受激輻射概率相同的能量。由于UC區段和STD區段的有源材料結構相同,因此它們的反轉因子項也相同。因此,UC-SOA的噪聲系數應與STD-SOA的噪聲系數相似。

為了實現大增益和高飽和輸出功率(Psat),應妥善確定每個區段的長度,以確保大增益區段(UC區段)中的光功率始終低于其飽和水平。

實際上,光功率應僅在SOA的STD區段輸出附近接近飽和輸出功率。只有這樣,才能通過公式(2)以及輸出區段的A和Г參數正確推導出芯片的飽和輸出功率(Psat)。否則,如果UC區段過長,飽和輸出功率將會降低。因此,為了獲得STD區段和UC區段的最優長度分配,我們建立了一個簡單的模型來模擬增益和飽和輸出功率性能。

C. 雙區段SOA模型

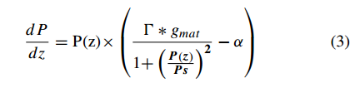

假設SOA中的載流子密度是均勻的,且載流子壽命是一個恒定值,那么在給定載流子密度下,SOA中傳播的光功率可以通過考慮長度為dz的小傳播步長來計算,如下所示:

其中,(Г)表示有源區域中的光限制因子,(gmat)表示材料增益,(α)表示每厘米的傳播損耗,(Ps)表示增益介質的飽和功率。

通過求解方程(3),可以計算出每個區段輸出處的傳播功率以及芯片增益,從而優化各個區段的長度。

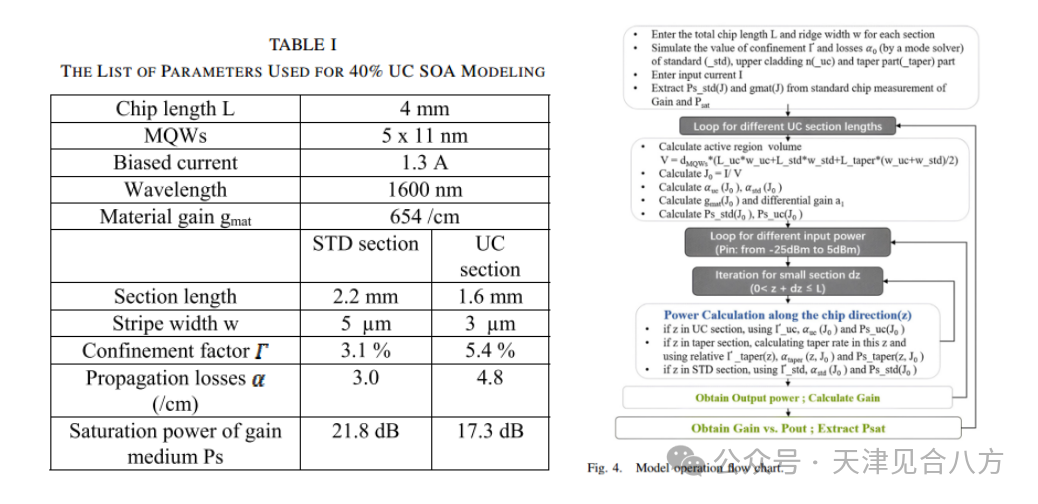

因此,方程(3)的參數是從光學模式求解器和具有相同多量子阱(MQW)設計芯片的測量中提取的。例如,使用模式求解器計算了MQW和包層中的光限制因子,從而可以推導出n型和p型摻雜區域的光損耗,而材料增益隨載流子密度的變化以及增益介質的飽和功率則是分別使用方程(1)和(2)從現有SOA STD芯片的增益和飽和輸出功率測量中提取的。然后,對方程(3)在UC區段、錐度區段和STD區段進行了數值求解,從而提取了芯片增益。此外,通過使用循環函數并掃描從-25 dBm到5 dBm的輸入功率,計算了器件的飽和輸出功率。流程圖如圖4所示。

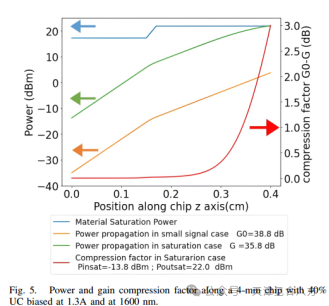

芯片長度確定為4毫米,以便為STD SOA提供適中的增益。在圖5中,展示了在1.3 A偏置電流下,對于不同輸入1600 nm信號功率的情況,一個4毫米長芯片上沿其長度的光功率值,其中40%的長度由UC區段組成。所使用的參數列在表I中。1.3 A電流是我們在測量中通常能夠達到的最大電流,并確保沒有過載操作。光從UC區段傳播到芯片的STD區段。

在圖5中,對應于小信號情況(橙色曲線)的曲線,輸入功率被設置為-35 dBm。而對于對應于飽和情況(綠色曲線)的曲線,輸入功率被調整到與輸入飽和功率(-13.8 dBm)相匹配。這兩條曲線的差值就得到了增益壓縮因子,該因子繪制在次垂直軸上(紅色曲線)。它顯示了增益飽和在芯片上的哪個位置發生。特別是,對于這種雙區段設計,飽和發生在SOA STD區段的輸出處。此外,還展示了每個區段以及整個芯片的材料飽和功率(藍色曲線)。

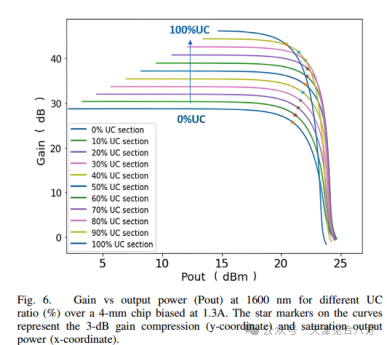

因此,我們進一步研究了UC比例(即UC區段長度與總長度(UC + STD)的比例)的影響。在圖6中,展示了在1.3A偏置電流和1600nm輸入信號下,4mm芯片上芯片增益隨UC區段比例和輸出功率的變化情況。UC區段比例以10%的步長從0%變化到100%。特別地,在0% UC的情況下,SOA僅由STD區段組成;而在100% UC的情況下,SOA則僅由UC區段組成。每條曲線上星號標記對應的橫坐標表示每個UC比例下的芯片飽和功率Psat。隨著UC比例的增加,增益總是增加,這是UC區段中更大的光限制因子的直接結果。然而,飽和輸出功率首先隨著UC比例的增加而增加,直到60%,然后減少。其最初增加的原因是由于UC區段的波導比STD區段更窄,導致有源體積減小。實際上,這導致在相同偏置電流下電流密度增加,進而降低了微分增益a1(見方程(3))。然而,當UC區段過長(在此情況下超過60%)時,飽和功率會下降,因為光信號會在到達芯片輸出之前先在UC區段中飽和。

因此,對于這個4mm長的雙區段SOA設計,UC區段的最優長度比例約為60%。

為了驗證這個模型,我們制造了具有相同多量子阱(MQW)結構但UC區段比例不同的芯片,并隨后對它們進行了適當的表征。

--未完待續--

注:本文由天津見合八方光電科技有限公司挑選并翻譯,旨在推廣和分享相關半導體光放大器如1550nm、1310nm等全波段SOA基礎知識,助力SOA技術的發展和應用。特此告知,本文系經過人工翻譯而成,雖本公司盡最大努力保證翻譯準確性,但不排除存在誤差、遺漏或語義解讀導致的不完全準確性,建議讀者閱讀原文或對照閱讀,也歡迎指出錯誤,共同進步。

天津見合八方光電科技有限公司,是一家專注半導體光放大器SOA研發和生產的高科技企業,目前已推出多款半導體光放大器SOA產品(1060nm, 1310nm, 1550nm),公司已建立了萬級超凈間實驗室,擁有較為全面的光芯片的生產加工、測試和封裝設備,并具有光芯片的混合集成微封裝能力。目前公司正在進行小型SOA器件、DFB+SOA的混合集成器件、可見光波長SOA器件、大功率SOA器件的研發工作,并可對外承接各種光電器件測試、封裝和加工服務。

-

放大器

+關注

關注

145文章

14104瀏覽量

216308 -

半導體

+關注

關注

335文章

28625瀏覽量

232871 -

SOA

+關注

關注

1文章

300瀏覽量

28035

原文標題:具有大增益、小噪聲、高飽和輸出功率的新型SOA設計(一)

文章出處:【微信號:天津見合八方,微信公眾號:天津見合八方】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

一種新型Doherty功率放大器的仿真設計

半導體光放大器SOA技術及應用簡介

半導體光放大器的工作原理_半導體光放大器的優缺點

soa光放大器原理 soa光放大器增益測試

SOA半導體光放大器原理 SOA半導體光放大器的缺點

soa半導體光放大器原理 soa半導體光放大器可以當光開關嗎

一文帶你看懂什么是SOA半導體光放大器?半導體光放大器的分類及應用 SOA半導體光放大器介紹

一種新型半導體光放大器設計(1)

一種新型半導體光放大器設計(1)

評論