提高電磁干擾(EMI)抗擾性對于確保電子設(shè)備的穩(wěn)定性和可靠性至關(guān)重要。以下是一些提高電磁干擾抗擾性的方法:

一、設(shè)計(jì)層面的優(yōu)化

- 合理的電路板布局 :

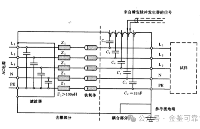

- 在PCB設(shè)計(jì)中,將敏感電路與產(chǎn)生強(qiáng)電磁場的元件合理布局,減小它們之間的耦合。

- 遵循最小回路面積原則,以減少電磁耦合。

- 接地設(shè)計(jì) :

- 設(shè)計(jì)良好的接地系統(tǒng),為各個(gè)部件提供一個(gè)零電位參考點(diǎn)。

- 增大接地面積,并合理分布接地點(diǎn),以降低接地阻抗。

- 在多層板布線設(shè)計(jì)時(shí),可將其中一層作為“全地平面”,以起到屏蔽作用。

- 濾波設(shè)計(jì) :

- 屏蔽措施 :

- 使用金屬屏蔽層、屏蔽殼體等將設(shè)備或關(guān)鍵部件包裹起來,以阻隔外部電磁波的干擾。

- 對于高頻信號,必須使用屏蔽電纜,其正面和背面均接地,以消除EMI干擾。

二、元器件的選擇與配置

- 選用低輻射元器件 :

- 選擇具有低輻射特性的元器件,以減少電磁干擾的產(chǎn)生。

- 配置抑噪技術(shù) :

- 使用吸收材料 :

- 在某些場合下,可以采用吸波材料吸收不必要的電磁能量。

三、系統(tǒng)層面的優(yōu)化

- 頻譜管理 :

- 在無線通信系統(tǒng)中,通過合理的頻譜規(guī)劃和管理,避免不同系統(tǒng)之間的頻譜干擾。

- 電磁兼容性測試 :

- 在產(chǎn)品研發(fā)的早期階段進(jìn)行電磁兼容性測試,及時(shí)發(fā)現(xiàn)并解決潛在的電磁干擾問題。

- 瞬時(shí)過壓/過流保護(hù) :

- 安裝瞬時(shí)過壓或過流保護(hù)裝置,防止過壓或過流傳遞到敏感電路,造成干擾或損壞。

四、其他措施

- 優(yōu)化電纜布線 :

- 確保電纜布線合理,減小電纜之間的交叉干擾。

- 使用高質(zhì)量的線纜,并定期檢查和維護(hù),以確保線路的正常工作。

- 減小環(huán)路面積 :

- 每個(gè)環(huán)路都相當(dāng)于一個(gè)天線,因此應(yīng)盡量減小環(huán)路的數(shù)量和面積,以降低天線效應(yīng)。

- 避免直角走線 :

- 直角走線會產(chǎn)生輻射,應(yīng)避免走線、過孔及其它元器件形成90°角。走線應(yīng)至少以兩個(gè)45°角布線到拐角處。

綜上所述,提高電磁干擾抗擾性需要從設(shè)計(jì)層面、元器件選擇、系統(tǒng)層面以及其他多個(gè)方面綜合考慮。通過采取這些措施,可以有效地降低電磁干擾對電子設(shè)備的影響,提高設(shè)備的穩(wěn)定性和可靠性。

聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點(diǎn)僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請聯(lián)系本站處理。

舉報(bào)投訴

-

電子設(shè)備

+關(guān)注

關(guān)注

2文章

2871瀏覽量

54521 -

元件

+關(guān)注

關(guān)注

4文章

1071瀏覽量

37450 -

電磁干擾

+關(guān)注

關(guān)注

36文章

2379瀏覽量

106299 -

電磁場

+關(guān)注

關(guān)注

0文章

797瀏覽量

47866

發(fā)布評論請先 登錄

相關(guān)推薦

熱點(diǎn)推薦

EMI(干擾)和EMS(抗擾)基礎(chǔ)知識與整改流程

)、RS(輻射抗干擾)、Surge(雷擊)、PMS(磁場抗擾)。即:EMC(電磁兼容性)是指兼?zhèn)銭MI和EMS兩方面的性能。EMI(電磁

發(fā)表于 03-28 13:28

解析電壓暫降和短時(shí)中斷抗擾度試驗(yàn)

電壓暫降和短時(shí)中斷抗擾度試驗(yàn)電壓暫降和短時(shí)中斷抗擾度試驗(yàn)(VoltageDipsandShortInterruptionImmunityTest)是用于評估電子設(shè)備或系統(tǒng)對電力系統(tǒng)中電

電磁干擾的防護(hù)技術(shù) EMI電磁干擾對通信設(shè)備的影響

設(shè)備或關(guān)鍵部件,以減少外部電磁場的影響。 屏蔽材料的選擇應(yīng)基于其導(dǎo)電性、導(dǎo)磁性和機(jī)械強(qiáng)度等因素。 濾波技術(shù) : 安裝濾波器來過濾掉特定頻率的電磁干擾信號,保護(hù)設(shè)備免受影響。 濾波器可以

案例:小電容解決困擾多時(shí)的輻射抗擾度問題

【現(xiàn)象描述】某醫(yī)療產(chǎn)品,用來接收植人人體內(nèi)部輔助器官向外發(fā)送的信號,來監(jiān)控被植入的人造輔助器官工作狀態(tài)及相應(yīng)測試數(shù)據(jù)。因?yàn)樾盘柾ㄟ^電磁場無線傳輸,所以輻射抗擾度測試是必不可少的項(xiàng)目,測試等級要求為

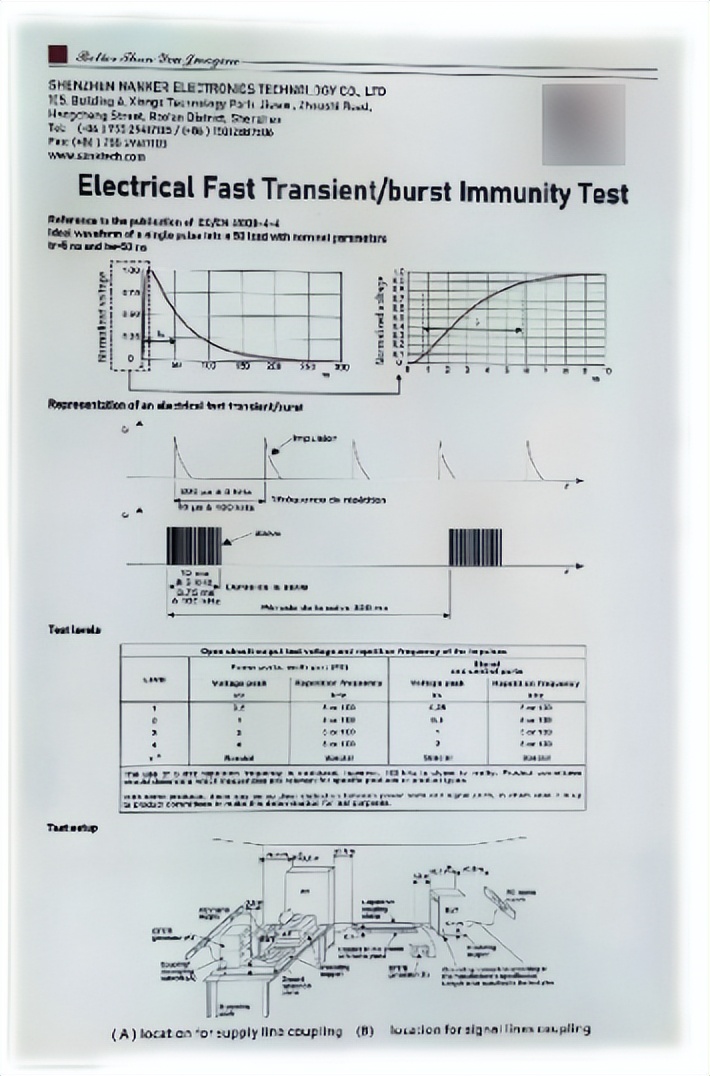

電磁兼容測試:電快速瞬變脈沖群的抗擾度評估

電快速瞬變脈沖群抗擾度測試電快速瞬變脈沖群抗擾度測試,遵循國家標(biāo)準(zhǔn)GB/T17626.4,等同于國際標(biāo)準(zhǔn)IEC61000-4-4,是一種專門用來評估電氣和電子設(shè)備在面對電路中機(jī)械開關(guān)切

GB/T 17626.5-2019電磁兼容試驗(yàn)和測量技術(shù)浪涌(沖擊)抗擾度試驗(yàn)

電子發(fā)燒友網(wǎng)站提供《GB/T 17626.5-2019電磁兼容試驗(yàn)和測量技術(shù)浪涌(沖擊)抗擾度試驗(yàn).pdf》資料免費(fèi)下載

發(fā)表于 10-21 11:05

?74次下載

TAS5630 SE模式時(shí),IC如何提高擾干擾能力?

,C23至0.1uF,問題同樣存在。

C與D之間互相干擾。

當(dāng)A+B輸入100HZ ,隨著輸出幅度增大,C,D會有干擾輸出,輸出頻率隨A+B幅度增大而增大。

當(dāng)將PCB改成2*BTL模式時(shí) ,CMRR提高,性能良好

請問

發(fā)表于 09-25 08:28

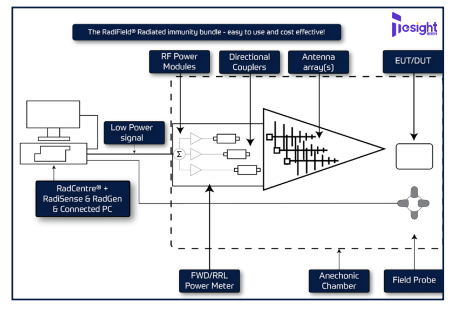

EMC RI/CI測試方案助力對抗電磁設(shè)備干擾!

一、方案背景 電磁或射頻干擾的敏感性,會給工程師帶來重大的風(fēng)險(xiǎn)和安全隱患。尤其是在工業(yè)、船用和醫(yī)療設(shè)備環(huán)境。這些環(huán)境系統(tǒng)中的控制、導(dǎo)航、監(jiān)控、通信和警報(bào)等關(guān)鍵零部件必須具備電磁抗

如何提高電磁干擾抗擾性

如何提高電磁干擾抗擾性

評論