隨著FPGA技術的發(fā)展,數字通信技術與FPGA的結合體現了現代數字通信系統(tǒng)發(fā)展的一個趨勢。為了使高速通信系統(tǒng)更加緊湊、成本更低、減小功耗,特別是提高設備的可靠性,可采用Q P S K數字調制技術來實現,其具有頻譜利用率高、頻譜特性好、抗干擾性能強、傳輸速率快等特點。運用verilog編寫在QPSK調制解調代碼以及ISE自帶的IP CORE在Xilinx公司的FPGA平臺上測試,結果表明系統(tǒng)可完全實現調制解調功能,并具有集成度高和可軟件升級等優(yōu)點。

四相絕對移相鍵控(QPSK)技術以其抗干擾性能強、誤碼性能好、頻譜利用率高等優(yōu)點,廣泛應用于數字通信系統(tǒng)。隨著超大規(guī)模集成電路的出現,FPGA在數字通信系統(tǒng)中的應用日益廣泛,目前已提出了多種基于FPGA實現QPSK的方法。本文基于FPGA實現直接數字頻率合成(DDS),通過對DDS信號(載波信號)輸出相位的控制實現調相,除DA轉換外,其它過程均可以FPGA實現。QPSK調制信號是抑制載波的信號,無法用常規(guī)的鎖相環(huán)或窄帶濾波器直接提取參考載波,但它又不同于一些連續(xù)相位調制信號,其載波相位變化只能取有限的幾個離散值,這就隱含了參考載波的相位信息。所以,可以通過非線性處理,消除信號中的調制信息,產生與原載波相位有一定關系的分量,然后再提純該信號,恢復已被抑制的載波信號,進而完成信號的相干解調。本文所設計的QPSK調制解調器由于具有較好的頻帶利用率,具有體積小、功耗低、集成度高、軟件可移植性強、擾干擾能力強的特點,符合未來通信技術設計的方向。

1.QPSK調制的基本原理

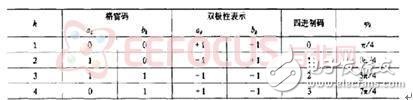

四相絕對移相鍵控QPSK是MPSK的一種特殊情況,它利用載波的四種不同相位來表征數字信息。由于每一種載波相位代表兩個比特信息,故每個四進制碼元又被稱為雙比特碼元。我們把組成雙比特碼元的前一信息比特用a表示,后一比特信息用b表示。雙比特碼元中兩個信息比特ab通常是按格雷碼(即反射碼)排列的,當ab為00時,載波相位為0°,當ab為01時,載波相位為90°,當ab為11時,載波相位為180°,當ab為10時,載波相位為270°。

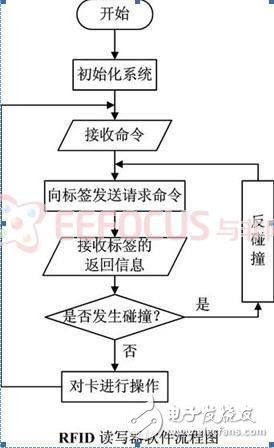

QPSK信號的產生分為調相法和相位選擇法。由于調相法比較常用,且實際操作性更強,故在本文中,選擇調相法。用調相法產生QPSK信號的組成方框圖如圖1所示。圖中,串/并變換器將輸入的二進制序列依次分為兩個并行的雙極性序列。設兩個序列中的二進制數字分別為a和b,每一對ab稱為一個雙比特碼元。雙極性的a和b脈沖通過兩個平衡調制器分別對同相載波及正交載波進行二相調制。將ab兩路輸出疊加,得到四相移相信號,其相位編碼邏輯關系為:當雙比特碼元ab為11時,輸出相位為315°的載波;ab為01時,輸出相位為225°的載波;ab為00時,輸出相位為135°的載波;ab為10時,輸出相位為45°的載波,相應的對照關系如下表所示。

數據與相位的對照關系

傳統(tǒng)的QPSK模擬調制器結構,一般采用正交調制方法。全數字調制器的實現仍采用正交調制方法,只是將模擬處理單元采用數字信號處理的算法實。QPSK采用四種不同的載波相位來表示數字信息,每個載波相位代表2比特信息,其實現有兩種方法,相位選擇法與正交調制法,相位選擇法又分為A、B兩種方式。本文采用相位選擇法B方式來實現QPSK信號,如圖1所示。

圖1 QPSK調制框圖

QPSK調制的MATLAB仿真相關的代碼網上有很多,本文作者自己編寫了一段代碼,可以簡單的表示調制的原理,在此僅將代碼羅列如下,相的注釋已經很清楚,不再贅述。代碼要綜合解調部分一起研讀。

clear all;

clc

M=4;

Ts=1;

fc=5;

N_sample=8;%每個正弦波采樣點數

N_num=300;%I Q路分別100個bit

dt=1/fc/N_sample;

t=0:dt:N_num*Ts-dt;

T=dt*length(t);

Noise=(1/500)*randn(1,length(t))*32767;%加入噪聲

py1f=zeros(1,length(t));

py2f=zeros(1,length(t));

for PL=1:1:700%加入噪聲強度加大

d1=sign(randn(1,N_num));

d2=sign(randn(1,N_num));

d=[d1;d2];

D=reshape(d,1,[]);%D是輸入的信息序列

gt=ones(1,fc*N_sample);

s1=sigexpand(d1,fc*N_sample);%此為符號位擴展函數,相關函數在原代碼中可見

s2=sigexpand(d2,fc*N_sample);

b1=conv(s1,gt);

b2=conv(s2,gt);

s1=b1(1:length(s1));

s2=b2(1:length(s2));

st_qpsk_1=s1.*round(cos(2*pi*fc*t)*32767);

st_qpsk_2=s2.*round(sin(2*pi*fc*t)*32767);

st_qpsk=st_qpsk_1+st_qpsk_2;%定點量化后的數據

%-----------------------------------------------------------

% 發(fā)射信號的功率譜

%plot((abs(fft(st_qpsk,2048))).^2);

-

FPGA

+關注

關注

1643文章

21968瀏覽量

614298 -

QPSK

+關注

關注

2文章

63瀏覽量

26956

發(fā)布評論請先 登錄

基于VHDL方式實現了QPSK數字調制解調電路的設計

基于FPGA 的QPSK 調制解調電路設計與實現Design

基于F PGA的QPS K調制解調電路設計與實現

基于FPGA的QPSK解調器的設計與實現

QPSK高性能數字調制器的FPGA實現

基于VHDL的QPSK調制解調系統(tǒng)設計與仿真

基于QPSK數字調制解調的FPGA實現

基于QPSK數字調制解調的FPGA實現

評論