2016年7月正式發(fā)布的2015年國際半導體技術(shù)路線圖(ITRS)做出預測,經(jīng)歷了50多年的微型化,晶體管的尺寸可能將在5年后停止縮減。

該報告預測,2021年之后,對各公司來說,繼續(xù)縮小微處理器中的晶體管將不再是一種經(jīng)濟的做法。芯片制造商們將轉(zhuǎn)而采用其他方式提高晶體管密度,即將晶體管布置結(jié)構(gòu)從水平變成垂直,建立層層相疊的多層電路。

一些人認為,這種變化可能再一次給摩爾定律敲響了喪鐘;晶體管密度曾經(jīng)遵循摩爾定律而不斷翻倍,我們才有了今天這種極其強大的計算機。雪上加霜的是,這是最后一份ITRS路線圖。這項協(xié)調(diào)規(guī)劃于1993年始于美國,然后擴展到了世界其他地區(qū),現(xiàn)在走到了終點。

半導體行業(yè)協(xié)會(Semiconductor Industry Association)是一家位于華盛頓特區(qū),代表IBM、英特爾及其他公司利益的美國貿(mào)易團體,也是ITRS的主要贊助商。該協(xié)會表示,在行業(yè)參與度下降、企業(yè)參與其他計劃的興趣增強的情況下,它將發(fā)揮自己的作用,與另一家行業(yè)組織——半導體研究公司(SemiconductorResearch Corp.)合作,為政府和行業(yè)資助項目確定應該優(yōu)先做哪些研究。預計其他ITRS參與者將在新名稱下開展新的路線圖工作,作為IEEE“重啟計算”(RebootingComputing)計劃的一部分。

這些路線圖變化看似是無關(guān)緊要的管理變動,但是,“在行業(yè)里,這是一場重大破壞,或者說是地震”,市場分析公司VLSI研究公司(位于加州圣何塞)的首席執(zhí)行官丹?哈奇森(Dan Hutcheson)如是說。20世紀90年代初,也就是路線圖工作剛開始的時候,美國半導體企業(yè)有理由開展合作,確定共同需求,最終于1998年促成了ITRS的建立。他說,供應商們很難知道半導體企業(yè)的確切需求,因此各芯片公司集體確定優(yōu)先工作,充分利用有限的研發(fā)資金,這也就說得通了。

但要維持摩爾定律的領(lǐng)先優(yōu)勢,會面臨重重困難,耗費大量資金,因此導致行業(yè)出現(xiàn)重大整合。據(jù)哈奇森計算,2001年有19家企業(yè)在研發(fā)和制造配備先進晶體管的邏輯芯片,而今天只剩格羅方德、英特爾、三星和臺積電4家。(此前,IBM也曾屬于這一方陣,但其芯片制造工廠被格羅方德收購了。)

哈奇森表示,這些公司有自己的路線圖,而且可以與其設(shè)備和材料供應商直接溝通。此外,它們極具競爭力。“他們并不想坐在屋子里,談談自己需要什么。”他說,“有點像橄欖球賽季剛開始的時候,一切都很有趣,但進入季后賽,就變得很殘酷了。”

ITRS主席保羅?佳基尼(Paolo Gargini)也同意“這個行業(yè)已經(jīng)變了”,而且他還強調(diào)了其他變化。不再自己制造先進芯片的半導體公司現(xiàn)在依靠芯片代工廠來提供先進技術(shù)。而且,他還說,芯片買方和設(shè)計方(如蘋果、谷歌和高通等公司)對未來的芯片提出了越來越多的要求。佳基尼說:“曾經(jīng)是由半導體公司來決定半導體應具有的功能特征。但現(xiàn)在,這種情況一去不復返了。”最后一份ITRS報告被稱為ITRS2.0,反映出計算上的提高不再是自下而上進行,不再追求更小的開關(guān)、更密集或更快的內(nèi)存。這份報告更多地采取了自上而下的方法,專注于數(shù)據(jù)中心、物聯(lián)網(wǎng)、移動設(shè)備等推動芯片設(shè)計的應用。

新的IEEE路線圖——國際設(shè)備和系統(tǒng)路線圖(IRDS)——也將采用這種方法,但還會加入計算機架構(gòu),實現(xiàn)“一個包括設(shè)備、組件、系統(tǒng)、架構(gòu)和軟件在內(nèi)的,全面的、端到端的計算生態(tài)系統(tǒng)”。

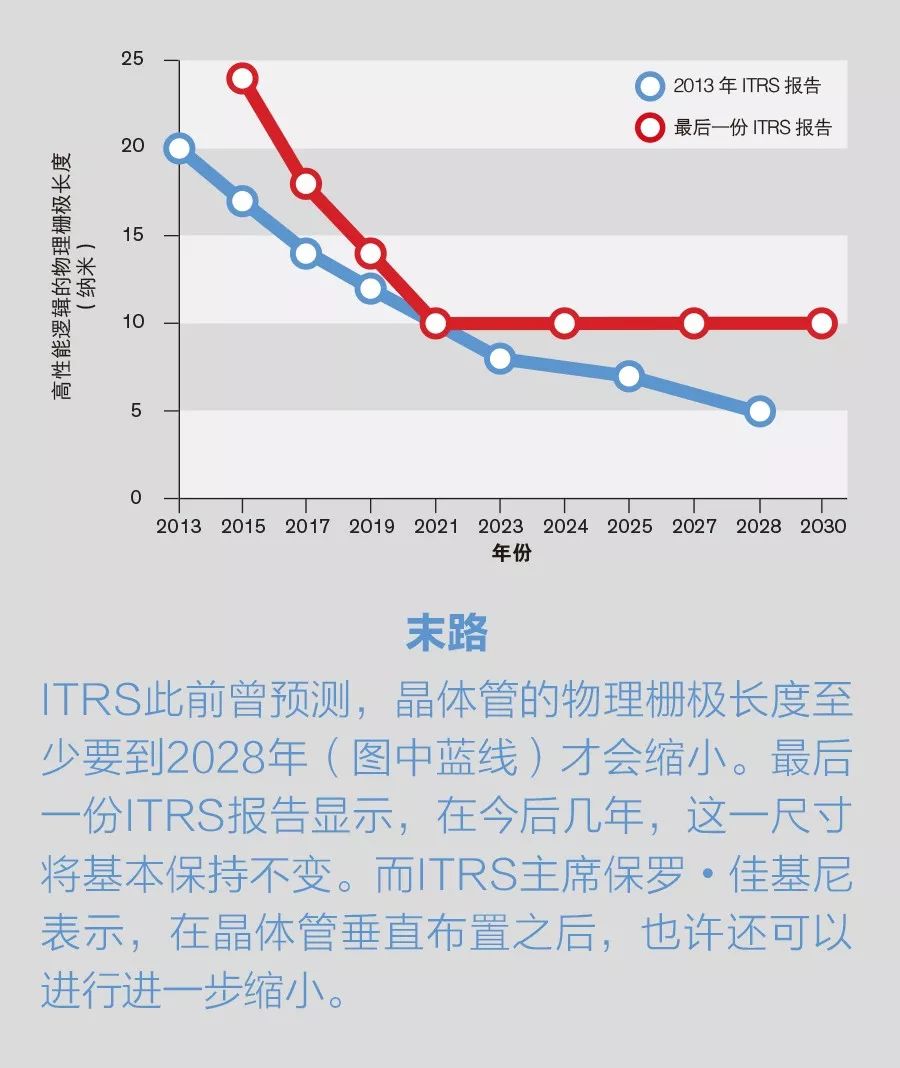

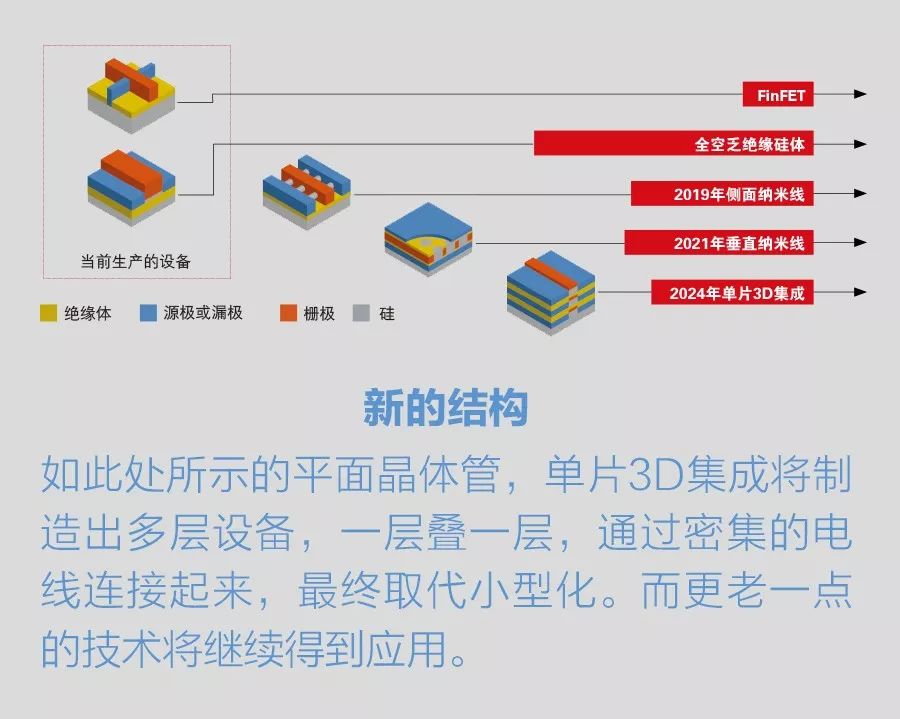

直到2014年發(fā)布2013年ITRS報告(也就是倒數(shù)第二份路線圖)之時,晶體管小型化還屬于長期預測內(nèi)容。那份報告預測,晶體管的物理柵極長度(說明電流在設(shè)備中必須穿行多遠的指標)和其他關(guān)鍵的邏輯芯片尺寸至少在2028年之前會繼續(xù)縮小。然而自那之后,3D概念發(fā)展起來。存儲行業(yè)也早已轉(zhuǎn)向3D架構(gòu)來緩解小型化壓力,提高NAND閃存的容量。將元件一層疊一層并用許多電線連接的單片3D集成已成為越來越熱門的討論話題。

2015年報告包含了這些趨勢,預測到21世紀20年代初,一直以來的縮小趨勢——芯片尺寸的縮小——將結(jié)束。但佳基尼表示,認為摩爾定律即將消亡的想法“是完全錯誤的”。“媒體發(fā)明了多種定義摩爾定律的方法,但其實真正的定義只有一種:每兩年,晶體管的數(shù)量都會翻倍。”

他強調(diào),摩爾定律只是預測集成電路的某一區(qū)域能有多少個晶體管——無論是幾十年來的單層布置還是多層堆疊。佳基尼說,如果一家公司真的想縮小晶體管尺寸,那么就能繼續(xù)縮小到本世紀20年代,“但采用3D辦法更為經(jīng)濟。這就是我們想傳遞的信息”。

其他變化也即將發(fā)生。今后幾年里,在3D集成獲得采用之前,ITRS預測,領(lǐng)先的芯片企業(yè)將不再使用現(xiàn)在高性能芯片上應用的晶體管結(jié)構(gòu):鰭式場效應晶體管(FinFET)。該設(shè)備有一個柵極圍繞水平鰭形通道的3個方向,控制電流通過。根據(jù)最新路線圖,芯片制造商們將放棄這種結(jié)構(gòu),轉(zhuǎn)而選擇一個柵極從側(cè)面控制各個方向的元件。該元件也像FinFET那樣有一個水平通道,但是柵極延伸到了通道下方,將通道環(huán)繞起來。之后,晶體管將變成垂直的,其通道像硅柱或納米線一樣豎立起來。該報告還預測,傳統(tǒng)的硅通道將被其他材料制成的通道取代,如硅鍺、鍺,以及三族和五族元素構(gòu)成的化合物。

有了這些變化,各公司將能在某一區(qū)域中配置更多的晶體管,從而遵守摩爾定律的內(nèi)容。但遵守摩爾定律的精神——計算性能的穩(wěn)步提高——就是另一回事了。

IEEE計算機學會主席兼IEEE重啟計算計劃的共同領(lǐng)導人湯姆?康特(Tom Conte)提出,有一段時間,人們并沒有把晶體管密度的翻倍和計算性能的提高聯(lián)系起來。

在很長一段時間里,晶體管體積的縮小就意味著速度的提升。但康特說,在20世紀90年代中期,為了把越來越多的晶體管用線連起來,需要更多的金屬層,這嚴重耽誤了時間,工程師們不得不重新設(shè)計芯片的微架構(gòu)來提高性能。10年后,由于晶體管密度過大,其散發(fā)出的熱量限制了時鐘速度。各公司開始在芯片上加入更多核心以保持運轉(zhuǎn)。

“我們一直生活在這個泡沫之中,計算機行業(yè)依靠設(shè)備方完成自己的工作,所以,計算機行業(yè)和設(shè)備行業(yè)之間有一堵非常美好的墻。”康特說,“2005年那堵墻開始真正坍塌,自那之后,我們有了越來越多的晶體管,但它們的性能真的沒有提高很多。”

2015年,在IRDS啟動之前,這堵坍塌的墻成為了IEEE重啟計算計劃開始與ITRS協(xié)作的強大動力。康特表示:“我想說我們能看到通道另一端的光,我們也知道那是一列迎面駛來的火車。”

重啟計算計劃之后召開的一次峰會,涵蓋了所有具有未來計算潛力的技術(shù),如新款晶體管和存儲元件、神經(jīng)形態(tài)計算、超導電路,以及使用近似答案而非準確答案的處理器。

康特說,IRDS將追尋“摩爾定律直到最后”。但路線圖的焦點發(fā)生了變化。“并不是說這是摩爾定律的終結(jié),”他說,“只是后退一步,談談此時真正重要的事情——而此時真正重要的就是計算。”

-

芯片

+關(guān)注

關(guān)注

459文章

52199瀏覽量

436378 -

半導體

+關(guān)注

關(guān)注

335文章

28613瀏覽量

232796 -

晶體管

+關(guān)注

關(guān)注

77文章

9979瀏覽量

140695

原文標題:到2021年,晶體管體積將停止縮小

文章出處:【微信號:IEEE_China,微信公眾號:IEEE電氣電子工程師】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

鰭式場效應晶體管的原理和優(yōu)勢

晶體管電路設(shè)計(下)

晶體管電路設(shè)計與制作

晶體管與場效應管的區(qū)別 晶體管的封裝類型及其特點

微型晶體管怎么做出來的

預測2030年5G RedCap連接數(shù)或達近10億

達林頓晶體管概述和作用

晶體管的輸出特性是什么

CMOS晶體管的尺寸規(guī)則

NMOS晶體管和PMOS晶體管的區(qū)別

CMOS晶體管和MOSFET晶體管的區(qū)別

晶體管處于放大狀態(tài)的條件是什么

芯片中的晶體管是怎么工作的

PNP晶體管符號和結(jié)構(gòu) 晶體管測試儀電路圖

2016年發(fā)布ITRS做出預測,晶體管的尺寸可能將在5年后停止縮減

2016年發(fā)布ITRS做出預測,晶體管的尺寸可能將在5年后停止縮減

評論