在傳統(tǒng)的概念中,芯片工藝的改進(jìn)將會帶來性能的提高,成本的降低。同時,由于芯片內(nèi)核電壓的降低,其所消耗的功耗也隨之降低,這一點(diǎn)到0.13um時代也是正確的。

但是在工藝進(jìn)入90nm時代,甚至于以后的40nm或更小的工藝,出現(xiàn)了一點(diǎn)反常,芯片功耗將顯著提高。

由于40nm工藝的內(nèi)核電壓進(jìn)一步降低,電壓降低的一個負(fù)面影響是晶體管中的溝道(channel)內(nèi)的電場減弱,于是電子移動速度降低,實際上也就是晶體管的傳播延時(tpd)增加了。為了達(dá)到非常高的性能,芯片設(shè)計廠商通常降低晶體管的門檻電壓(Vth),使得晶體管快速開關(guān),用來達(dá)到較小傳播延時的目的。這個Vth就是使得晶體管的溝道(channel)開始導(dǎo)通時的最小電壓值。

而Vth的降低,帶來一個嚴(yán)重影響,就是晶體管漏電流隨著Vth的降低呈指數(shù)增加,這樣就會使得芯片的靜態(tài)功耗大大增加,因此40nm的芯片制造商就是需要在芯片性能和其能承受的漏電流之間做一個權(quán)衡。

總的來說,芯片進(jìn)入40nm時代后,門檻電壓的降低以及晶體管尺寸的減小,都將會導(dǎo)致芯片漏電流增加,而這個漏電流就成為芯片靜態(tài)功耗的主要來源,有的甚至高于芯片工作的動態(tài)功耗。

新工藝的使用反而帶來功耗的大幅度增加,這是目前半導(dǎo)體業(yè)界所需要面臨的一個普遍的問題。而功耗增加所帶來的問題主要是芯片在工作中將產(chǎn)生更多的熱量,如果這些熱量不及時散播出去,芯片的溫度將會升高,嚴(yán)重的時候有可能會導(dǎo)致芯片工作異常,甚至失效。

FPGA的功耗

FPGA器件的一個比較特別的現(xiàn)象是其上電瞬間的電流比較大,有的時候甚至大于芯片正常工作的電流,這是因為FPGA內(nèi)部的邏輯和互連線資源(SRAM工藝)在上電的瞬間處于不確定狀態(tài),發(fā)生電流沖突的結(jié)果。

如果用戶在設(shè)計的時候沒有考慮到這個上電瞬間的打電流,電源模塊不能夠提供這么大的電流,芯片在上電過程中就會出現(xiàn)上電曲線不單調(diào)的問題,導(dǎo)致器件上電失敗,以至于芯片無法正常工作。一般在器件手冊中會給出這個上電電流值。

FPGA在正常工作中,其消耗的總功耗由器件的靜態(tài)功耗、動態(tài)功耗和IO功耗構(gòu)成。靜態(tài)功耗也叫待機(jī)功耗(standby power),是芯片處于上電狀態(tài),但是內(nèi)部電路沒有工作(也就是內(nèi)部電路沒有翻轉(zhuǎn))時消耗的功耗;而所謂動態(tài)功耗是指由于內(nèi)部電路翻轉(zhuǎn)所消耗的功耗;IO功耗是IO翻轉(zhuǎn)時,對外部負(fù)載電容進(jìn)行充放電所消耗的功耗。

如下式:

總功耗=靜態(tài)功耗+動態(tài)功耗+IO功耗

芯片的靜態(tài)功耗是芯片處于待機(jī)狀態(tài)下所消耗的功耗,它主要由芯片內(nèi)部的漏電流產(chǎn)生。在高速的40nm器件中(如stratic IV),芯片的漏電流相對來說較大,因此靜態(tài)功耗成為主要的電源功耗,也叫漏電功耗(leakage power)。

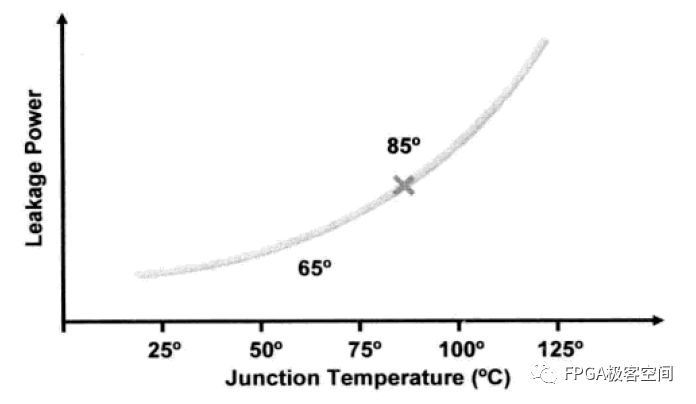

靜態(tài)功耗有一個顯著的特點(diǎn),就是它隨著器件結(jié)溫(junction temperature,TJ)的變化而變化較大。TJ越大,功耗越大;TJ越小,功耗越小,如下圖所示。因此,控制芯片的結(jié)溫可以有效的控制芯片的靜態(tài)功耗。

漏電功耗與器件結(jié)溫的關(guān)系

相比以前的器件工藝(如0.13um),40nm器件由于內(nèi)核電壓的降低,芯片在工作時所消耗的動態(tài)功耗也相應(yīng)降低。

至于IO功耗,因為其電源是與內(nèi)核分開的,所以它消耗的功耗改變不大。

不同工藝器件的功耗組成如下圖:

不同工藝器件功耗比較

功耗增加是40nm高速芯片的結(jié)果。如果芯片設(shè)計者降低器件的性能規(guī)格,那么其功耗也將隨之顯著降低。ALTERA 65nm的低成本器件CYCLONE III 就是一個很好的例子。

ALTERA為了使用戶能夠準(zhǔn)確地評估其芯片在工作時候的實際功耗,提供了一種功耗計算的方法。

功耗計算器:用戶需要估算FPGA中的各種資源使用情況,包括LE,RAM,PLL,DPS塊和IO口等,以及它們工作的時鐘頻率。同時,用戶也需要估計各種資源工作過程中的翻轉(zhuǎn)率,這對芯片的動態(tài)功耗影響非常大。表格中同樣給出了靜態(tài)功耗值。在40nm的Stratix IV器件中,由于靜態(tài)功耗受結(jié)溫影響較大,因此計算表格中還需要用戶輸入環(huán)境溫度、表面風(fēng)速和散熱片類型等參數(shù),用來估計芯片的實際待機(jī)功耗。如果用戶的設(shè)計已經(jīng)完成,用戶可以在quartusii中輸出一個功耗估計文件,將其載入到估計表格中,就可以自動載入精確的器件資源使用情況。

基于仿真的功耗估計(powergauge):quartus ii提供了一種功耗估計工具。在使用之前,用戶必須首先編譯設(shè)計,然后根據(jù)設(shè)計的實際情況,給設(shè)計加一些激勵,再在quartusii中對這個設(shè)計進(jìn)行時序仿真。Powergauge可以在仿真過程中估算出芯片實際工作時的功耗,這種方法通常是在設(shè)計的后期用來精確估計芯片功耗時采用。和計算表格相比,它準(zhǔn)確,但耗時。

-

FPGA

+關(guān)注

關(guān)注

1645文章

22050瀏覽量

618472 -

芯片

+關(guān)注

關(guān)注

460文章

52520瀏覽量

440900 -

功耗

+關(guān)注

關(guān)注

1文章

836瀏覽量

32674

原文標(biāo)題:功耗的挑戰(zhàn)

文章出處:【微信號:ALIFPGA,微信公眾號:FPGA極客空間】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

深度解析FPGA的功耗

深度解析FPGA的功耗

評論