工藝原理

CSP(Chip Scale Package,芯片級(jí)封裝)技術(shù)是一種先進(jìn)的封裝技術(shù),其焊端通常設(shè)計(jì)為直徑0.25mm的焊球。這種設(shè)計(jì)不僅減小了封裝尺寸,還提高了集成度。在焊接過(guò)程中,焊膏首先融化,隨后焊球融化,這種順序融化機(jī)制有助于避免焊球間的橋連問(wèn)題,但可能因印刷過(guò)程中的少印而導(dǎo)致球窩、開(kāi)焊等缺陷。因此,對(duì)于0.4mm間距的CSP,確保印刷過(guò)程中獲得足夠的焊膏量是關(guān)鍵。

基準(zhǔn)工藝

為了優(yōu)化CSP的焊接效果,基準(zhǔn)工藝設(shè)定如下:

模板厚度:0.08mm。這一厚度選擇旨在平衡焊膏的填充性和溢出控制,確保焊膏能夠均勻且適量地覆蓋焊盤。

模板開(kāi)口直徑:ф0.25mm,與焊球直徑相匹配,以確保焊膏能夠準(zhǔn)確、完整地填充到焊球下方的區(qū)域。

模板類型:推薦使用FG模板。FG模板(Fine Grain模板)以其精細(xì)的網(wǎng)孔結(jié)構(gòu)和優(yōu)異的脫模性能,有助于實(shí)現(xiàn)高精度的焊膏印刷。

接受條件

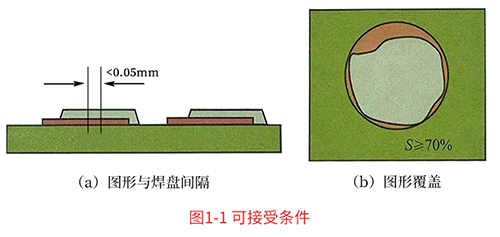

可接受條件:

焊膏圖形中心位置:焊膏圖形中心偏離焊盤中心應(yīng)小于0.05mm,以確保焊膏的準(zhǔn)確位置,避免焊接不良。

焊膏量:焊膏量覆蓋率超出焊盤75%~125%的范圍(通過(guò)SPI檢測(cè))。這一范圍確保了焊膏的充足性,同時(shí)避免了過(guò)量焊膏可能導(dǎo)致的短路問(wèn)題。

焊膏覆蓋面積:焊膏覆蓋面積應(yīng)大于或等于模板開(kāi)口面積的70%,以確保焊膏能夠充分覆蓋焊盤,提高焊接的可靠性和穩(wěn)定性。

印刷質(zhì)量:

無(wú)漏印現(xiàn)象,且擠印引發(fā)的焊膏與焊盤最小間隔應(yīng)大于或等于0.5mm2,以避免短路風(fēng)險(xiǎn)。

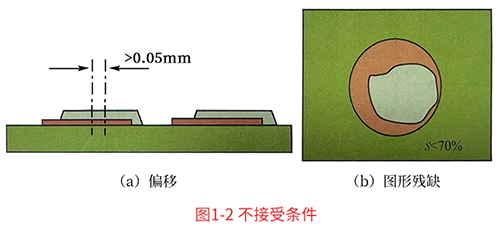

不接受條件

焊膏圖形中心位置偏移:圖形中心偏離焊盤中心大于0.05mm,這可能導(dǎo)致焊接不良,產(chǎn)生錫珠,影響封裝質(zhì)量。

焊膏量異常:焊膏量覆蓋率超出焊盤75%~125%的范圍,無(wú)論是過(guò)多還是過(guò)少,都可能對(duì)焊接質(zhì)量產(chǎn)生不利影響。

焊膏覆蓋面積不足:圖形覆蓋面積小于模板開(kāi)口面積的70%,這可能導(dǎo)致焊盤部分區(qū)域無(wú)焊膏覆蓋,進(jìn)而影響焊接的可靠性。

印刷缺陷:出現(xiàn)焊膏漏印、嚴(yán)重?cái)D印與拉尖等缺陷,這些都會(huì)直接影響焊接的質(zhì)量和穩(wěn)定性,因此不被接受。

總的來(lái)說(shuō),CSP封裝工藝的成功實(shí)施需要嚴(yán)格控制焊膏的印刷過(guò)程,確保焊膏的準(zhǔn)確位置、適量填充和良好覆蓋,以滿足嚴(yán)格的焊接質(zhì)量要求。

審核編輯 黃宇

-

封裝

+關(guān)注

關(guān)注

128文章

8522瀏覽量

144822 -

CSP

+關(guān)注

關(guān)注

0文章

125瀏覽量

28592 -

焊盤

+關(guān)注

關(guān)注

6文章

589瀏覽量

38705

發(fā)布評(píng)論請(qǐng)先 登錄

芯片封裝工藝詳解

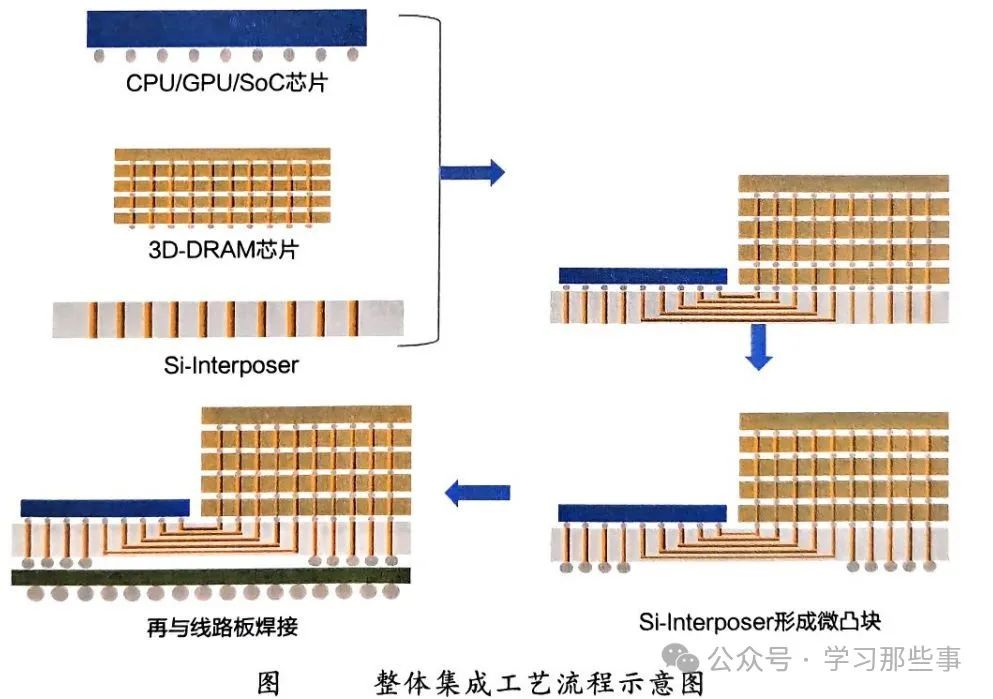

一文詳解2.5D封裝工藝

一種新型RDL PoP扇出晶圓級(jí)封裝工藝芯片到晶圓鍵合技術(shù)

倒裝封裝(Flip Chip)工藝:半導(dǎo)體封裝的璀璨明星!

功率模塊封裝工藝

功率模塊封裝工藝有哪些

深入剖析:封裝工藝對(duì)硅片翹曲的復(fù)雜影響

瑞沃微:一文詳解CSP(Chip Scale Package)芯片級(jí)封裝工藝

CSP(Chip Scale Package)封裝工藝詳解?

CSP(Chip Scale Package)封裝工藝詳解?

評(píng)論