1. 項(xiàng)目背景

蜜罐技術(shù)由來已久,蜜罐(Honeypot)是一種在互聯(lián)網(wǎng)上運(yùn)行的計(jì)算機(jī)系統(tǒng)。它是專門為吸引并誘騙那些試圖非法闖入他人計(jì)算機(jī)系統(tǒng)的人(如電腦黑客)而設(shè)計(jì)的,蜜罐系統(tǒng)是一個(gè)包含漏洞的誘騙系統(tǒng),它通過模擬一個(gè)或多個(gè)易受攻擊的主機(jī),給攻擊者提供一個(gè)容易攻擊的目標(biāo)。由于蜜罐并沒有向外界提供真正有價(jià)值的服務(wù),因此所有對(duì)蜜罐嘗試都被視為可疑的。蜜罐的另一個(gè)用途是拖延攻擊者對(duì)真正目標(biāo)的攻擊,讓攻擊者在蜜罐上浪費(fèi)時(shí)間。簡單點(diǎn)一說:蜜罐就是誘捕攻擊者的一個(gè)陷阱。根據(jù)蜜罐與攻擊者之間進(jìn)行的交互,可以分為3類:低交互蜜罐,中交互蜜罐和高交互蜜罐。

目前市面上的蜜罐都是利用軟件來實(shí)現(xiàn)的,軟件有它速度慢、依賴性強(qiáng)、程序復(fù)雜等弱點(diǎn),基于蜜罐需要快速大量的數(shù)據(jù)匹配(入侵審計(jì)等)和安全的系統(tǒng)(簡單),我們想到可以用硬件FPGA實(shí)現(xiàn)蜜罐技術(shù)。目前用硬件實(shí)現(xiàn)蜜罐技術(shù)在網(wǎng)絡(luò)和相關(guān)書籍雜志上都不曾出現(xiàn)過。

2.項(xiàng)目目標(biāo)

作為我們用XILINUX公司的SPARTEN-3E實(shí)驗(yàn)板來做的這次實(shí)驗(yàn),我們?cè)诨镜牡徒换ッ酃薜幕A(chǔ)上,自己編寫了操作系統(tǒng)和內(nèi)核,做到了高交互的蜜罐系統(tǒng)。

3.項(xiàng)目的主要內(nèi)容

本項(xiàng)目一共分為三部分

a.蜜墻的設(shè)定

功能:

利用FPGA實(shí)現(xiàn)IDS和入侵檢測、入侵審計(jì)的功能

防止黑客利用蜜罐作為跳板攻擊服務(wù)器

b.蜜罐的構(gòu)建

功能:

用FPGA模擬出一個(gè)真實(shí)的操作系統(tǒng)

在FPGA實(shí)驗(yàn)板上用操作系統(tǒng)建立一個(gè)高交互的蜜罐,讓黑客攻擊

c.數(shù)據(jù)的采集和分析

功能:

把蜜罐上的有效數(shù)據(jù)安全的轉(zhuǎn)移到其他地方

研究并分析黑客或木馬病毒的攻擊行為

4.項(xiàng)目關(guān)鍵技術(shù)及創(chuàng)新點(diǎn)的論述

關(guān)鍵技術(shù)包括:IDS入侵檢測、入侵審計(jì)、蜜罐技術(shù)及其相關(guān)的日志記錄分析,honeynet和蜜墻功能。

國內(nèi)目前還沒有任何用FPGA或者相關(guān)的硬件平臺(tái)來實(shí)現(xiàn)蜜罐、蜜墻,所有的蜜罐技術(shù)都是基于在軟件平臺(tái)上的實(shí)現(xiàn)。同時(shí),F(xiàn)PGA的終端安全防護(hù)一直處于被動(dòng)防護(hù)的狀態(tài),如果可以用蜜罐技術(shù),就能把終端防護(hù)由被動(dòng)變?yōu)橹鲃?dòng),能加有效安全得保護(hù)終端的安全。

5.項(xiàng)目的成果

我們最終完成了項(xiàng)目主要工作中的功能實(shí)現(xiàn),并對(duì)于整個(gè)蜜罐蜜墻所組成的系統(tǒng)用不同的攻擊手段進(jìn)行了測試,測試結(jié)果表明,我們用FPGA實(shí)現(xiàn)的這套系統(tǒng)可以完成期望的目標(biāo)。

1.采用FPGA實(shí)現(xiàn)蜜墻技術(shù),幾乎包含現(xiàn)在終端攻擊中全部的攻擊方式的入侵檢測。

2.利用蜜墻將攻擊誘導(dǎo)到FPGA實(shí)現(xiàn)的蜜罐上。

3.實(shí)現(xiàn)了日志記錄,檢測并分析攻擊的特征和方式,來更進(jìn)一步了解攻擊,為今后的防御贏得主動(dòng)。

需求分析和項(xiàng)目目標(biāo)

1.1 需求分析

蜜罐發(fā)展的3個(gè)過程:

低交互蜜罐最大的特點(diǎn)是模擬。蜜罐為攻擊者展示的所有攻擊弱點(diǎn)和攻擊對(duì)象都不是真正的產(chǎn)品系統(tǒng),而是對(duì)各種系統(tǒng)及其提供的服務(wù)的模擬。由于它的服務(wù)都是模擬的行為,所以蜜罐可以獲得的信息非常有限,只能對(duì)攻擊者進(jìn)行簡單的應(yīng)答,它是最安全的蜜罐類型。

中交互是對(duì)真正的操作系統(tǒng)的各種行為的模擬,它提供了更多的交互信息,同時(shí)也可以從攻擊者的行為中獲得更多的信息。在這個(gè)模擬行為的系統(tǒng)中,蜜罐可以看起來和一個(gè)真正的操作系統(tǒng)沒有區(qū)別。它們是真正系統(tǒng)還要誘人的攻擊目標(biāo)。

高交互蜜罐具有一個(gè)真實(shí)的操作系統(tǒng),它的優(yōu)點(diǎn)體現(xiàn)在對(duì)攻擊者提供真實(shí)的系統(tǒng),當(dāng)攻擊者獲得ROOT權(quán)限后,受系統(tǒng),數(shù)據(jù)真實(shí)性的迷惑,他的更多活動(dòng)和行為將被記錄下來。缺點(diǎn)是被入侵的可能性很高,如果整個(gè)高蜜罐被入侵,那么它就會(huì)成為攻擊者下一步攻擊的跳板。

但是,如果我們有一個(gè)蜜墻來有效的防治黑客利用蜜罐作為跳板,那么就可以很好的解決高交互蜜罐的缺點(diǎn),讓蜜罐真正變成一個(gè)我們可以控制的安全的陷阱。并且我們用硬件實(shí)現(xiàn)蜜罐技術(shù),比用軟件在速度上快數(shù)百倍,F(xiàn)PGA上可以安裝實(shí)時(shí)性操作系統(tǒng),并且硬件比軟件在程序上更簡單、更基礎(chǔ),防護(hù)效果更好。

1.2實(shí)現(xiàn)的功能目標(biāo)

用FPGA實(shí)現(xiàn)高交互的蜜罐技術(shù)并實(shí)現(xiàn)蜜墻功能,通過對(duì)硬件的底層編程實(shí)現(xiàn)

1.3項(xiàng)目可行性分析

因?yàn)橛糜布?shí)現(xiàn)蜜罐技術(shù)在目前世界、至少是中國網(wǎng)站上沒有出現(xiàn)過,屬于首創(chuàng),里面的很多技術(shù)問題尤其是軟件到硬件的編程和實(shí)現(xiàn)是我們所面臨的主要問題,但是硬件的速度快,結(jié)構(gòu)簡單,實(shí)時(shí)性好,這些特點(diǎn)我們可以充分利用在蜜罐和蜜墻上,來實(shí)現(xiàn)我們的硬件蜜罐,比軟件實(shí)現(xiàn)的優(yōu)勢還是非常的明顯的。

項(xiàng)目總體設(shè)計(jì)

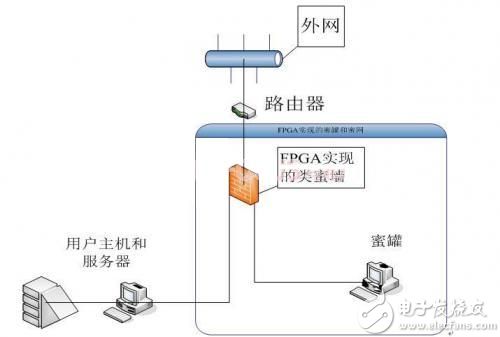

2.1總體結(jié)構(gòu)圖

上面是我們大致的系統(tǒng)架構(gòu)圖。我們可以看到,以太網(wǎng)相當(dāng)于外網(wǎng)通過路由器首先經(jīng)過我們用FPGA實(shí)現(xiàn)的蜜墻。他具有IDS、入侵檢測、入侵審計(jì)等多種功能,最重要的是,高交互的蜜罐很容易在被攻破以后被黑客作為攻擊主服務(wù)器的跳板,但是蜜墻就可以做好很好的防止從蜜罐到服務(wù)器的攻擊,簡單的說,他對(duì)于蜜罐是一個(gè)只進(jìn)不出的防火墻。

數(shù)據(jù)流經(jīng)過了蜜墻以后,我們對(duì)數(shù)據(jù)進(jìn)行分析,當(dāng)沒有發(fā)現(xiàn)攻擊信息的時(shí)候,數(shù)據(jù)流作為正常數(shù)據(jù)通過蜜墻發(fā)給服務(wù)器,如果我們檢測出了入侵攻擊,那么蜜墻會(huì)利用IP欺騙技術(shù)把攻擊的數(shù)據(jù)流引到蜜罐上,這樣黑客攻擊的就只能是蜜罐而無法接觸到真正的服務(wù)器。

在蜜罐上,我們進(jìn)行實(shí)時(shí)監(jiān)控,黑客的一舉一動(dòng)都在我們的監(jiān)視下,通過安全的途徑把蜜罐上的信息導(dǎo)出,我們可以分析這些信息對(duì)黑客的行為進(jìn)行了解和掌握,并以此來對(duì)未來其他的攻擊方式進(jìn)行主動(dòng)的防御。

FPGA硬件實(shí)現(xiàn)帶網(wǎng)絡(luò)連接的操作系統(tǒng)內(nèi)核

3.1系統(tǒng)硬件的基本構(gòu)成與配置

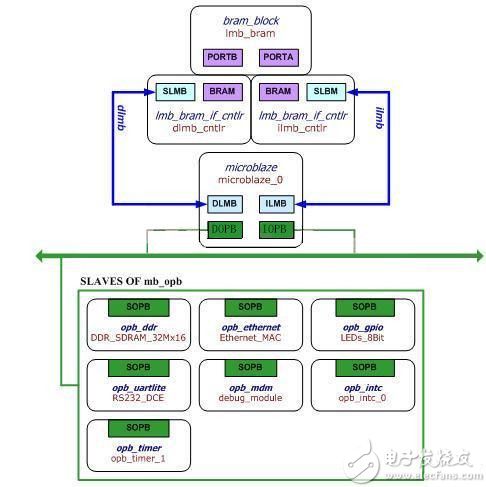

系統(tǒng)的硬件設(shè)計(jì)使用 Xilinx Platform Studio 集成開發(fā)環(huán)境中的 Base System Builder 進(jìn)行配置。完成設(shè)計(jì)的系統(tǒng)框圖如圖XX所示。

系統(tǒng)硬件框圖

整個(gè)系統(tǒng)硬件的核心是Microblaze 處理器,處理器的基本配置和主要外設(shè)包括:

3.2 硬件功能與指標(biāo)

一、Microblaze 處理器:

處理器總線頻率: 66.7 MHz;

片上內(nèi)存(BRAM):16KB;

由于Spartan-3e XC3S500E 的BRAM資源有限,沒有選擇 Cache 功能;

二、基本外設(shè)配置:

波特率:115200,使用中斷;

(2)以太網(wǎng)MAC:

使用 Xilinx Ethernet_MAC IP,其配置參數(shù)為:No DMA,使用中斷,并選擇 FIFO 方式,以滿足在 Xilkernel 系統(tǒng)下,使用lwIP 進(jìn)行 socket 編程的需求;

(3)定時(shí)器:

采用一個(gè)32位定時(shí)器,并使用中斷。

使用開發(fā)板上的 32Mx16內(nèi)存,并配置為 OPB DDR。

此外,系統(tǒng)硬件中還包括:中斷控制器、8個(gè)與通用I/O連接的LED,以及調(diào)試模塊。更為詳盡的硬件平臺(tái)細(xì)節(jié),可以參照系統(tǒng)的硬件描述文件(MHS)。

-

FPGA

+關(guān)注

關(guān)注

1645文章

22050瀏覽量

618427

發(fā)布評(píng)論請(qǐng)先 登錄

基于Matlab與FPGA的雙邊濾波算法實(shí)現(xiàn)

基于FPGA的壓縮算法加速實(shí)現(xiàn)

火爆開發(fā)中 | 開源FPGA硬件板卡,硬件第一期發(fā)布

FPGA從0到1學(xué)習(xí)資料集錦

MRAM存儲(chǔ)替代閃存,FPGA升級(jí)新技術(shù)

基于FPGA實(shí)現(xiàn)圖像直方圖設(shè)計(jì)

FPGA驅(qū)動(dòng)AD芯片之實(shí)現(xiàn)與芯片通信

FPGA與ASIC的優(yōu)缺點(diǎn)比較

FPGA技術(shù)對(duì)5G通信的影響

Altera推出一系列FPGA軟、硬件和開發(fā)工具

FPGA在圖像處理領(lǐng)域的優(yōu)勢有哪些?

如何用FPGA實(shí)現(xiàn)一個(gè)通信系統(tǒng)的發(fā)射端接收機(jī)?

為什么FPGA屬于硬件,還需要搞算法?

FPGA在自動(dòng)駕駛領(lǐng)域有哪些優(yōu)勢?

分享幾個(gè)用FPGA實(shí)現(xiàn)的小型神經(jīng)網(wǎng)絡(luò)

用硬件fpga實(shí)現(xiàn)蜜罐技術(shù)的這些要點(diǎn),學(xué)到就賺了

用硬件fpga實(shí)現(xiàn)蜜罐技術(shù)的這些要點(diǎn),學(xué)到就賺了

評(píng)論