作者:Ken Brock,新思科技公司(Synopsys)產品營銷經理

***積體電路制造公司(簡稱為臺積電(TSMC))最近宣布了其第四個28nm工藝進入了量產 - 28HPC Plus(即28HPC +)。臺積電(TSMC)的前兩項28nm工藝(聚氮氧化硅28LP和高K 金屬閘28HP / 28HPL / 28HPM)已生產了數百萬個生產晶片。臺積電(TSMC)已利用28HPC優化了移動和消費設備在性能和成本之間的平衡需求,然后開發了28HPC +,從而進一步提高性能和降低泄漏。設計人員通過結合這些新工藝技術和專為這些工藝而設計的高質量標準單元邏輯庫,可實現其性能、功耗和面積目標,同時減小設計進度風險。

本文介紹了六個方面,設計人員可以利用這些采用新工藝的最新邏輯庫技術來優化其系統級芯片(SoC)的性能、功耗和面積。

-

首先,臺積電(TSMC)28HPC/HPC+工藝相對于28LP/HP/HPL/HPM,能更好的控制全局慢速和全局快速(SSG,FFG)工藝角,因此可以提高系統級芯片(SoC)性能。改良的性能可以使用較低驅動(較小的)邏輯單元來滿足關鍵時序路徑。

-

其次,臺積電(TSMC)對28HPC工藝進行更嚴格的工藝控制,可以減少對應工藝角中的20%漏電來降低功耗。

-

第三,28HPC +提高了15%性能,降低了25%漏電。

-

第四,28HPC和28HPC +都能減少面積,靈活的工藝規則,使得邏輯庫設計者可以設計出更小的可布線性更好的邏輯單元。

-

第五,這些相同的靈活規則使得能夠得到相對于28HPM工藝更長的溝道長度,從而減少最高50%的漏電,而不需要使用高成本的基于光刻的閘極偏置。

-

第六,在28HPC工藝引入的新的邏輯庫功能,如多重延遲、多重建立時間和多位觸發器(MBFF),可幫助設計人員優化處理器內核的性能和功耗。

創新工藝技術和邏輯庫設計功能的結合,以及最新的EDA工具創新和流程,使系統級芯片(SoC)設計人員能夠利用他們的設計技能,設計出最高性能、 最低成本、最低功耗的產品。

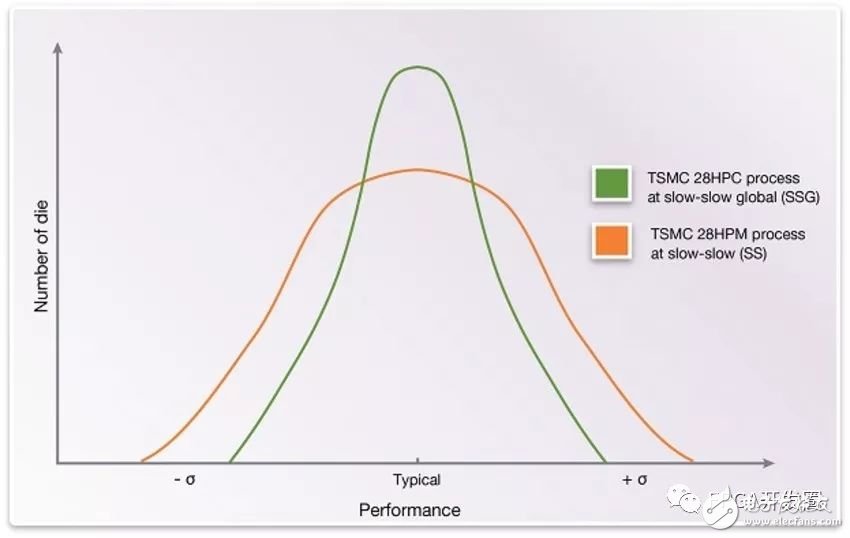

1. 通過全局工藝角簽核來提升系統級芯片(SoC)性能傳統開發的邏輯庫,包括總工藝角工藝、電壓、溫度(PVT)模擬試驗,可反映典型的P溝道和N溝道晶體管性能,統計學上性能最慢的(slow-slow或SS在3 sigma)和性能最快的(fast-fast或FF在3 sigma)。這些工藝角用于模擬典型的預期性能、最慢情況(用于觸發器setup)和最快情況(用于觸發器hold),且包括預期die和die之間、wafer和wafer之間以及lot和lot之間的變化,從而確保良率。

由于工藝變異性的降低,臺積電(TSMC)能夠提供高良率的新工藝角,稱之為slow-slow global(SSG)。與之前的28HPM工藝相比提高了10-15%的性能,這需要更保守的SS 簽核 (圖1)。工藝變異性改進可使處理器運行速度提高10-15%,因此,28HPC邏輯庫必須能夠支持在更高的速度下電路的額外動態功耗和電遷移要求。

圖1. 臺積電(TSMC)28HPC SSG工藝角和28HPM SS 工藝角

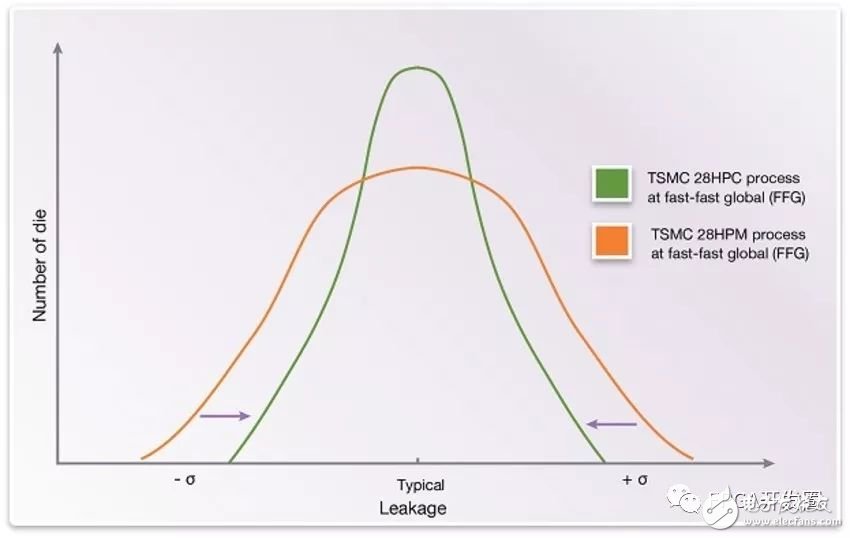

2. 隨著工藝變異性減小,閘門漏電流也減少HPC工藝變異性的改進降低了晶體管泄漏,因此根據不同的工藝選項和條件,28HPC工藝將比28HPM減少約20%的漏電量(圖2)。

圖2. TSMC 28HPC FFG工藝角和28HPM FFG工藝角

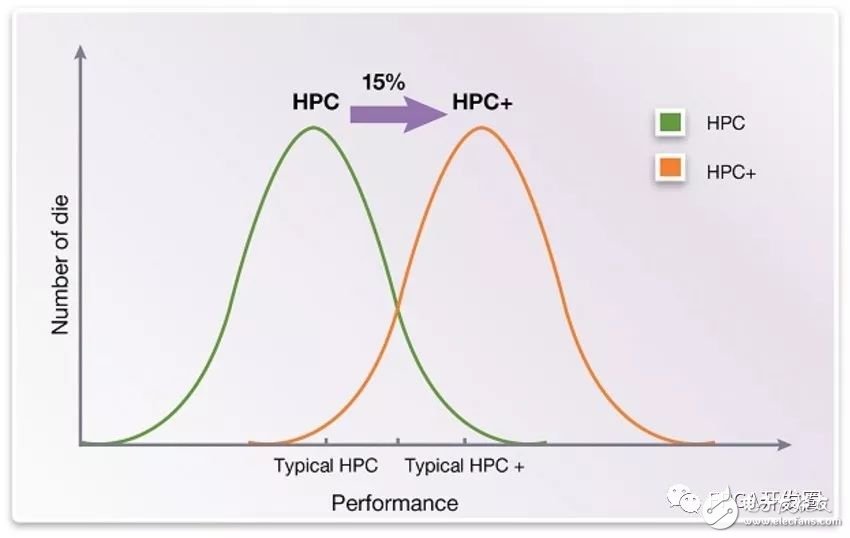

3.使用28HPC +改進工藝秘訣臺積電(TSMC)利用28HPC +改善了28HPM和28HPC上使用的高K金屬工藝,具有新的摻雜特性,并從高K金屬閘上分離了一些原子,提高了15%的性能和降低25%的漏電流。

圖3.左邊的曲線顯示了28HPC的性能分布,右圖顯示了28HPC +的性能分布。請注意,這些曲線比較了相同的SSG工藝角

圖4.右側曲線顯示28HPC的漏電分布,左側顯示28HPC +處的漏電分布。請注意,這些曲線比較了相同的FFG工藝角

因為這是工藝中心的平移,而不僅僅是工藝的加強,現有的電路塊或其它IP塊至少需要重新驗證是否存在違例,或重新進行綜合以利用改良的性能和漏電。

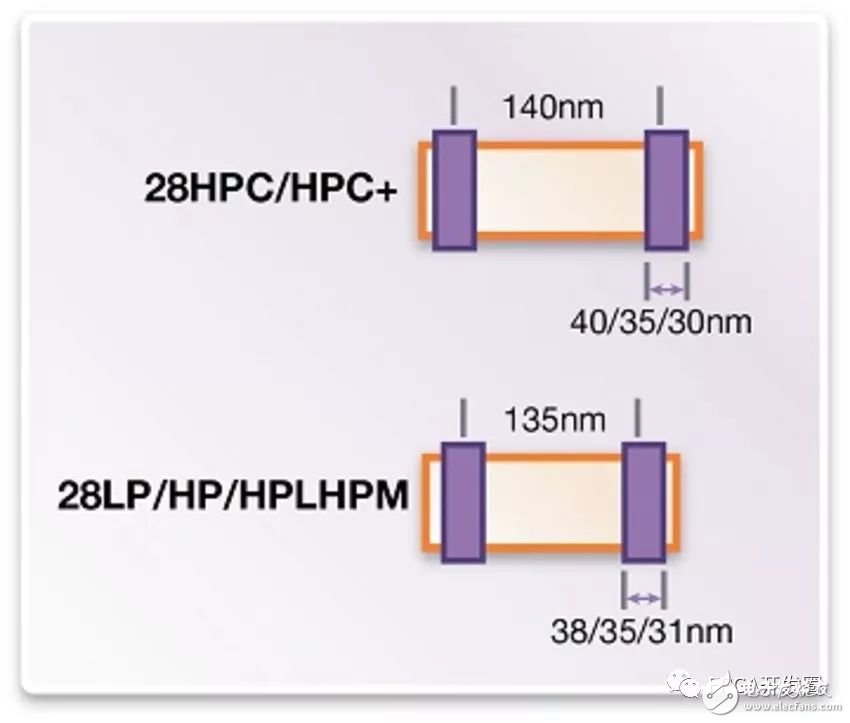

4.更長的溝道長度減少漏電工藝改進帶動了臺積電(TSMC)設計規則的變化,使得邏輯庫相對于TSMC 28HPM可以有更多的柵極長度范圍。

同時,新的靈活設計規則去除了一些光刻步驟,使得以30nm,35nm和40nm繪制的單元格能夠以稍大的柵極間距來改善性能或漏電。

圖5.上面的圖顯示,與下面的28HPM工藝相比,TSMC 28HPC / HPC +工藝的140nm間距和3個柵極長度,為連接提供了更多空間

更寬范圍的柵極長度和相關的光刻簡化,使設計人員能夠使用28HPC優化的邏輯庫,以及綜合和布局布線工具中最新的漏電優化功能,得到更廣泛的性能與漏電折中范圍。

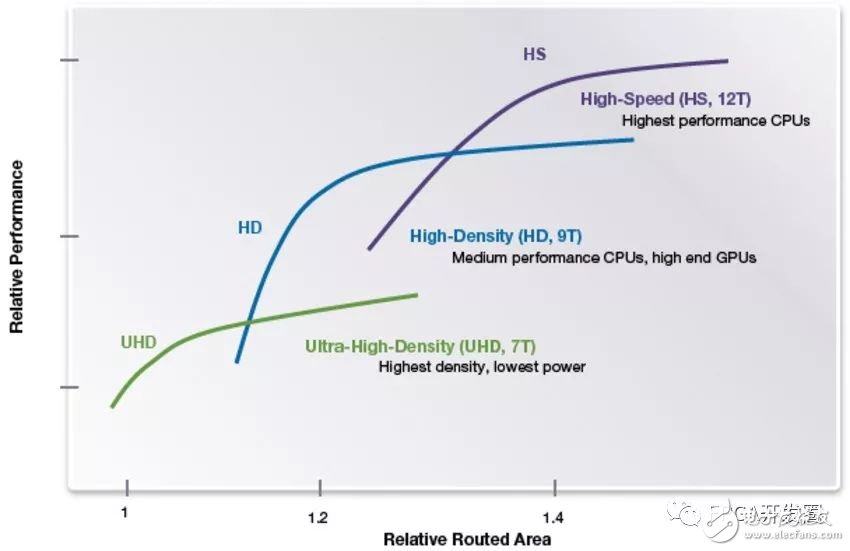

5.靈活的設計規則加強高密度臺積電在28HPC / HPC +工藝中的靈活設計規則和更高的性能,使設計人員能夠在邏輯庫中使用更矮的單元格高度,以便在一些能滿足時序要求的block設計中,得到更小的芯片面積。使用較矮的邏輯庫和實現更高速度之間存在一個折中,因為較矮的邏輯庫需要更大的驅動單元,從而有可能抵消面積節省。 每個邏輯庫在單元高度和性能之間都具有“最佳點”,以此來提供優化結果 ,但是采用更低高度的單元并不總是最好的辦法。

圖6:在較低的頻率下,較矮的邏輯庫可以是某些block的最優選擇

也就是說,臺積電的靈活設計規則使更矮的單元變得更容易繞線,如果邏輯庫設計者利用布局和布線工具中的最新功能來設計邏輯庫,則可通過更好的連接可能性來得到更高的利用率。

6.可大幅改良PPA的邏輯庫設計創新結合TSMC 28HPC / HPC +工藝與創新的邏輯庫設計和優化布局的優點,可以幫助設計工程師通過綜合和布局布線完成RTL數字邏輯設計。 使用優化的邏輯庫電路(如組合邏輯,多重建立、多重延遲觸發器和多位觸發器(MBFF))以及TSMC 28HPC / HPC +工藝來獲得面積及性能優勢。

組合單元

優化寄存器到寄存器路徑需要豐富的標準單元庫,其中包含適當的功能,驅動強度和設計變化。需要合成優化功能(與非、或非、與、或、反相器、緩沖器、異或、同或、多路選擇器、加法器、壓縮器等),以創建最佳綜合效果,優化的布局技術需要最大限度地利用最新的繞線算法來消除擁塞。先進的綜合和布局布線工具可以利用不同的驅動強度,以最佳地處理由單元之間的設計拓撲和物理距離產生的不同扇出和負載。

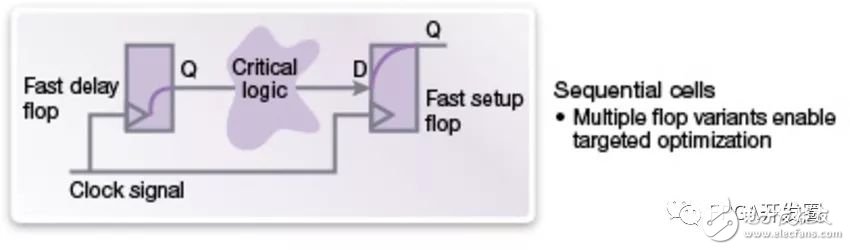

時序單元

觸發器的建立時間加上延遲時間有時被稱為“死區”或“黑洞”時間。 像時鐘不確定性一樣,該時間可以侵蝕每個時鐘周期,而該周期內本可以進行一些有用的計算工作。 需要各種類型的高性能觸發器來對這死區時間進行優化處理。延遲優化的觸發器(多重延遲觸發器)快速地將信號發送到關鍵路徑邏輯中,而建立時間優化的觸發器(多重建立時間觸發器)則可以更快的捕獲寄存器。綜合和繞線優化工具可以有效利用這些多重建立或多重延遲觸發器組,從而提高15-20%的性能。

圖7:時序單元用于解決高性能核心設計挑戰。多重觸發器可實現定向優化

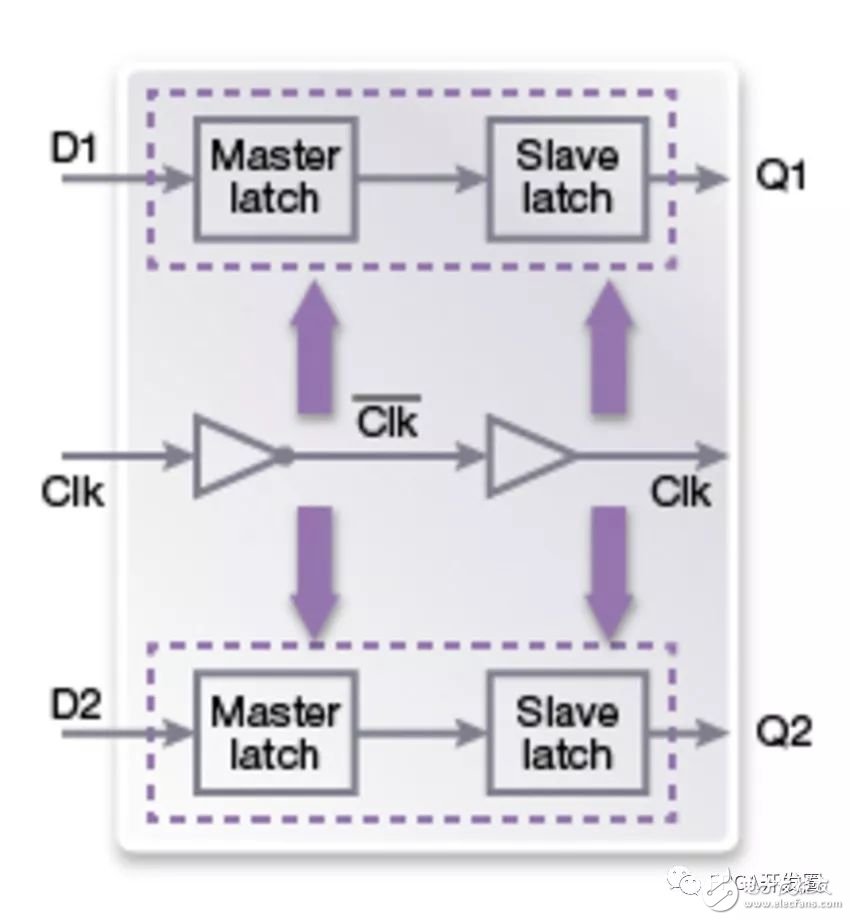

圖8:將兩個單位觸發器組合成具有共享時鐘的雙觸發器

多位觸發器提供了一組額外的觸發器,已經針對功耗和面積進行了優化,在性能和布局靈活性方面進行了輕微的折中。觸發器共享一個公共時鐘引腳,這便降低了多位觸發器單元中N個觸發器的總時鐘負載,減少相應的漏電功耗,并明顯降低時鐘樹上的動態功耗(雙重觸發高達50%,四重或八重會降低更多)。

多位觸發器通常用于不在最高芯片工作頻率的關鍵路徑模塊中。它們的范圍從小型的面向總線的系統級芯片(SoC)配置數據寄存器(僅在上電時計時)到每個周期都計時的、同時之間有多種變量的主要數據路徑。系統級芯片(SoC)設計人員使用替換比率,通過設計中標準觸發器的被替代的數量來衡量,和其產生的PPA改進結果,以確定其整體芯片功率和面積節省量。多位觸發器和被替代的單位觸發器也必須具有相同的功能(時鐘邊沿、置位/復位和掃描配置)。

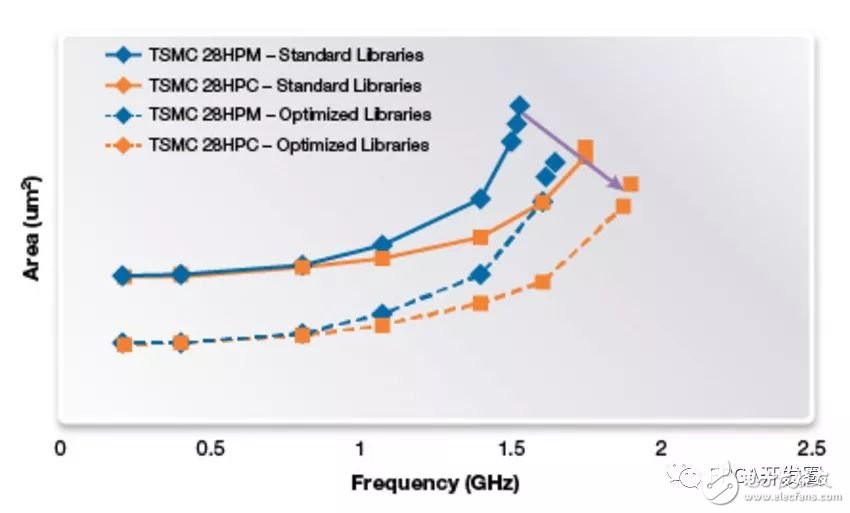

圖7顯示了一個32位處理器,該處理器用TSMC 28HPM(藍線)的邏輯庫綜合,且再次用TSMC 28HPC(橙色線)邏輯庫綜合,您可以發現會得到更小的面積以及更高的性能。而使用Synopsys高性能核心設計套件中的創新邏輯單元將使系統級芯片(SoC)設計人員在更小的面積內實現給定頻率或者得到更高的頻率,如紅色和藍色虛線所示。使用28HPC +工藝將該曲線向右移動15%。

圖9:使用Synopsys邏輯庫將28HPM工藝與28HPC工藝進行比較,并添加Synopsys HPC設計工具庫,通過時序約束來設計32位處理器,直到該庫無法使時序收斂

與最新數字EDA工具功能結合

TSMC 28HPC/HPC+工藝的邏輯庫必須通過數字EDA工具來進行綜合,布局,繞線,驗證和優化以獲得最優的性能,功耗和設計規則兼容性。數字EDA工具和流程使設計人員能夠充分利用電路創新,如多位觸發器和緊湊布局設計成最有效的邏輯庫。

總結臺積電(TSMC)的28HPC高K金屬閘工藝改進了工藝規則和可變性,以利用更少的功耗實現更小的設計,更高的性能。 臺積電(TSMC)的新型28HPC +工藝進一步推動了其發展,并提供了令人難以抗拒的平臺。如果他們擁有合適的邏輯庫,并充分利用這些新的流程功能,領先的綜合、布局和繞線工具可以最大利用這些工藝的改進來滿足嚴格的設計規范要求。采用TSMC 28HPC / HPC + 工藝的Synopsys邏輯庫和領先的EDA工具,旨在使系統級芯片(SoC)設計人員能夠追求性能、面積和功耗的極限,并充分利用這些新工藝的功能。

-

soc

+關注

關注

38文章

4338瀏覽量

221654 -

eda

+關注

關注

71文章

2886瀏覽量

176450 -

Synopsys邏輯庫

+關注

關注

0文章

1瀏覽量

2678

原文標題:TSMC 28HPC+工藝邏輯庫改善PPA的六個方法

文章出處:【微信號:FPGA-EETrend,微信公眾號:FPGA開發圈】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

采用TSMC 28HPC / HPC + 工藝的Synopsys邏輯庫和領先的EDA工具完美解決系統級芯片(SoC)設計

采用TSMC 28HPC / HPC + 工藝的Synopsys邏輯庫和領先的EDA工具完美解決系統級芯片(SoC)設計

評論