高性能、高速互聯(lián)、更優(yōu)體驗等的追求推動了移動終端與物聯(lián)網(wǎng)市場的迅猛發(fā)展。

這些日益增長的要求反過來促使芯片在功/性能上和三維構(gòu)架上的集成度不斷提高,這就帶來了半導體工藝及技術(shù)的新需求與挑戰(zhàn)。尤其是芯片前道工藝尺寸縮減與后道封裝,正走向越來越精細化與復雜化。作為快速消費電子產(chǎn)品中的核心“大腦”的芯片,追求其成本的降低和良率的提升顯然成為驅(qū)動半導體產(chǎn)業(yè)工藝不斷改進演化的原動力。

誠如管理學大師彼得德魯克所說——能測量,始能改善。半導體產(chǎn)業(yè)前道后道工藝的持續(xù)改進也一直是建立在對每一個檢測節(jié)點的可靠可重復的測量基礎上的。無論是從Si到GaAs再到SiC等材料更新,還是工藝流程日新月異的突破,都會對工藝提出挑戰(zhàn),沖擊良率。因而,量測設備和儀器在此過程中越來越重要,實時、全方位的監(jiān)控對測量技術(shù)本身提出了更高的要求。

從前道三極管關(guān)鍵尺寸的精準測量到后道封裝中互聯(lián)導線的三維尺寸,從器件設計時預想的電學特征到實際生產(chǎn)出來后的電學性能,再到新材料新工藝運用造成的器件機械性能的變化等等都會直接影響到芯片的使用性能和可靠性,從而影響良率。

今天,以原子力顯微鏡技術(shù)、三維光學式輪廓技術(shù)和納米壓/劃痕技術(shù)等為代表的量測技術(shù)正在全球范圍內(nèi)每時每刻被廣泛使用,持續(xù)解決上述挑戰(zhàn)。不但直接使用在無塵室大規(guī)模產(chǎn)品的生產(chǎn)現(xiàn)場和研發(fā)中心以及失效分析實驗室,也被大量使用在大學、研究所等科研領域,用以開發(fā)更先進的材料與工藝。

前道工藝中高空間分辨的電學測量原子力顯微鏡技術(shù)

原子力顯微鏡技術(shù)作為當今世界上具有最高分辨率測量和成像的工具,在垂直方向低于埃級,水平方向為納米級。當使用特殊導電探針時,通過布魯克首創(chuàng)的掃描擴展電阻、掃描電容顯微鏡等模式,可以直接測量摻雜后載流子的極性與濃度分布梯度,用于離子注入或爐管、快速反應退火等工藝的精準監(jiān)控。而通過導電原子力顯微鏡則可以直接獲取伏安曲線,測量鎢柱是否良好接觸,用于物理氣相沉積時種子層和鎢柱填充等工藝的失效分析。

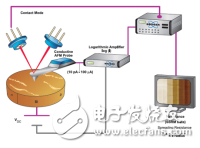

圖一 掃描擴展電阻顯微鏡

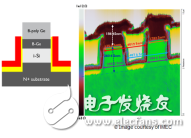

圖二 垂直異質(zhì)結(jié)隧穿場效應晶體管

圖三 CMOS影像傳感器結(jié)構(gòu)

圖一是掃描擴展電阻顯微鏡(SSRM)原理示意圖。圖二為SSRM在垂直異質(zhì)結(jié)TFET結(jié)構(gòu)斷面數(shù)據(jù),該技術(shù)優(yōu)異之處在于量程廣而精度高,通過顏色不同襯度直觀顯示出幾十至幾百納米的結(jié)構(gòu)細節(jié),右圖左側(cè)標尺定量出電阻數(shù)據(jù)。圖三通過SSRM顯示出CMOS影像傳感器中單顆像素點的載離子的二維分布高清圖像,而CMOS正是目前大量使用的手機攝像模組的核心單元。此外,布魯克原子力顯微鏡還具備掃描電容顯微鏡(SCM)、掃描微波阻抗顯微鏡(sMIM)等多種電學測量模塊,廣泛使用于半導體器件的結(jié)構(gòu)分析。

后道封裝工藝中快速三維尺寸精準測量白光干涉技術(shù)

后道封裝從有基片(substrate-based)的鍵合(WireBond)到倒裝(Flip Chip)發(fā)展到扇出式晶圓級封裝(Fan-Out Wafter Level Packaging),經(jīng)歷著不斷的技術(shù)與成本挑戰(zhàn)。但正如市場上一、二、三代半導體技術(shù)并存一樣,前述封裝工藝在不同應用場景的芯片封裝中都在使用。以下以全球封裝領先的安靠公司的SWIFTTM(Silicon Wafer Integrated Fan-Out Technology)為例,展示布魯克的白光干涉技術(shù)是如何在封裝工藝中實現(xiàn)快速可靠監(jiān)控的。

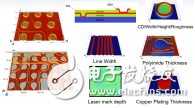

圖四SWIFT工藝流程

圖五 銅柱典型工藝監(jiān)控數(shù)據(jù)

圖六 PCB封裝工藝典型監(jiān)控數(shù)據(jù)

圖四是SWIFT工藝流程。圖五左側(cè)展示了RDL(Re-distributed layer)和UBM(Under bump metallization)經(jīng)白光干涉測得的三維形貌效果,線條分布、圖案高低一目了然,中間和右側(cè)選擇了局部圖案具體分析了銅柱(pillar)的高度、直徑、表面粗糙度等,線條的高寬,光刻膠的厚度,以及芯片封好后表面激光加工產(chǎn)品logo的圖案的最大深度(確保不損傷內(nèi)部芯片)。圖六左側(cè)是可以直接測量600x600mmPCB板(包含硬軟板,厚窄板)的白光干涉儀,右側(cè)是典型測試圖案,來確保工藝滿足要求(如目前窄板工藝線條線寬已經(jīng)可以達到7微米,其在線監(jiān)控要求已非常嚴苛)。

后道封裝工藝中物性測試與失效分析納米壓痕、劃痕技術(shù)

對于3D堆疊式封裝而言,各層器件間以及器件內(nèi)由于各種材料的物理性能尤其是熱膨脹性能不同,或者特定的幾何結(jié)構(gòu)(如硅穿孔,TSV)等會造成封裝時嚴重的形變和應力產(chǎn)生,對器件的可靠性與失效分析表明:薄膜自身、薄膜與基體、電路圖案與基板等的各種物性都是應該考察的關(guān)鍵因素。而納米壓痕、劃痕技術(shù)可以在微納米尺度上對材料局域的物理性能提供準確而定量可靠的測量數(shù)據(jù),為工藝模擬與監(jiān)控提供了途徑。

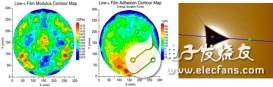

圖七 300mm晶圓上模量與結(jié)合力譜圖(左)和斷裂韌性測試圖

圖八 電鏡中觀測納米劃痕過程觀察與數(shù)據(jù)采集

圖九 填銅的TSV升溫后三維形貌(左)與微銅柱結(jié)合力測試

圖七左側(cè)是通過納米壓痕和劃痕技術(shù)對層間電介質(zhì)的low k材料在整張300mm硅片上測試的模量和結(jié)合力譜圖,右側(cè)是對薄膜材料斷裂韌性測試的典型結(jié)果(原位掃描探針顯微鏡圖)。圖八左側(cè)顯示了在電鏡中觀測納米劃痕從劃入薄膜(A)到薄膜開裂(B)至薄膜剝落(C),最終探頭劃入基體(D)的全過程,而右側(cè)的數(shù)據(jù)是實時采集的全過程正壓力、切向力與時間的關(guān)系,完美揭示此薄膜失效機制并定量給出膜基結(jié)合力。圖九左側(cè)顯示了TSV結(jié)構(gòu)填完銅后在400°C高溫下由于熱膨脹系數(shù)(CTE)不同,從Si孔中凸起的形貌,而右側(cè)是利用壓頭直接推動微銅柱(μ-bump)來考察其與底下保護層(passivation layer)的結(jié)合強度,這種測試均可得到可重復的定量數(shù)據(jù)。

-

芯片設計

+關(guān)注

關(guān)注

15文章

1061瀏覽量

55443 -

質(zhì)量管理

+關(guān)注

關(guān)注

1文章

108瀏覽量

13338

原文標題:芯片質(zhì)量工程師必讀指南

文章出處:【微信號:icbank,微信公眾號:icbank】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

硬件工程師手冊(全套)

不同時期的硬件工程師,最怕發(fā)生的事 #電子工程師 #硬件工程師 #內(nèi)容過于真實 #YXC晶振 #揚興科技

芯片封裝工藝集成工程師的必修課程指南

FPGA算法工程師、邏輯工程師、原型驗證工程師有什么區(qū)別?

芯片質(zhì)量工程師必讀指南

芯片質(zhì)量工程師必讀指南

評論